- 1面试经验|拿了8家大厂SSP offer_sspoffer

- 2scrapy-redis_scrapy-redis配置

- 3【论文阅读及代码实现】BiFormer: 具有双水平路由注意的视觉变压器

- 4如何评价cisp-pte证书?_cise-pte

- 5linux mips汇编指令集,MIPS汇编与指令

- 6springboot3使用自定义注解+Jackson优雅实现接口数据脱敏_springboot3 jackson

- 7PU学习相关知识

- 8读英语计算机书籍读后感,读英语小说的读后感(精选14篇)

- 9uni-app的开发环境_uniapp安装依赖

- 10【文章系列解读】AI绘图必读模型:Derambooth和Textual Inversion

vivado仿真

赞

踩

Verilog的代码编写完成了,代码是否正确,需要经过仿真的验证。

打开FreDivDou的工程,

仿真

点击Sources中的“+”,

Add Sources

选择添加仿真文件,点击“Next”,

Add or Create Simulation Sources

点击“Create File”,

Create Source File

File Type选择Verilog,File name填写仿真文件名称,点击OK,

Add or Create Simulation Sources

点击Finish,

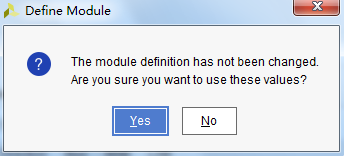

Define Module

点击OK,

Define Module

点击Yes,

仿真文件产生

成了仿真文件tb_Fre.v,双击tb_Fre(tb_Fre.v),

打开仿真文件

在tb_Fre.v中编写仿真代码,

moduletb_Fre(

);

reg clk_i;

reg rst_n_i;

wire div2_o;

wire div3_o;

wire div4_o;

wire dou2_o;

wire dou3_o;

FreDivDouttb( //调用FreDivDou.v

.clk_i(clk_i), //.后面的clk_i是FreDivDou.v中的端口名称,括号内的clk_i是仿

//真文件tb_Fre.v中定义的变量名称

.rst_n_i(rst_n_i),

.div2_o(div2_o),

.div3_o(div3_o),

.div4_o(div4_o),

.dou2_o(dou2_o),

.dou3_o(dou3_o)

);

//initial块从仿真0时刻开始执行,在整个仿真过程中只执行一次

initial begin

clk_i = 0;

rst_n_i = 0;

#1000;

rst_n_i = 'b1;

end

//产生一个周期为20ns的时钟

always #10 clk_i = ~clk_i;

endmodule

仿真代码编写完成后,保存该文件,

保存文件

点击PROJECT MANAGER——SIMULATION——Run Simulation,

Run Simulation

点击Run Behavior Simulation,

Run Behavioral Simulation

等待若干秒钟,

Simulation

点击仿真界面的最大化按钮,如上图所示,

Run All

点击上图中的Run All按钮,开始仿真,

仿真结果

数一数,你就会发现,假定clk_i是50M时钟,那么div2_o的时钟是50M/2=25M;div3_o的时钟是50M/3=16.67M;div4_o的时钟是50M/4=12.5M;dout2_o的时钟是50M*2=100M;dout3_o的时钟是50M*3=150M。

作者:学vivado的小鱼

链接:https://www.jianshu.com/p/57ebc6886e0a

来源:简书

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。