热门标签

热门文章

- 1《Python自然语言处理》第二章 习题解答 练习6

- 2YOLOv7改进:BoTNeT(Bottleneck Transformer)_yolov7使用botnet

- 3计算机毕业设计springboot农贸市场摊位出租系统k52bf9【附源码+数据库+部署+LW】_农贸菜市场租位管理系统的类图

- 4第一课:什么是树莓派_树莓派为啥叫树莓派

- 5InstructGPT高效实践——【DeepSpeed-Chat】源码详解(1/3):基本概念、数据集管理_deepspeed chat数据集

- 621.5k Star , AI 智能体项目OpenDevin:少写代码,多创造(附部署教程)_opendevin部署到windows

- 7go语言kafka入门_kafka-go

- 8【C语言】库函数—qsort

- 9Python的安装_python 阿里源

- 10高可靠性部署系列(3)--- ASG双机热备(HA)

当前位置: article > 正文

59-ARM与FPGA间RGMII通信电路设计

作者:菜鸟追梦旅行 | 2024-05-04 09:40:58

赞

踩

59-ARM与FPGA间RGMII通信电路设计

视频链接

ARM与FPGA间RGMII通信电路设计01_哔哩哔哩_bilibili

ARM与FPGA间RGMII通信电路设计

第2课:千兆以太网电路设计

第3课:万兆网电路设计

第49课:PCIE转网口电路设计

第50课:RGMII & SGMII & QGMII电路设计

1、以太网简介

1.1、以太网的概述

以太网接口电路主要由MAC(Media Access Control:媒体访问控制)控制器和物理层接口 PHY(Physical Layer,PHY)两大部分构成。

1.2、以太网接口介绍

以太网的通信离不开物理层PHY芯片的支持,以太网MAC和PHY之间有一个接口,常用的接口有MII、RMII、GMII、RGMII等。

在千兆以太网中,常用的接口为RGMII

| 简述 | 管脚 | 速率计算 | |

| RGMII | RGMII(Reduced GMII): RGMII是GMII的简化版,数据位宽为4位,在1000Mbps传输速率下,时钟频率为125Mhz,在时钟的上下沿同时采样数据。 在100Mbps和10Mbps通信速率下,为单个时钟沿采样。 | TXD[3:0] RXD[3:0] TX_EN RX_DV TX_CLK RX_CLK | Clock=125MHz, 数据位宽4bit(一个时钟周期里上升取TX\RX的0-3bit下降沿取TX\RX的4-7bit,所以其实是在一个时钟周期单读取了8bit数据) 1000Mbps=125MHz*8bit 100Mbps=25MHz*4bit 10Mbps=2.5MHz*4bit |

2、案例一:君正M300与FPGA间的RGMII通信设计

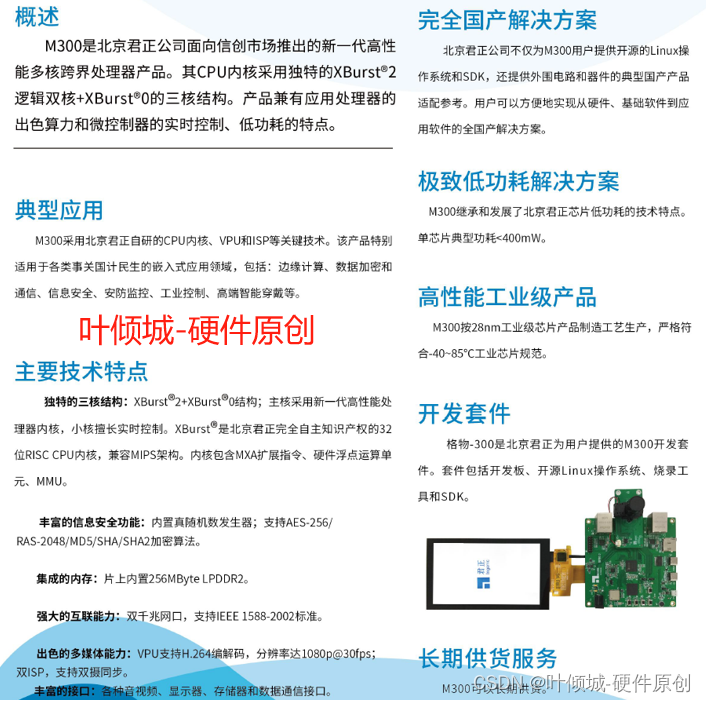

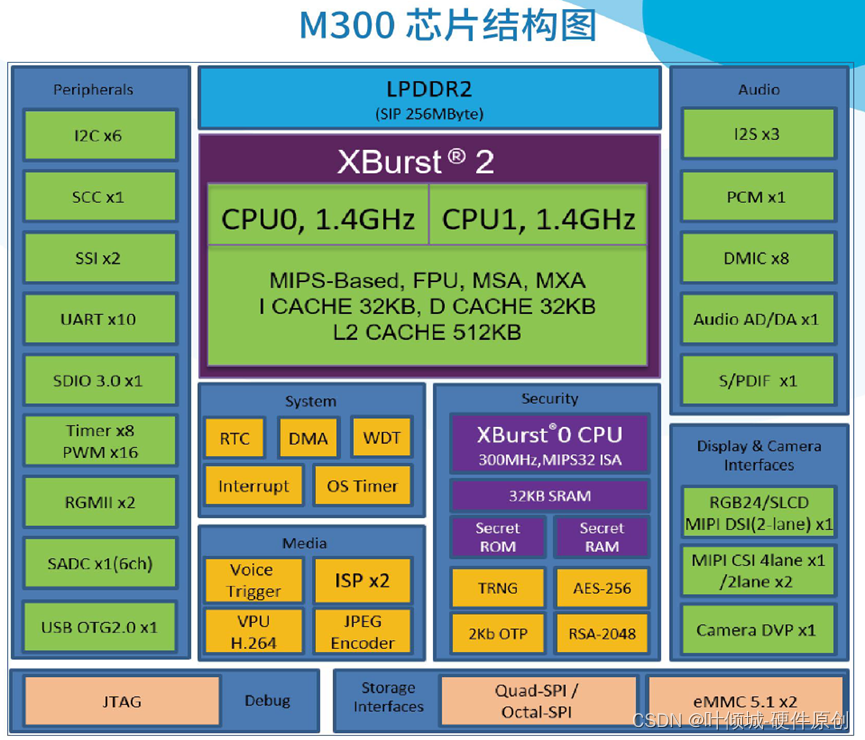

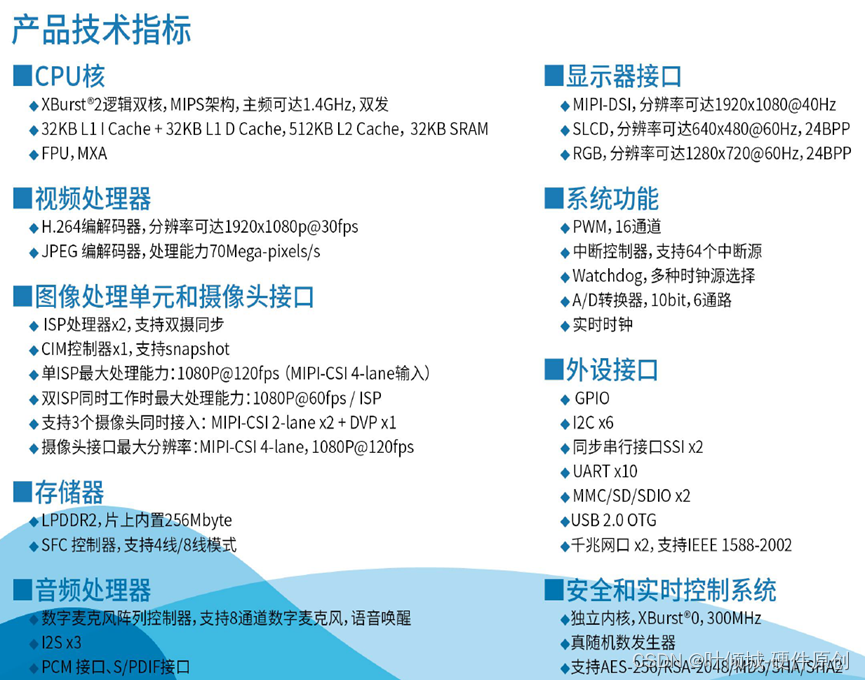

2.1、君正M300简介

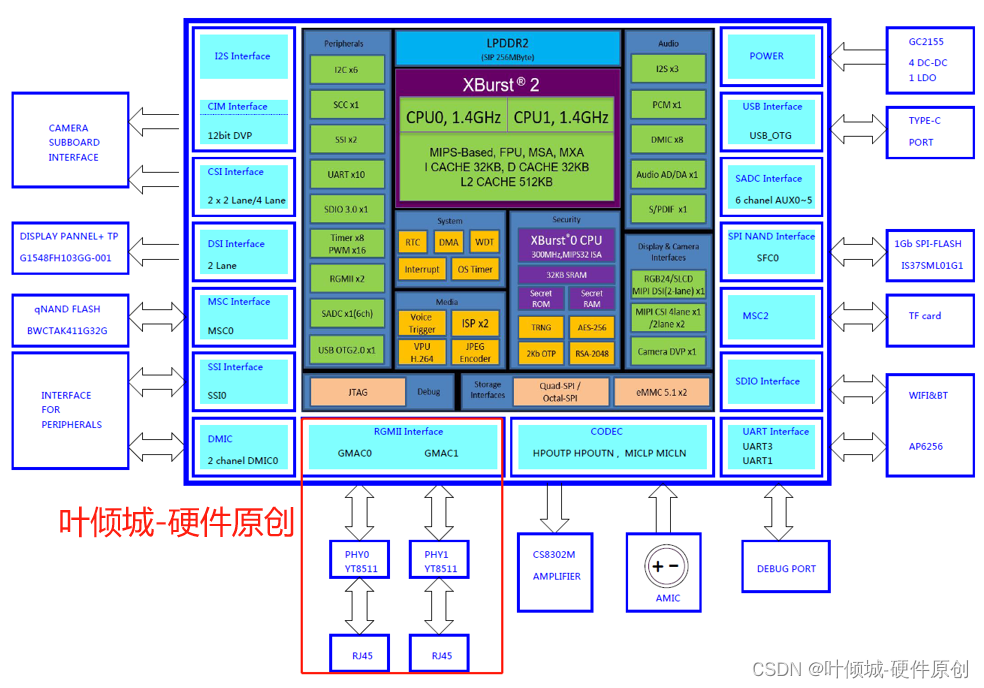

2.2、君正M300 与FPGA间RGMII通信电路设计

3、案例二:NXP IMX6Q与FPGA间的RGMII通信设计

3.1、IMX6Q简介

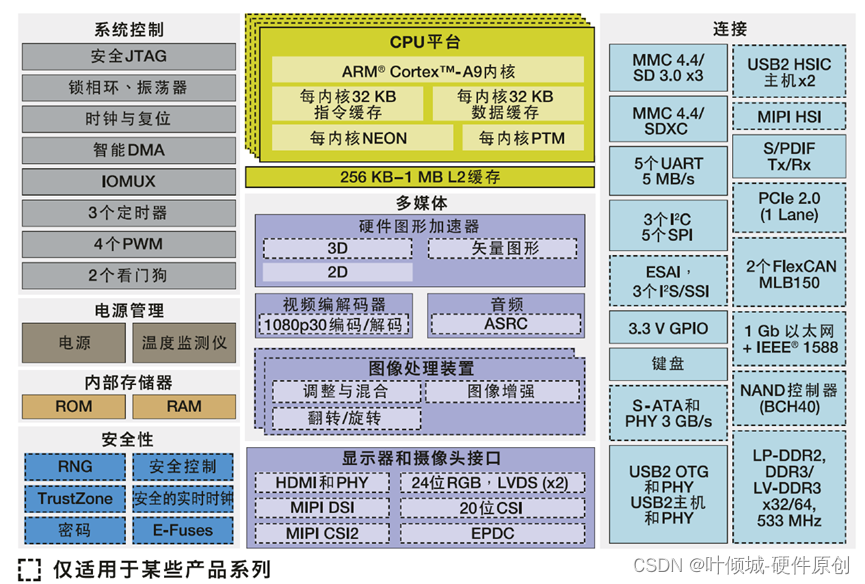

NXP I.MX6系列应用处理器基于ARM Cortex-A9架构,将节能高效的处理能力与尖端的2D、3D图形,以及高清视频功能相结合,将多媒体性能提升到全新的水平。

i.MX 6系列应用处理器框图

3.2、NXP IMX6Q与FPGA间RGMII通信电路设计

4、总结

详细内容参考视频讲解

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/菜鸟追梦旅行/article/detail/533857

推荐阅读

相关标签