热门标签

热门文章

- 1ICode国际青少年编程竞赛- Python-1级训练场-for循环入门_icode青少年编程重点代码

- 2已解决(三个问题)|neo4j Failed authentication attempt for ‘meter‘ from 127.0.0.1_py2neo.errors.clienterror: [security.unauthorized]

- 3SQL Server索引管理——索引创建建议和经验(二)_为什么在创建并管理普通索引的时候说关系产品不存在

- 4从制造到智造,安捷利的云数蝶变

- 5微软撤离中国市场?四大布局疑似“预备撤退”_微软退出中国

- 6Python数据分析与可视化(基础知识)

- 72024年最全软件测试学习书籍【附电子版】_软件测试的书籍,2024年最新软件测试面试题2024高级_软件测试有趣的书籍

- 8【GB28181】从一个开源平台入门到实践系列文章汇总(持续更新)_开源gb28181

- 9vscode使用_vscode ssh 密码

- 10Elasticsearch 面试题及参考答案:深入解析与实战应用

当前位置: article > 正文

FPGA时序约束(一)

作者:菜鸟追梦旅行 | 2024-05-31 15:49:32

赞

踩

fpga时序约束

1. 时序约束理论篇

- 建立和保持时间

- 时序路径

- 时序模型

2.I/O管脚约束

- 管脚约束

- 延迟约束

3.时钟周期约束

4.两种时序例外

- 多周期路径

- 伪路径

5.xdc约束优先等级

- 建立和保持时间

建立时间:在clk上升沿到来之前,保持稳定(准备好开始)

保持时间:在clk上升沿到来之后,保持稳定(别动!)

时序路径

典型的额时需路径有4种,如下图所示:其中标记1和3是片间路径,2和4是片内路径。

这几类中,我们关注比较多的是2的同步时序逻辑,也就是FPGA内部的时序逻辑。

这几类中,我们关注比较多的是2的同步时序逻辑,也就是FPGA内部的时序逻辑。

时序模型

一个完整的时序路径包括:源时钟路径,数据路径,目的时钟路径,也可以表示为触发器+组合逻辑+触发器的模型。

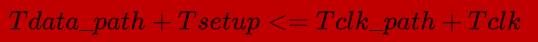

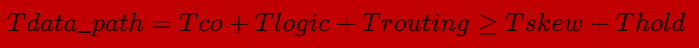

面试常考的两条公式(要理解):

面试常考的两条公式(要理解):

2.I/O管脚约束

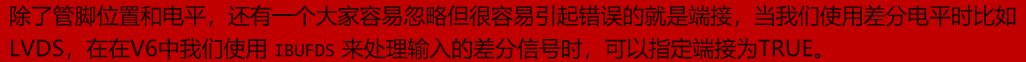

管脚约束就是管脚分配,我们要指定管脚两个属性:PACKAGE_PIN和IOSTANDARD(管脚位置和管脚对应的电平标准)。

如:

延迟约束:

延迟约束用的是set_input_delay和set_output_delay,分别用于input端和ouput端,其时钟源可以是时钟输入管脚,也可以是虚拟时钟。但是需要注意的是,这两个约束并不是起延迟作用。

3.时钟周期约束:顾名思义,是对时钟的周期进行约束。

常用的约束指令有:

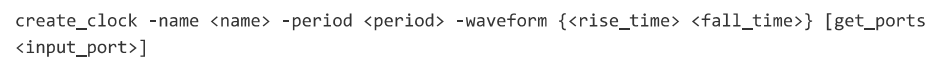

1>create_clock。使用方法如下:

这里的时钟必须是主时钟primary clock,主时钟通常有两种情形:一种是时钟由外部时钟源提供,通过时钟引脚进入FPGA,该时钟引脚绑定的时钟为主时钟:另一种是高速收发器(GT)的时钟RXOUTCLK或TXOUTCLK。对于7系列FPGA,需要对GT的这两个时钟手工约束:对于UltraScale FPGA,只需对GT的输入时钟约束即可,Vivado会自动对这两个时钟约束。

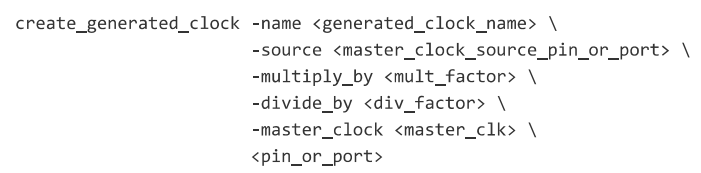

2>create_generated_clock,其使用方法为:

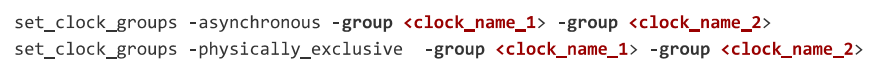

3>set_clock_groups使用方法为:

这个约束常用的方法有三种。

4>创建虚拟时钟

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/菜鸟追梦旅行/article/detail/653064

推荐阅读

相关标签