热门标签

热门文章

- 1设置文件上传限制(解除限制)_gozero如何修改文件上传限制

- 2educoder答案-Python编程基础-第二阶段 数据类型-字符串处理-太原理工大学_获取待处理的源字符串

- 3决策树的实现及可视化方法总结_决策树可视化实现

- 4SPI读写FLASH 原理+完整代码_spiflash

- 5centos7-dmhs同步kafka搭建部署(保姆级)_kafka dmhs

- 6MySQL问题:2002 - Can‘t connect to server on ‘localhost‘(10061)【已解决】_2002cant connect to server on

- 7Flink高频面试题( 精简 )_100个flink高频面试题系列

- 8【EI会议征稿通知】第四届人工智能,大数据与算法国际学术会议 (CAIBDA 2024)_caibda2022

- 9Python matplotlib画气温变化的折线图_python在多个坐标系绘制沈阳和广州4月份温度变化折线图

- 10GCN图神经网络和LSTM的介绍和使用场景 中英文_gcn lstm

当前位置: article > 正文

vivado 设置 VIO 核以执行测量、查看 VIO 核状态_vivado vio

作者:菜鸟追梦旅行 | 2024-06-11 18:35:12

赞

踩

vivado vio

设置

VIO

核以执行测量

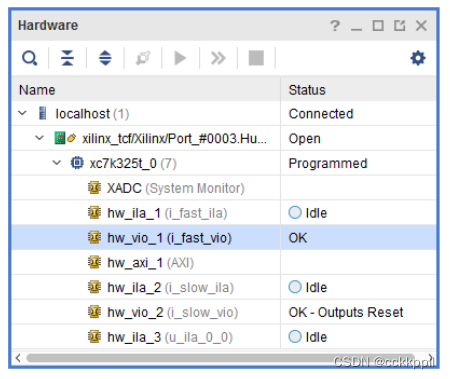

您添加到自己的设计中的

VIO

核会显示在“硬件

(Hardware)

”窗口中的目标器件下。如果未显示这些

VIO

核

,

请右键

单击器件并选择“

Refresh Hardware

”。这样将重新扫描

FPGA

或

ACAP

并刷新“

Hardware

”窗口。

注释

:

如果编程和

/

或刷新

FPGA

或

ACAP

后仍未显示

VIO

核

,

请检查并确保已使用正确的

.pdi

文件完成器件编程

,

并确认已实现的设计包含

VIO

核。此外

,

还请检查并确认有相应的

.ltx

探针文件

(

与

.bit

文件相匹配

)

与该器件

关联。

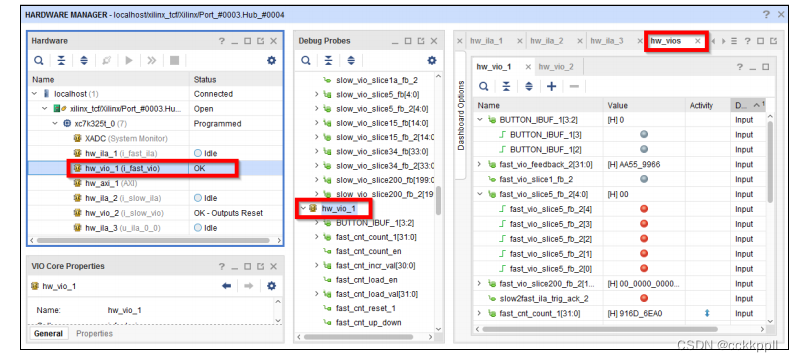

单击

VIO

核

(

下图中名为

hw_vio_1

的核

),

以在“

VIO

核属性

(VIO Core Properties)

”窗口中查看其属性。选中

VIO

核后

,

还应在“调试探针

(Debug Probes)

”窗口以及

Vivado IDE

工作空间中对应的“

VIO

仪表板

(VIO Dashboard)

”中

看到对应于此

VIO

核的探针。

VIO

核可能会与

Vivado IDE

不同步。请参阅“查看

VIO

核状态”

,

以获取有关如何解释

VIO

状态指示的更多信息。

VIO

核根据基于对象属性的置位

/

落实和刷新

/

获取模型来操作

:

• 要读取

VIO

输入探针值

,

请首先刷新含

VIO

核数值的

hw_vio

对象。获取对应

hw_probe

对象的属性值

,

以观察输

入探针值。请参阅“与

VIO

核输入探针进行交互”部分

,

以获取更多信息。

• 要编写

VIO

输出探针值

,

请首先在

hw_probe

对象上获取期望的值作为属性。随后

,

这些属性值将落实到硬件中的

VIO

核

,

以将这些值写入核的输出探针端口。请参阅“与

VIO

核输入探针进行交互”部分

,

以获取更多信息。

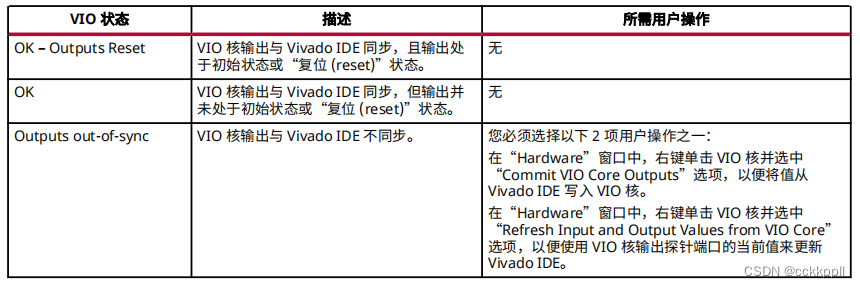

查看

VIO

核状态

VIO

核可包含

0

或多个输入探针以及

0

或多个输出探针

(

请注意

,

VIO

核必须包含至少

1

个输入或输出探针

)

。

“

Hardware

”窗口中所示

VIO

核状态用于表示

VIO

核输出探针的当前状态。下表中描述了可能的状态值以及您需要采

取的任何操作。

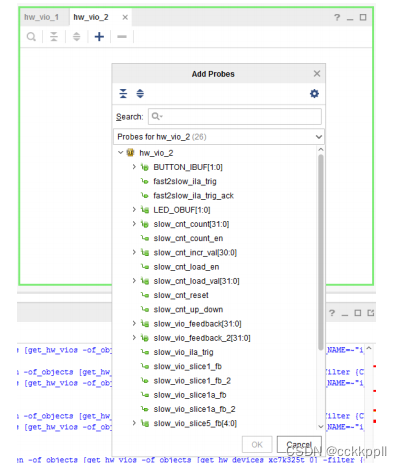

在“调试探针

(Debug Probes)

”窗口中查看

VIO

核

“

VIO

仪表板

(VIO Dashboard)

”窗口中的“

+

”按钮用于查看、添加和删除属于

VIO

核的调试探针。

使用

VIO

仪表板

VIO

默认仪表板初始为空

,

您可向其中添加

VIO

探针

,

如下图显示。

VIO

仪表板是给定

VIO

核相关的所有状态和控制信息的集中显示位置。刷新硬件器件并首次检测到

VIO

核时

,

将自动

打开该核的

VIO

仪表板。如果需要手动打开或重新打开此仪表板

,

请在“硬件

(Hardware)

”窗口或“调试探针

(Debug

Probes)

”窗口中右键单击此

VIO

核对象

,

然后单击“

Open Dashboard

”。

与

VIO

核输入探针进行交互

VIO

核输入探针用于从实际硬件的

FPGA

或

ACAP

内运行的设计中读取相应的值。

VIO

输入探针通常用作为待测设计

的状态指示器。

VIO

调试探针需手动添加到

VIO

仪表板的“

VIO

探针

(VIO Probes)

”窗口中。请参阅“在‘调试探针

(Debug Probes)

’窗口中查看

VIO

核”章节

,

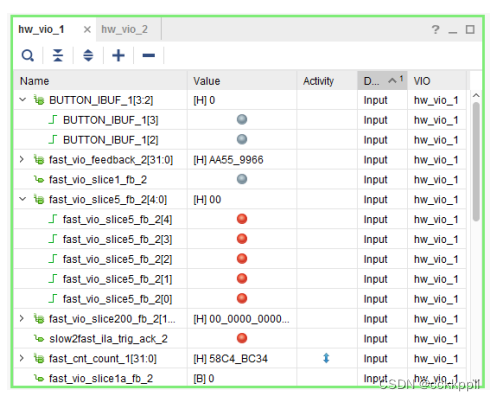

以了解具体方法。下图中显示了

VIO

仪表板的“

VIO Probes

”窗口中的

VIO

输入探针示例。

使用

VIO

核视图读取

VIO

输入

VIO

输入探针可使用“

VIO

仪表板

(VIO Dashboard)

”窗口的“

VIO

探针

(VIO Probes)

”窗口来查看。每项输入在表中

均独立成行以供查看。

VIO

输入探针的值显示在表中的“值

(Value)

”列中

(

请参阅“与

VIO

核输入探针进行交

互”

)

。

VIO

核输入值将根据

VIO

核的刷新率值定期更新。您可通过更改“

VIO

属性

(VIO Properties)

”窗口中的“刷

新率

(Refresh Rate (ms))

”或者通过运行以下

Tcl

命令来设置刷新率

:

set_property CORE_REFRESH_RATE_MS 1000 [get_hw_vios hw_vio_1]

注释

:

将刷新率设为

0

会导致

VIO

核停止自动刷新。另请注意

,

刷新率值过低可能导致

Vivado IDE

迟滞。赛灵思建议

将刷新率设为不低于

500 ms

。

如果要手动读取

VIO

输入探针值

,

可使用

Tcl

命令。例如

,

如果要刷新并获取

VIO

核

hw_vio_1

的输入探针值

(

名为

BUTTON_IBUF

),

请运行以下

Tcl

命令

:

refresh_hw_vio [get_hw_vios {hw_vio_1}]

get_property INPUT_VALUE [get_hw_probes BUTTON_IBUF]

相关信息

与

VIO

核输入探针进行交互

设置

VIO

输入显示类型和基数

VIO

输入探针的显示类型可通过如下方式进行设置

:

在“

VIO

仪表板

(VIO Dashboard)

”窗口的“

VIO

探针

(VIO

Probes)

”窗口中

,

右键单击

VIO

输入探针

,

并选择

:

• “

Text

”

,

用于将输入显示为文本字段。这是对应

VIO

输入探针矢量

(

位宽大于

1

)

的唯一显示类型。

• “

LED

”

,

用于将输入显示为发光二极管

(LED)

的图形表示法。此显示类型仅适用于

VIO

输入探针标量以及

VIO

输

入探针矢量的个别元素。您可将高低值设置为以下

4

种颜色中的任何颜色

:

○

灰

(

熄灭

)

○

红

○

绿

○

蓝

当

VIO

输入探针的显示类型设置为“

Text

”时

,

您可通过如下方式更改基数

:

在“

VIO Dashboard

”窗口的“

VIO

Probes

”窗口中

,

右键单击

VIO

输入探针

,

并选择

:

• “

Radix > Binary

”

,

以将基数更改为二进制。

• “

Radix > Octal

”

,

以将基数更改为八进制。

• “

Radix > Hex

”

,

以将基数更改为十六进制。

• “

Radix > Unsigned

”

,

以将基数更改为无符号十进制。

• “

Radix > Signed

”

,

以将基数更改为有符号十进制。

您还可使用

Tcl

命令来设置

VIO

输入探针的基数。例如

,

要更改名为“

BUTTON_IBUF

”的

VIO

输入探针的基数

,

请

运行以下

Tcl

命令

:

set_property INPUT_VALUE_RADIX HEX [get_hw_probes BUTTON_IBUF]

观察和控制

VIO

输入活动

除了从

VIO

输入探针读取值外

,

您还可以监控

VIO

输入探针的活动。活动检测器可用于指示

Vivado IDE

定期更新期间

VIO

输入值何时发生改变。

VIO

输入探针活动值在“

VIO

仪表板

(VIO Dashboard)

”窗口的“

VIO

探针

(VIO Probes)

”窗口的活动列中显示为箭

头

:

• 向上箭头表示在活动持续期间

,

输入探针值已从

0

转变为

1

。

• 向下箭头表示在活动持续期间

,

输入探针值已从

1

转变为

0

。

• 双向箭头表示在活动持续期间

,

输入探针值已至少一次从

1

转变为

0

并从

0

转变为

1

。

如需控制输入活动状态显示的持续时间

,

请在“

VIO Dashboard

”窗口的“

VIO Probes

”窗口中右键单击

VIO

输入探

针并选择

:

• “

Activity Persistence > Infinite

”

,

此项用于累积并保留活动值

,

直至复位。

• “

Activity Persistence > Long (80 samples)

”

,

此项用于在较长的时间段内累积并保留活动。

• “

Activity Persistence > Short (8 samples)

”

,

此项用于在较短的时间段内累积并保留活动。

您还可使用

Tcl

命令来设置活动持续状态。例如

,

要将名为

BUTTON_IBUF

的

VIO

输入探针上的活动持续时间更改为

较长的时间段

,

请运行以下

Tcl

命令

:

set_property ACTIVITY_PERSISTENCE LONG [get_hw_probes BUTTON_IBUF]

要将任一给定核的所有输入探针的活动复位

,

请在“

Hardware

”窗口中右键单击

VIO

核

,

然后选择“

Reset All Input

Activity

”。您也可以通过运行以下

Tcl

命令来执行此操作

:

reset_hw_vio_activity [get_hw_vios {hw_vio_1}]

提示

:

要更改任一

VIO

输入探针矢量的多个标量成员的类型、基数和

/

或活动持续时间

,

请右键单击整个探针或

者该探针的多个成员

,

然后从弹出菜单中进行选择。菜单选项适用于选中的所有探针标量。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/菜鸟追梦旅行/article/detail/704330

推荐阅读

相关标签