- 1scrapy框架-反爬虫与绕过方法+setting动态配置

- 2浅谈单元测试和JUnit4使用_还有人在用 junit4吗

- 3开源新纪元:ChatTTS——引领对话式文本转语音的新潮流_chattts特点

- 4pnpm安装成功但不能用_pnpm 安装没效果

- 5【Mysql】utf8与utf8mb4区别,utf8mb4_bin、utf8mb4_general_ci、utf8mb4_unicode_ci区别

- 6python2.7是什么_python2.7是什么

- 7PG302 QDMA Subsystem for PCI Express v4.0 Ch.2 Overview

- 8AIGC总体相似度是什么意思_aigc相似度

- 9记录docker-compose遇到的坑_dockercompose keyerror: 'containerconfig

- 10unity入门教程(非常详细)从零基础入门到精通,看完这一篇就够了_unity完全自学教程

7 Series FPGAs Integrated Block for PCI Express IP核 Advanced模式配置详解(一)_pcie integrated block for pci express

赞

踩

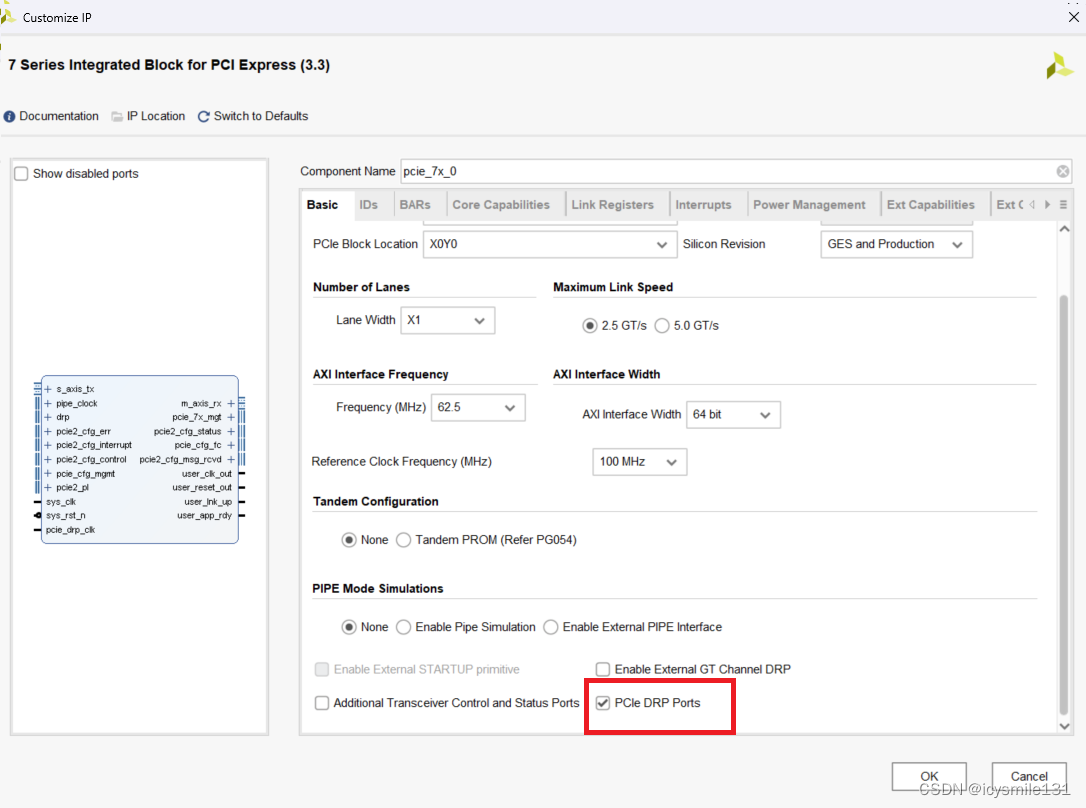

"7 Series FPGAs Integrated Block for PCI Express IP核" 是Xilinx公司7系列FPGA中集成的PCI Express (PCIe) IP核模块。这个IP核模块是一个可扩展的、高带宽的、可靠的串行互联构建块,用于与Xilinx的Zynq®-7000 SoC和7系列FPGA配合使用。

advanced 模式提供了更多配置选项、更复杂功能和更高级的设置。

1 Basic选项页

7 Series FPGAs Integrated Block for PCI Express IP核 的Advanced模式基本参数与Base模式相似,但增加了PCIe DRP Ports参数。

勾选这个选项会为PCIe Hard Block生成DRP(Dynamic Reconfiguration Ports)端口,这允许您对PCIe Hard Block的属性进行动态控制。这种设置可以用于执行高级调试。

DRP(动态重构端口)是一种机制,允许在运行时对PCIe IP核进行配置和修改。这对于高级调试和特定的系统需求非常有用,因为它允许开发者在不重新加载整个系统的情况下调整PCIe IP核的行为。

2 IDs(Identifiers) 选项页

参数设置同Basic模式。详见上一篇博文《7 Series FPGAs Integrated Block for PCI Express IP核基本模式配置详解》。

3 BARS(Base Address Registers)

参数设置同Basic模式。

4 Core Capacities

在Advanced模式下显示的Core Capabilities参数与Basic模式中的参数类似,但会添加一些额外的参数。

(1)Device Capabilities Register(设备能力寄存器)

该包含了一系列用于描述设备能力的字段。这些字段定义了设备如何响应PCIe事务,包括如何处理不同的数据格式、请求和电源管理状态。

-

Extended Tag Field

指示设备作为Requester(请求者)时Tag字段支持的最大大小。当选中时,表示支持8位Tag字段;当未选中时,表示支持5位Tag字段。 -

Extended Tag Default

当这个字段被选中时,指示Device Control寄存器的第8位默认设置为1,以支持Extended Tag Enable Default ECN(扩展标签启用默认扩展能力通知)。

3. Phantom Functions

指示设备是否支持使用未声明的功能号(Phantom Functions)来扩展由逻辑上组合未声明的 功能号和Tag标识符所允许的最大未完成事务数量。这个字段指示Requester ID中功能号部分 的最高位数与Tag标识符进行逻辑组合的数量。

4. Acceptable L0s Latency 和 Acceptable L1 Latency

这两个字段分别指示Endpoint(端点)可以承受的由于从L0s状态过渡到L0状态以及从L1状 态过渡到L0状态而产生的可接受的总延迟。

(2)PCIe 2.1 Specific

- UR Atomic:

- 如果选中,该IP核将自动对Atomic Operation请求(原子操作请求)以Unsupported Request(不支持的请求)进行响应。如果未选中,该IP核将Atomic Operations TLPs(事务层数据包)传递给用户。

- 32-bit/64-bit AtomicOp Completer Support:

- 这些字段指示设备是否支持32位或64位的原子操作完成器。

- 128-bit CAS Completer Support:

- 指示设备是否支持128位的Compare And Swap(比较并交换)完成器。

- TPH Completer Supported:

- 指示设备对TPH(Traffic Priority and Hierarchy)完成器的支持级别。TPH是PCIe中用于支持QoS(服务质量)的一种机制。

5 Link Registers(链路寄存器)

仅在Advanced模式下可用,提供有关PCIe链路状态、配置和能力的信息。用于监视和控制PCIe链路的各个方面,如链路带宽、链路训练状态、错误计数等。

(1)Link Capabilities Register(链路能力寄存器)

- Supported Link Speed:指示给定的PCI Express链路支持的链路速度。这个值在“Basic”选项卡中设置,并且不可编辑。

- Maximum Link Width:这个值设置为“Basic”选项卡中指定的初始通道宽度,并且不可编辑。

- ASPM Optionality:当选中时,此字段使ASPM(Active State Power Management,活动状态电源管理)成为可选的。ASPM是一种电源管理机制,用于在PCIe设备处于D0状态(活动状态)时,将链路置于低功耗状态。

- DLL Link Active Reporting Capability:指示数据链路控制和管理状态机的DL_Active状态的报告能力。

- Link Capabilities Register:显示发送到核心的Link Capabilities寄存器的值,并且不可编辑。

(2)Link Control Register(链路控制寄存器)

1. Hardware Autonomous Speed Disable:当选中时,此字段禁止硬件出于除尝试通过降低 链路速度来纠正不可靠的链路操作之外的设备特定原因来更改链路速度。

2. Read Completion Boundary:指示Root Port的读完成边界。

3. Target Link Speed:设置链路操作速度的上限。这用于设置目标Compliance Mode速度。 如果链路速度设置为5.0 Gb/s,则可以编辑此值。

4. Compliance De-emphasis:当链路以5.0 Gb/s运行时,为Upstream组件设置去加重级 别。此功能不可编辑。

5. Link Control Register 1 和 Link Control Register 2:分别显示发送到核心的Link Control Register 1和Link Control 2 Register的值,并且不可编辑。

(3)Link Status Register(链路状态寄存器)

Enable Slot Clock Configuration:该字段指示Endpoint是否使用连接器上提供的平台提供的物理参考时钟。如果Endpoint使用独立的参考时钟,则必须清除此字段。

6 Configuration Register (Only in Root Port Configuration)

当Root Port配置被选中,且处于高级模式时,配置寄存器页面是可用的。

(1)Root Capabilities Register(根能力寄存器)

- CRS Software Visibility:指示Root Port将CRs(配置请求重试状态)返回给软件的能力。当设置时,表示Root Port可以将配置请求重试状态(CRS)的完成状态返回给软件。

- Root Capabilities Register:指定设备的根能力寄存器。

(2)Slot Control Capabilities Register(插槽控制能力寄存器)

- Attention Button Present:指示是否实现了Attention Button。当设置时,表示在此插槽的底盘上实现了Attention Button。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。

- Attention Indicator Present:指示是否实现了Attention Indicator。当设置时,表示在此插槽的底盘上实现了Attention Indicator。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。

-

Power Controller Present:指示是否实现了电源控制器。当设置时,表示为此插槽实现了可软件编程的电源控制器。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。

-

Power Indicator Present:指示是否实现了电源指示灯。当设置时,表示在此插槽的底盘上为此插槽实现了电源指示灯。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。

-

Hot-Plug Surprise:当设置时,表示此插槽中的适配器可能会在系统没有任何预先通知的情况下被移除。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。

-

Hot-Plug Capable:当设置时,表示此插槽支持热插拔操作。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。在Vivado IDE中的复选框只是声明了这个能力,但它不会执行任何操作。您需要使用卡上的存在信号(presence signal),将其路由到FPGA的输入,并使用该输入作为存在检测,并通过管理接口写入来设置该位。

-

MRL Sensor Present:指示该插槽在机箱上是否实现了MRL(Manually operated Retention Latch,手动操作保持锁)传感器。当设置时,表示为此插槽在机箱上实现了MRL传感器。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。

- Electromechanical Interlock Present:指示该插槽在机箱上是否实现了电子机械互锁(Electromechanical Interlock)。当设置时,表示为此插槽在机箱上实现了电子机械互锁。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。

- No Command Completed Support:指示当热插拔控制器完成一个命令时,插槽是否不生成软件通知。当设置时,表示插槽在热插拔控制器完成命令时不会生成软件通知。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。

- Slot Power Limit Value:指定了供应给插槽的功率上限值,该值需要与“Slot Power Limit Scale”值结合使用。通过这个选项,您可以为PCIe插槽设置功率限制,以保护系统免受潜在的电源过载问题。当“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时,此选项被禁用。此功能仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。

- Slot Power Limit Scale:指定用于插槽功率限制值的比例尺。这个选项在“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时会被禁用。它仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。通过这个设置,您可以确定“Slot Power Limit Value”是以何种单位(如瓦特、千瓦等)来指定的。

- Physical Slot Number:指定与此端口关联的物理插槽编号。该字段必须由硬件初始化为一个值,该值在机箱内是唯一的,无论插槽的规格尺寸如何。这个选项在“Device_Port_Type”不是“PCI Express Root Complex的Root Port”时会被禁用。它仅在“Core Capabilities”选项卡中选择了“Slot Implemented”参数时才启用。通过设置这个值,系统可以识别和管理机箱内的每一个插槽。

- Slot Capabilities Register:指定设备的插槽能力寄存器。这个寄存器通常包含有关插槽特性的信息,例如它是否支持热插拔、是否支持电源管理等。这些能力信息对于操作系统和驱动程序来说很重要,因为它们需要知道如何与插槽及其上的设备进行交互。

这些配置项提供了关于PCIe插槽功能和限制的重要信息,使系统能够正确地管理和使用这些插槽。它们通常在硬件初始化或配置阶段进行设置,以确保系统的稳定性和兼容性。