热门标签

热门文章

- 1Spring Security认证流程分_springsecurity认证流程

- 2餐饮食堂安全守护者:可燃气体报警器故障处理与检测要点解析

- 3CAP框架异常处理、实现分布式事务及其它用法_cap标记为异常

- 4学“狂飙”的网络安全,做最强盛的打工人!!

- 5版本匹配指南:PyTorch版本、Python 版本和Torchtext版本的对应关系_pytorch 2.2.2对应torchtext

- 6(附源码)springboot基于java的超市购物管理系统 毕业设计 271611_java商品管理系统绪论

- 7微信账户体系科普:什么是UnionId、OpenId与wxopenid?_openid unionid

- 8JDK8之Lambda表达式_jdk8 lamada 表达式

- 9Spring Boot2.X(一)使用Spring Cache + Redis 实现缓存_springcache整合redis的目的

- 10如何CSS-画0.5px的线,解决IOS移动端兼容性问题_windicss border 0.5px 苹果手机不显示

当前位置: article > 正文

华科计算机组成原理 单总线CPU设计 定长&变长&现代时序&中断 指令周期3级时序 (Logisim&Educoder)_硬布线控制器组合逻辑单元logisim

作者:运维做开发 | 2024-06-20 23:50:29

赞

踩

硬布线控制器组合逻辑单元logisim

大家好,我是小黄鸭,又来更新了,应小伙伴的需要,定长、现代时序、中断、实验也过了。

2022/1/4大家好,我是小黄鸭,由于21年下半年在考研,因此很多消息没有回复,现在大家有问题可以来私聊我

- 1

- 2

实验所用的软件资源/测试电路也全部开放,地址在MOOC中国大学为:https://www.icourse163.org/learn/HUST-1205809816#/learn/announce

附带实验测试,地址在Educode上为:https://www.educoder.net/shixuns/ckff6yv9/challenges

把CPU不同指令的工作流程和时序转换的原理弄明白,就可以做出来了

整体框架

- 实验目的:该实验是帮助学生理解定长指令周期三级时序系统的设计,能够利用该时序构造硬布线控制器,支持5条典型的MIPS指令在单总线CPU上运行,最终CPU能够运行内存冒泡程序。实验完成后,最终的效果就是下面的这两幅图,分别是:单总线CPU和硬布线控制器部分。(只有RST为一条蓝色的线,其余都为正常)

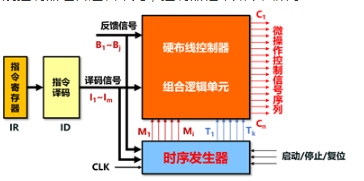

- 三级时序硬布线控制器基本架构,主要包括三个部分:指令译码信号、组合逻辑线路、时序发生器,这也正是整个实验需要实现的部分。

- 实验文件为MipsOnBusCpu-3.circ,其中单总线数据通路已经设计好了,主要设计部分为硬布线控制器,具体如下。

接下来以定长指令周期的CPU设计为例,给大家讲一下原理。

MIPS指令译码器设计

- 该实验较为简单,主要是根据指令字的OP和Func字段,利用比较器,对5条基本指令进行译码。

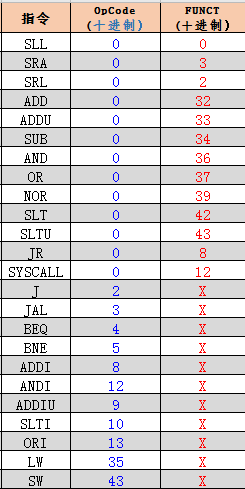

- 主要的MIPS指令OP和Func字段如下。

- 电路图如下

时序发生器FSM设计

- 时序发生器内部框图如下图所示,主要包括状态寄存器,状态机组合逻辑,输出函数组合逻辑三部分。其中状态机负责现态与次态的转换,输出函数根据当前状态生成状态周期电位和节拍周期电位。

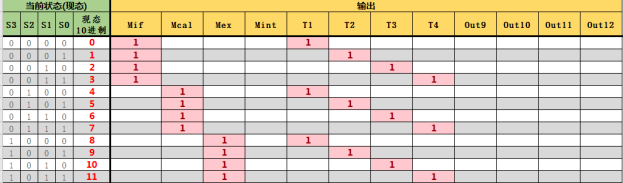

- 这个实验为定长指令周期,因此所有MIPS指令有需要3个时钟周期,每个机器周期4个时钟节拍,一共需要12个状态,状态图如下。

- 根据状态图在相应的excel表中(文件中标号位1的表格)填写,即可在logisim中自动生成电路。这里就详细给大家讲一下Excel表格和自生成电路的应用。

- 首先观察表格,需要输入的部分都为红色的数字部分,分别现态(10进制),输入信号,次态(10进制),灰色部分为自动生成部分。

- 由于为定长指令周期,因此每一种MIPS指令都需要执行12个周期,所以这里的次态与输入信号无关(不填或者填X),最终如下。

- 然后点击下方的自动生成表格,右下方的蓝色部分就是每一个输出的逻辑表达式。然后打开logisim中该实验的分析电路(项目->分析电路),将逻辑表达式复制后,并选中,最后生成电路。

- 生成的电路图如下

- 首先观察表格,需要输入的部分都为红色的数字部分,分别现态(10进制),输入信号,次态(10进制),灰色部分为自动生成部分。

时序发生器输出函数设计

上一关已经设计出了时序发生器FSM,了解了时序发生器的基本原理,这里只需要根据状态 转换图,进一步对输入输出进行设计,在Excel中填写相应表格,自动生成电路。如下。然后在Logisim中自生成电路。

硬布线控制器组合逻辑单元

- 硬布线控制器组合逻辑单元的基本框架如下

- 由于所有的微操作控制信号,都是反馈信号,指令译码信号,状态周期电位和节拍电位的组合逻辑函数根据各MIPS指令的数据流图,在相应的Excel中填写。

- 然后在logisim中自生成电路即可。

硬布线控制器设计

根据第2关中,硬布线控制器的总体框架,利用状态寄存器和时钟信号,将设计好的FSM状 态机和输出函数组合逻辑进行连接,从而实现硬布线控制器的整个功能。

单总线CPU设计

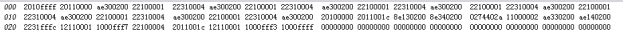

在前面硬布线控制器设计完成的基础上,在单总线CPU中,将sort-5中的指令复制到RAM 中,进行仿真。最终实现降序排列。

CPU性能分析与改进方法

传统三级时序执行慢,构成较为简单。其中定长指令周期的机器数和节拍数固定,机器数为3个机器周期,节拍数位4个节拍。这种方式对大多数指令都存在着时钟节拍的浪费而采用变长指令周期相对灵活,机器周期数和节拍数都可根据具体需要进行变化。这样就减少了不必要的浪费。

目前已完成实验

- 定长&变长(不放图了)

- 现代时序

- 现代时序+中断

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/运维做开发/article/detail/741281

推荐阅读

相关标签