热门标签

热门文章

- 1Mac本地安装部署Stable diffusion最全教程,AI绘画无痛入门指南_stable diffusion mac版

- 2git已经被使用的私钥公钥如何在其他电脑复用_两台电脑共用git 公钥

- 3鸿蒙购物系统——首页、分类、购物车、我的_鸿蒙购物界面

- 4AI机器人系统如何对接公众号_微信智能客服机器人 如何连接到公众号

- 5【Linux--多线程同步与互斥】_linux 多线程编程同步和互斥

- 6unity打包或者导出Android项目error sdk platform tools version_failed to extract android sdk platform version fro

- 7Studio One 6.6.2中文破解版+Studio One 6激活安装激活指南

- 8【漏洞通知】Apache Shiro又爆认证绕过漏洞CVE-2023-34478,漏洞等级:高危

- 9YOLOV5 -TensorRT linux平台实践_tensorrt exec

- 10大数据学习(二),hadoop集群重要节点概述以及HDFS文件系统的原理_hadoop集群节点

当前位置: article > 正文

呼吸灯——FPGA_fpga呼吸灯

作者:酷酷是懒虫 | 2024-07-05 22:50:07

赞

踩

fpga呼吸灯

前言

环境:

1、Quartus18.0

2、vscode

3、板子型号:EP4CE6F17C8

要求:

将四个LED灯实现循环从亮到灭、灭到亮的过程。下面我使用了两种方法供大家阅读。

一、呼吸灯是什么?

呼吸灯其实是在微处理器的控制下,由暗渐亮、然后再由亮渐暗,模仿人呼吸方式的 LED 灯。

1、介绍

呼吸灯采用 PWM 的方式,在固定的频率下,通过调整占空比的方式来控制 LED 灯亮度的变化。PWM(Pulse Width Modulation),即脉冲宽度调制,它利用微处理器输出的 PWM 信号,实现对模拟电路控制的一种非常有效的技术,广泛应用于测量、通信、功率控制等领域。

在由计数器产生的固定周期的 PWM 信号下,如果其占空比为 0,则 LED 灯不亮;如果其占空比为100%,则 LED 灯最亮。所以将占空比从 0 到 100%,再从 100%到 0 不断变化,就可以实现 LED 灯的“呼吸”效果。

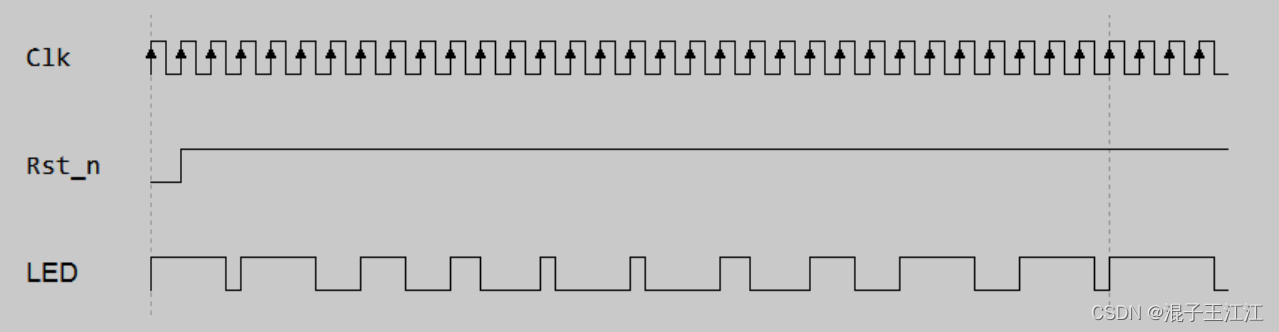

2、占空比调节示意图

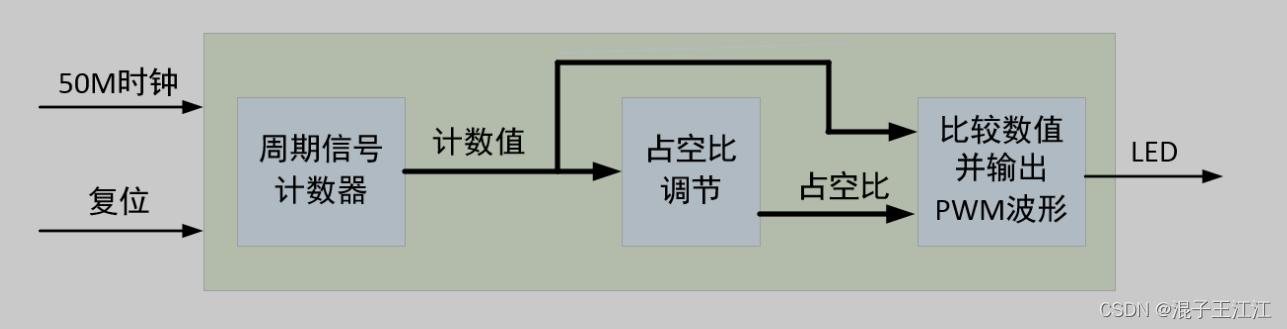

二、系统设计

1、系统框图

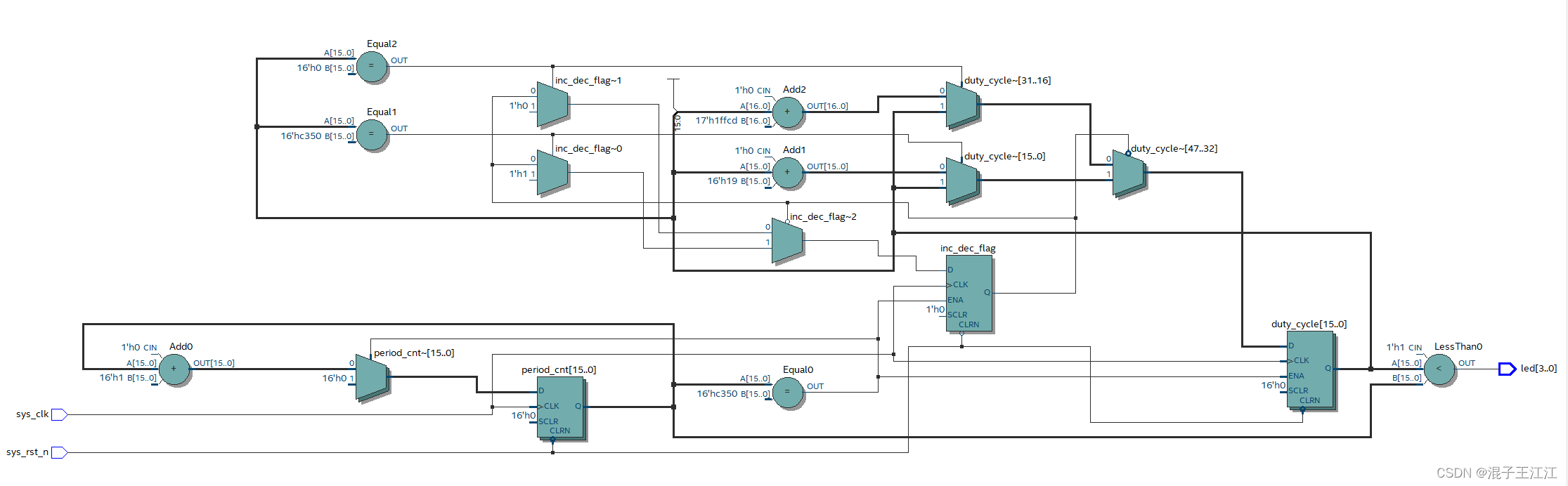

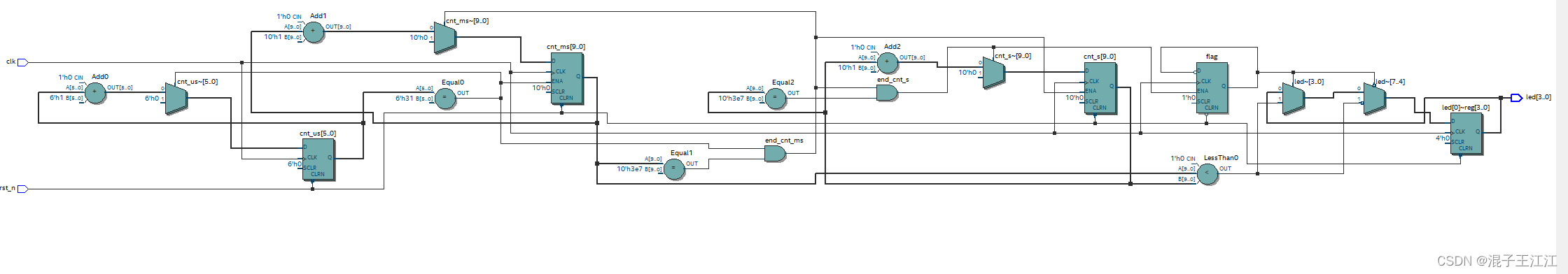

2、RTL视图

- 方法一:

- 方法二:

三、源码

- 方法一:

module BREATH_LED( input sys_clk , //时钟信号 50Mhz input sys_rst_n , //复位信号 output [3:0] led //LED ); //reg define reg [15:0] period_cnt ; //周期计数器频率:1khz 周期:1ms 计数值:1ms/20ns=50000 reg [15:0] duty_cycle ; //占空比数值 reg inc_dec_flag ; //0 递增 1 递减 //***************************************************** //** main code //***************************************************** //根据占空比和计数值之间的大小关系来输出 LED assign led = (period_cnt >= duty_cycle) ? 4'b1111 : 4'b0000; //周期计数器 always @(posedge sys_clk or negedge sys_rst_n) begin if(!sys_rst_n) period_cnt <= 16'd0; else if(period_cnt == 16'd50000) period_cnt <= 16'd0; else period_cnt <= period_cnt + 1'b1; end //在周期计数器的节拍下递增或递减占空比 always @(posedge sys_clk or negedge sys_rst_n) begin if(!sys_rst_n) begin duty_cycle <= 16'd0; inc_dec_flag <= 1'b0; end else begin if(period_cnt == 16'd50000) begin //计满 1ms if(inc_dec_flag == 1'b0) begin //占空比递增状态 if(duty_cycle == 16'd50000) //如果占空比已递增至最大 inc_dec_flag <= 1'b1; //则占空比开始递减 else //否则占空比以 25 为单位递增 else duty_cycle <= duty_cycle + 16'd25; end else begin //占空比递减状态 if(duty_cycle == 16'd0) //如果占空比已递减至 0 inc_dec_flag <= 1'b0; //则占空比开始递增 else //否则占空比以 25 为单位递减 duty_cycle <= duty_cycle - 16'd25; end end end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 方法二:

module BREATH #( parameter TIME_US = 6'd49, TIME_MS = 10'd999, TIME_S = 10'd999) ( input clk, input rst_n, output reg [3:0]led ); // parameter TIME_US = 6'd49; // parameter TIME_MS = 10'd999; // parameter TIME_S = 10'd999; reg [5:0] cnt_us; reg [9:0] cnt_ms; reg [9:0] cnt_s; reg flag; wire add_cnt_us; wire end_cnt_us; wire add_cnt_ms; wire end_cnt_ms; wire add_cnt_s; wire end_cnt_s; always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt_us <= 6'd0; end else if(add_cnt_us)begin if(end_cnt_us)begin cnt_us <= 6'd0; end else begin cnt_us <= cnt_us + 1'd1; end end else begin cnt_us <= cnt_us; end end assign add_cnt_us = 1'b1; assign end_cnt_us = add_cnt_us && cnt_us == TIME_US; always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt_ms <= 10'd0; end else if(add_cnt_ms)begin if(end_cnt_ms)begin cnt_ms <= 10'd0; end else begin cnt_ms <= cnt_ms + 1'd1; end end else begin cnt_ms <= cnt_ms ; end end assign add_cnt_ms = end_cnt_us; assign end_cnt_ms = add_cnt_ms && cnt_ms == TIME_MS; always @(posedge clk or negedge rst_n)begin if(!rst_n)begin cnt_s <= 10'd0; end else if(add_cnt_s)begin if(end_cnt_s)begin cnt_s <= 10'd0; end else begin cnt_s <= cnt_s + 1'd1; end end else begin cnt_s <= cnt_s ; end end assign add_cnt_s = end_cnt_ms; assign end_cnt_s = add_cnt_s && cnt_s == TIME_S; always @(posedge clk or negedge rst_n)begin if(!rst_n)begin flag <= 1'b0; end else if(end_cnt_s)begin flag <= ~flag; end else begin flag <= flag; end end //通过比较秒与毫秒的计数大小实现占空比的变化 //因为毫秒在秒每加一后,都会重新开始,使得高低电平的占比不同 //实际上呼吸灯周期就是秒计数周期,变换的占空比大小就是循环加1或减一 always @(posedge clk or negedge rst_n)begin if(!rst_n)begin led <= 4'b0000; end else if(!flag)begin led <= (cnt_s > cnt_ms)?4'b0000:4'b1111; end else if(flag)begin led <= (cnt_s > cnt_ms)?4'b1111:4'b0000; end else led <= led; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

实际上我更喜欢第一种,代码简洁易懂。

四、效果

呼吸灯

五、总结

呼吸灯的实现过程并不难,在原有的stm32实现呼吸灯的理解下更加透彻,就是通过控制周期里占空比的变化来实现。但值得一提的是第一种实现方法确实比较精简。

六、参考资料

以上资料均来自正点原子的教学视频或开拓者2开发教程:

原子官方

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/酷酷是懒虫/article/detail/791170

推荐阅读

相关标签