- 1CSS 伪元素 content的特殊用法_css 伪类 content

- 2面经 阿里云算法工程师实习生(已拿offer)_阿里云人工智能算法工程师怎么样

- 3Vue实现的人事管理系统,高质量毕业论文范例,附送源码、数据库脚本,项目导入与运行教程,论文撰写教程_人事管理系统vue

- 4python写学生信息管理系统,python学生管理系统报告

- 5数据结构:链表详解 (c++实现)

- 6【ATT&CK】守株待兔式的水坑攻击_常见水坑攻击识别

- 7使用 ElementPlus 组件时,遇到的一些问题及解决方案_elementplustype "password" is not assignable to ty

- 8VHDL和Verilog中数组定义、初始化、赋值方法_verilog数组表示及初始化

- 9题库数据库设计

- 10Hexo+GitHub+Netlify:打造高效个性化博客的完整指南_netlify部署hexo博客

Chisel入门——在windows系统下部署Chisel环境并点亮FPGA小灯等实验_chisel windows

赞

踩

Chisel入门——在windows系统下部署Chisel环境并点亮FPGA小灯等实验

一、chisel简介

传统数字芯片的RTL设计采用Verilog语言为主,Chisel语言的全称是Constructing Harward in Scala Embeded Language,即在Scala语言中导入Chisel3库,即可使用Chisel语言。其特点是面向对象编程,可以方便地参数化定制硬件电路,加快设计流程。目前在RISC-V生态中应用较多,中科院计算所主持的培育下一代处理器设计人才的“一生一芯”项目也在极力推进该语言。

Chisel是一个Scala库,用于构建高级别的、可综合的、模块化的硬件设计。它允许设计师在高层次上定义硬件的行为,然后通过一系列的转换步骤将其转换为低层次的Verilog或VHDL代码。这使得设计师可以专注于实现硬件的功能,而不需要关心底层的细节。

Chisel的主要特点包括:

高级抽象:使用Scala的高级别抽象来描述硬件行为。

可综合:生成的Verilog或VHDL代码可以直接用于ASIC或FPGA的设计。

模块化:可以将设计分解为多个独立的模块,每个模块都可以独立地进行测试和验证。

交互式开发:可以在Scala REPL中直接运行Chisel代码,以便于调试和验证。

为什么要提出Chisel?

Chisel的设计者们是这么说的(以下翻译自官网Motivation – “Why Chisel?”):

在我们的科研项目和硬件设计课程中,与现有硬件描述语言进行了多年的斗争,这促使我们开发一种新的硬件语言。Verilog和VHDL是作为硬件仿真语言开发的,直到后来它们才成为硬件综合的基础。这些语言的大部分语义不适用于硬件综合,事实上,许多结构都无法综合。其他结构在他们如何映射到硬件实现是很不直观的,或者说他们的使用可能会意外地导致非常低效的硬件结构。虽然可以使用这些语言的子集并且还能得到可以接受的效果,但它们仍然呈现出混乱和令人困惑的规范模型,特别是在教学环境中。

然而,我们开发新硬件语言的最强烈动机是我们希望改变电子系统设计的方式。我们认为,重要的是不仅要教学生如何设计电路,还要教他们如何设计电路生成器——从高级设计参数和约束自动生成设计的程序。通过电路生成器,我们希望利用设计专家的辛勤工作,为大家提高设计抽象水平。为了表达灵活和可拓展的电路结构,电路生成器必须采用复杂的编程技术来确定如何根据高级参数值和约束更好地定制其输出电路。虽然Verilog和VHDL包含一些用于编程电路生成的原始结构,但它们缺乏现代编程语言中的强大功能,例如面向对象编程、类型推断、对函数式编程的支持以及反射等。

我们没有从头开始构建新的硬件设计语言,而是选择在现有语言中嵌入硬件构造原语,我们选择Scala不仅是因为它包含我们认为对于构建电路生成器很重要的编程特性,还因为它是专门作为特定领域语言(DSL)的基础而开发的。

这里只做简单的介绍:更多资料可以查看以下链接

链接: link

二、vscode搭建scala开发环境

2.1 安装Scala官方插件

在VS Code中安装插件,先安装 Scala Syntax (official),再安装 Scala (Metals):

第一个和第二个都需要安装

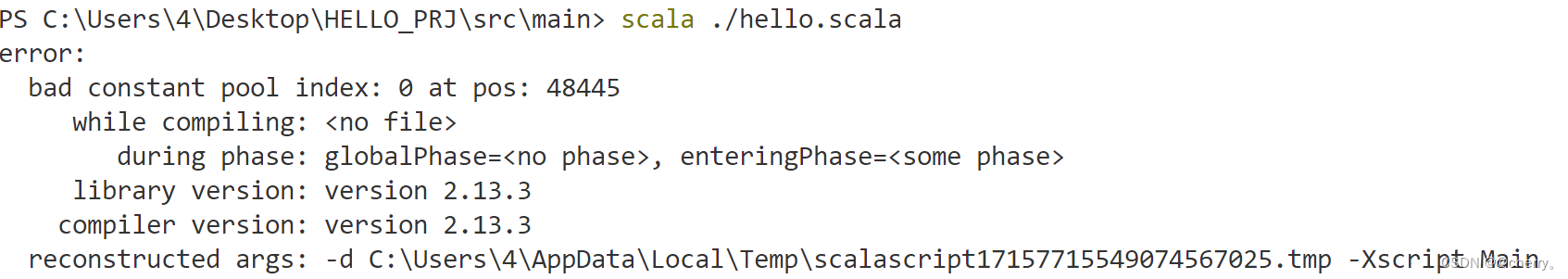

2.2 java版本(本人用的是jdk18)

注意可能部分jdk不适配

直接打开终端,输入

java -version

- 1

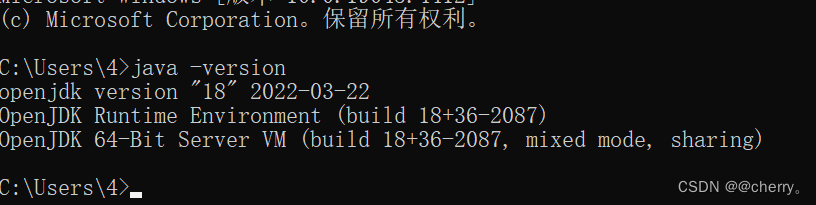

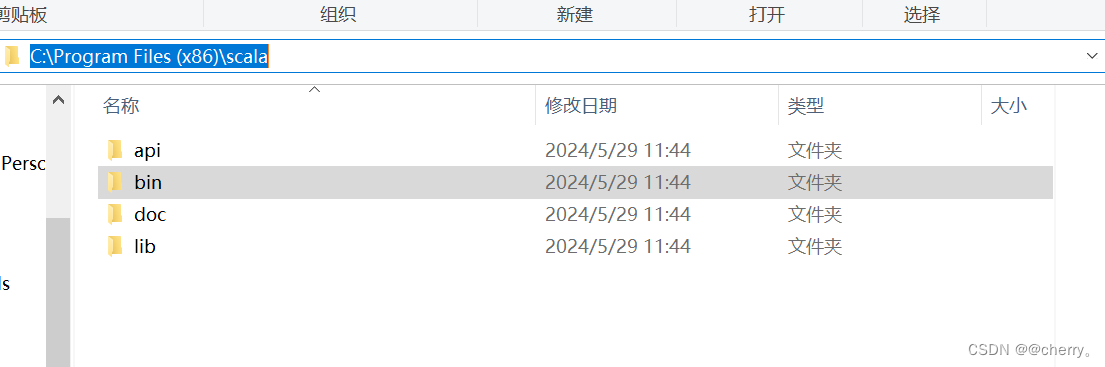

2.3 下载Scala Windows版本的二进制文件

下载链接:link

然后一直点击next即可

注意需要记得安装的路径

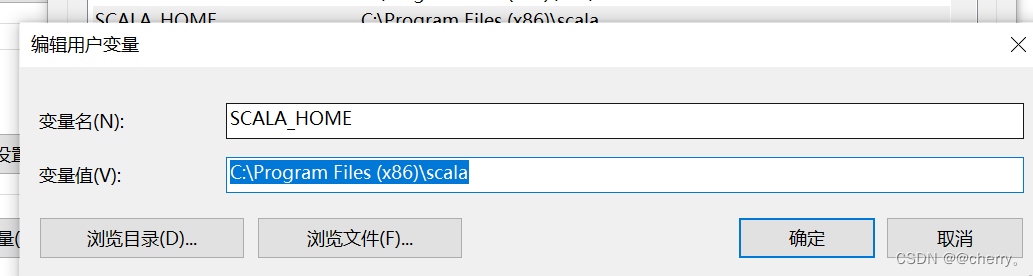

2.4 配置环境变量

1、变量值即为安装的路径

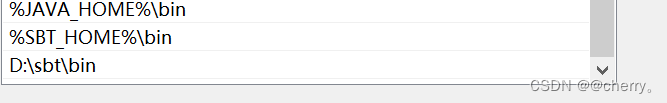

2.PATH变量下再新增值

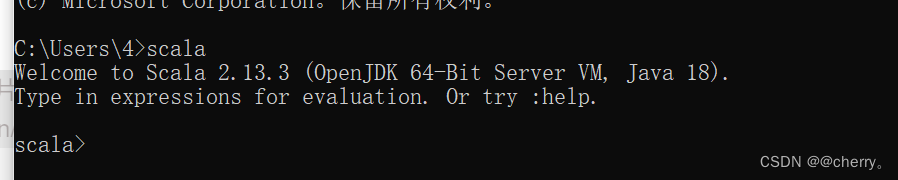

2.5 scala测试

终端输入scala,出现以下信息即可

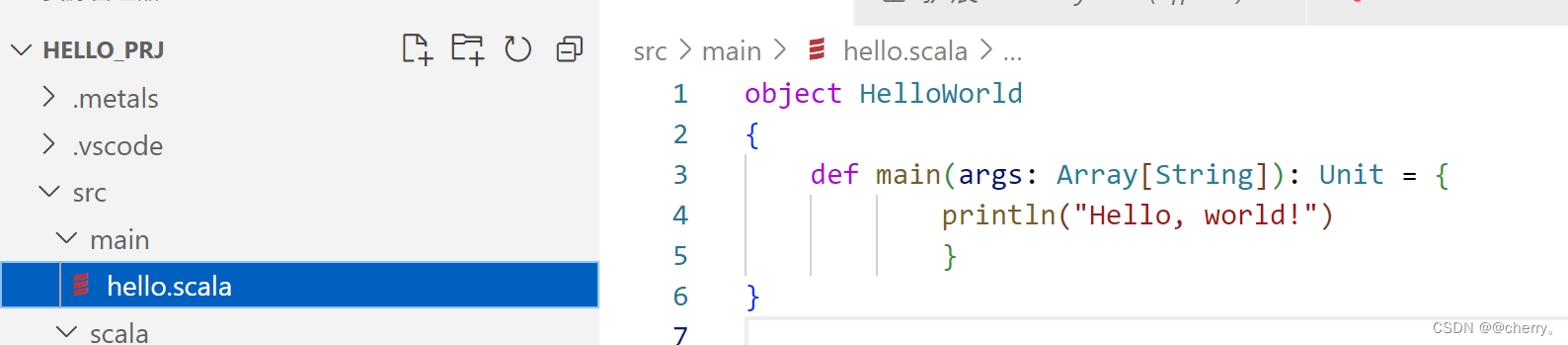

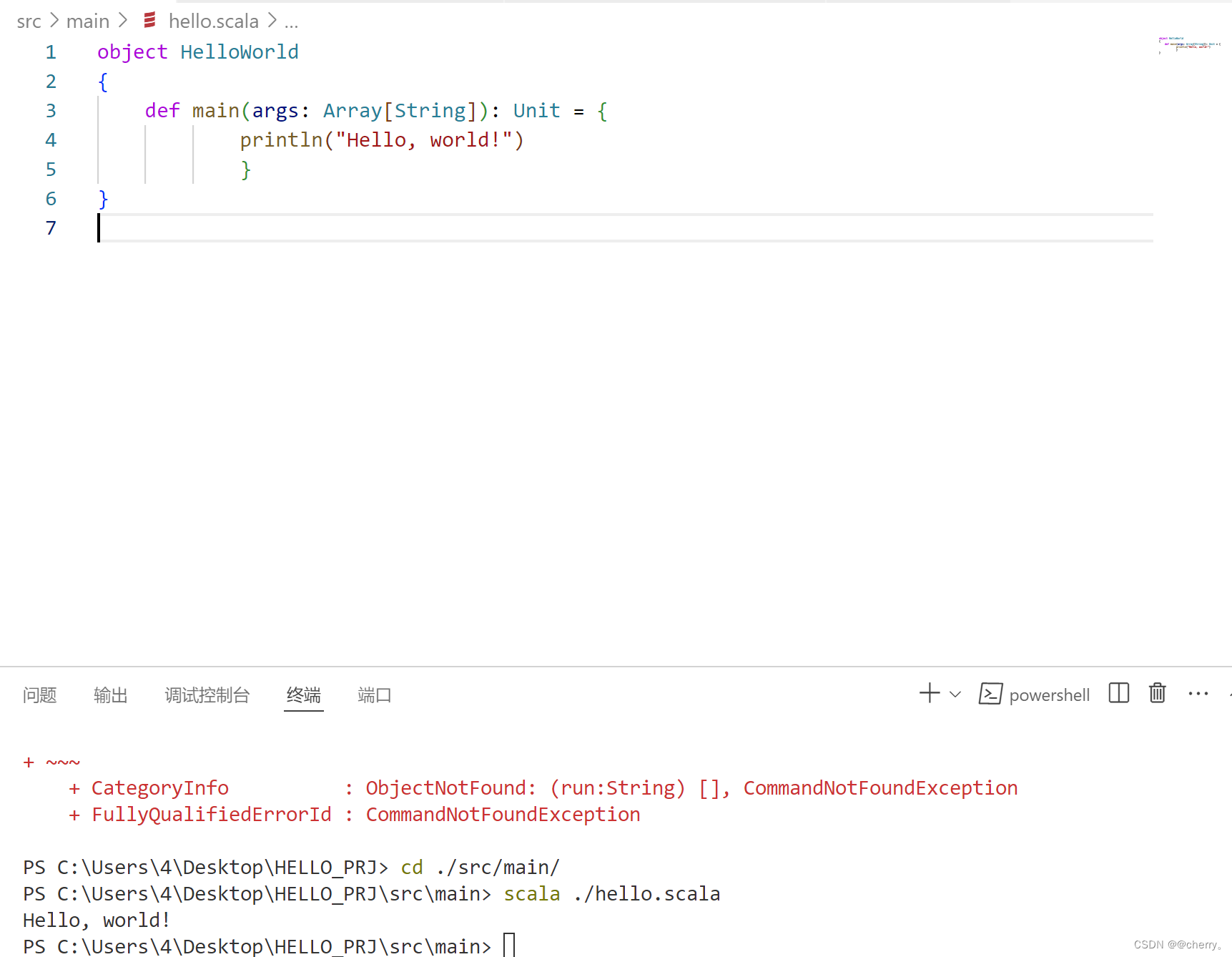

2.6 vscode运行scala

代码如下:

object HelloWorld

{

def main(args: Array[String]): Unit = {

println("Hello, world!")

}

}

- 1

- 2

- 3

- 4

- 5

- 6

三、windows安装sbt

3.1、sbt下载及安装

官网:http://www.scala-sbt.org/download.html

如果下载的是压缩文件,解压后需要配置环境变量等

通过下面这种方式一般都自动配置好了环境变量

点击next即可,还是要记住安装路径()

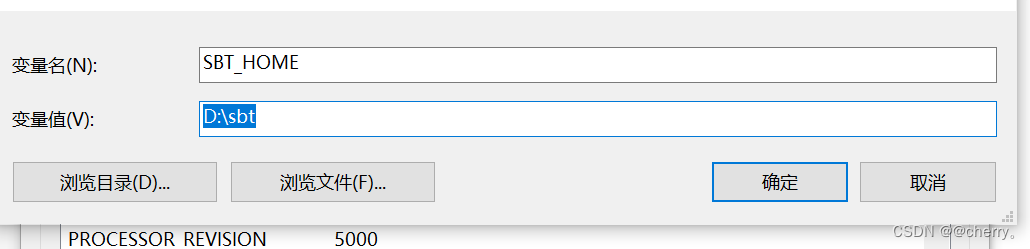

3.2 配置环境变量

这里和sacla的配置内容相同

3.3 sbt配置

修改 sbt\conf\sbtconfig.txt 为以下内容:

# sbt configuration file for Windows # Set the java args #-mem 1024 was added in sbt.bat as default -Xms1024m -Xmx1024m -Xss4M -XX:ReservedCodeCacheSize=128m # Set the extra sbt options -Dsbt.log.format=true -Dsbt.boot.directory=D:/sbt/boot/ -Dsbt.global.base=D:/sbt/.sbt -Dsbt.ivy.home=D:/sbt/.ivy2 -Dsbt.repository.config=D:/sbt/conf/repo.properties -Dsbt.override.build.repos=true

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

设置阿里云镜像,国内的网络环境复杂,在 sbt\conf\ 下新建 repo.properties 文件,内容为

[repositories] local aliyun-central: https://maven.aliyun.com/repository/central aliyun-public: https://maven.aliyun.com/repository/public jcenter: https://jcenter.bintray.com/ repo1: https://repo1.maven.org/maven2/ store_2: https://repo2.maven.org/maven2/ aliyun-releases: https://maven.aliyun.com/repository/releases aliyun-apache-snapshots: https://maven.aliyun.com/repository/apache-snapshots aliyun-google: https://maven.aliyun.com/repository/google aliyun-jcenter: https://maven.aliyun.com/repository/jcenter aliyun-spring: https://maven.aliyun.com/repository/spring aliyun-spring-plugin: https://maven.aliyun.com/repository/spring-plugin sbt-plugin: https://repo.scala-sbt.org/scalasbt/sbt-plugin-releases/ sonatype: https://oss.sonatype.org/content/repositories/snapshots typesafe: https://repo.typesafe.com/typesafe/ivy-releases/, [organization]/[module]/(scala_[scalaVersion]/)(sbt_[sbtVersion]/)[revision]/[type]s/[artifact](-[classifier]).[ext], bootOnly typesafe2: https://repo.typesafe.com/typesafe/releases/ atlassian: https://packages.atlassian.com/content/repositories/atlassian-public/ spring-plugin: https://repo.spring.io/plugins-release/ hortonworks: https://repo.hortonworks.com/content/repositories/releases/

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

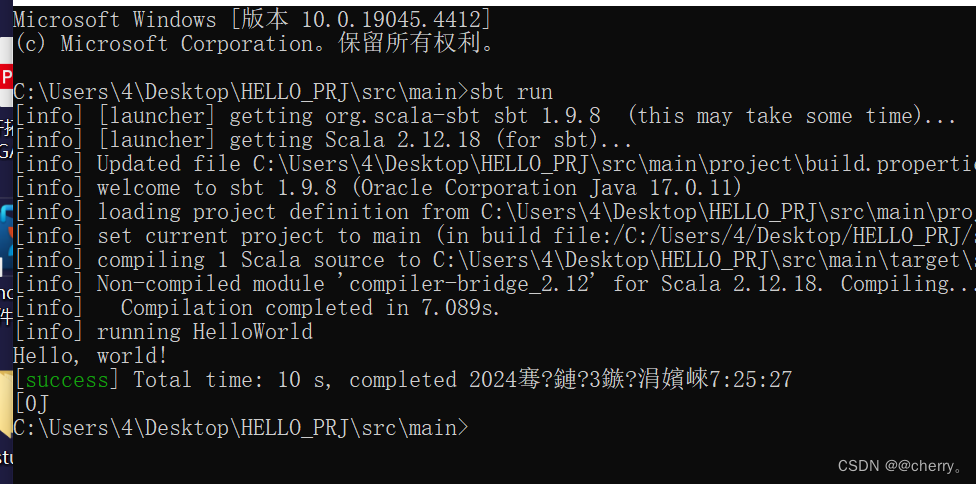

3.4测试

完成后打开cmd,输入 sbt,可能会有一段下载依赖包的过程,成功后会进入命令行,即sbt安装成功

退出方式:在命令框中输入 exit 即可退出

四、用Chisel点亮FPGA小灯

参考的chisel书为chisel-book,是一个PDF文档,

链接: link

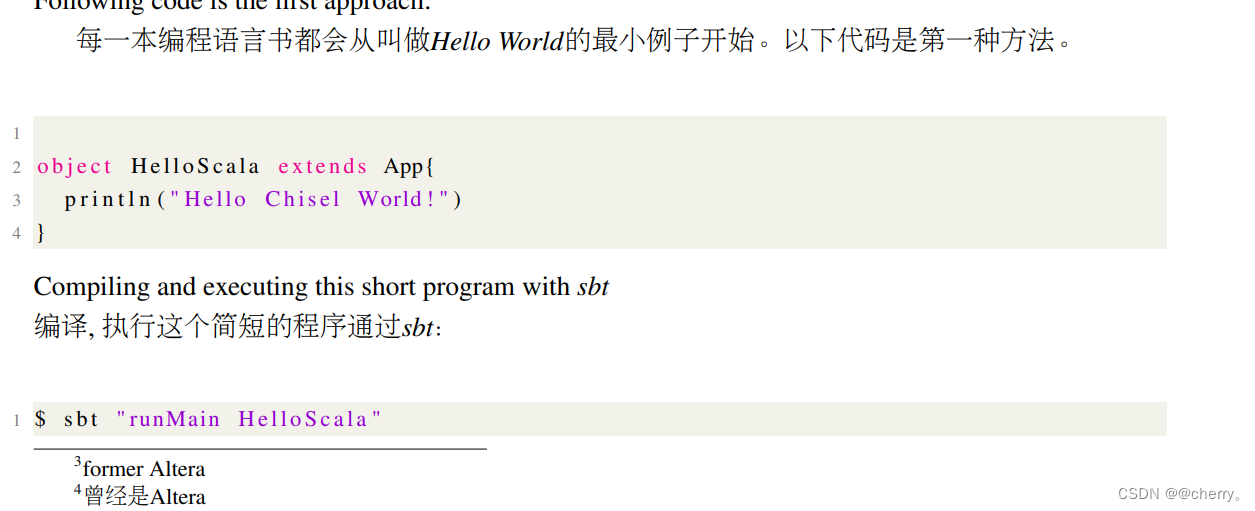

4.1 Hello world 实现

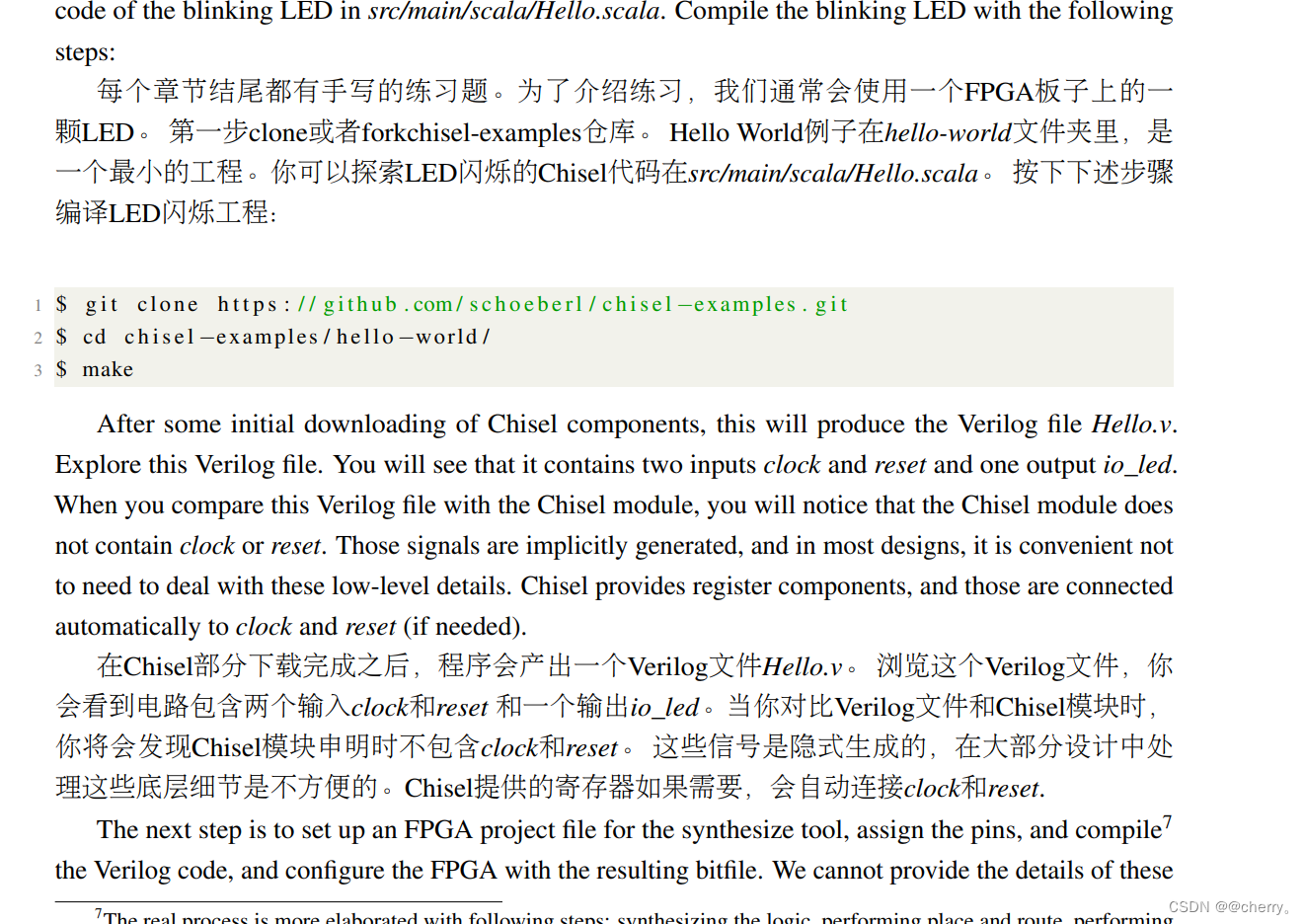

我们从书上找到相应的代码,然后把代码拉下来

git clone https://gitcode.com/schoeberl/chisel-examples.git

- 1

我们知道FPGA需要的是.v文件,显然我们拉下来的代码并没有这个文件,所以我们需要进行一些处理

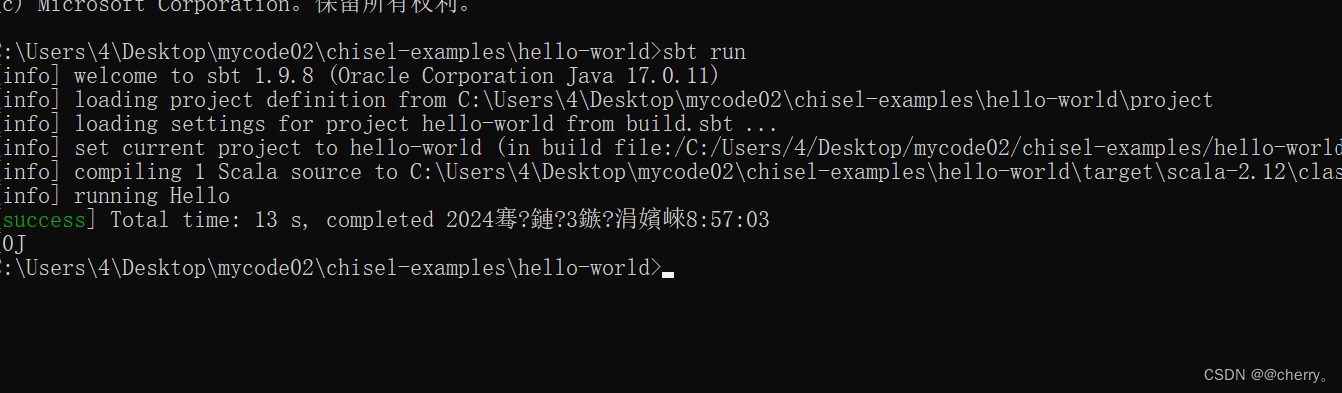

来到当前文件目录,运行 sbt run

第一次编译需要等待一段时间,然后显示成功。

hello.scala

//点亮小灯 /* * This code is a minimal hardware described in Chisel. * * Blinking LED: the FPGA version of Hello World */ // import chisel3._ // /** * The blinking LED component. */ // class Hello extends Module { val io = IO(new Bundle { val led = Output(UInt(1.W)) }) val CNT_MAX = (50000000 / 2 - 1).U // val cntReg = RegInit(0.U(32.W)) val blkReg = RegInit(0.U(1.W)) // cntReg := cntReg + 1.U when(cntReg === CNT_MAX) { cntReg := 0.U blkReg := ~blkReg } io.led := blkReg } // /** * An object extending App to generate the Verilog code. */ object Hello extends App { (new chisel3.stage.ChiselStage).emitVerilog(new Hello()) }

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

然后即可生成.v文件

hello.v文件如下

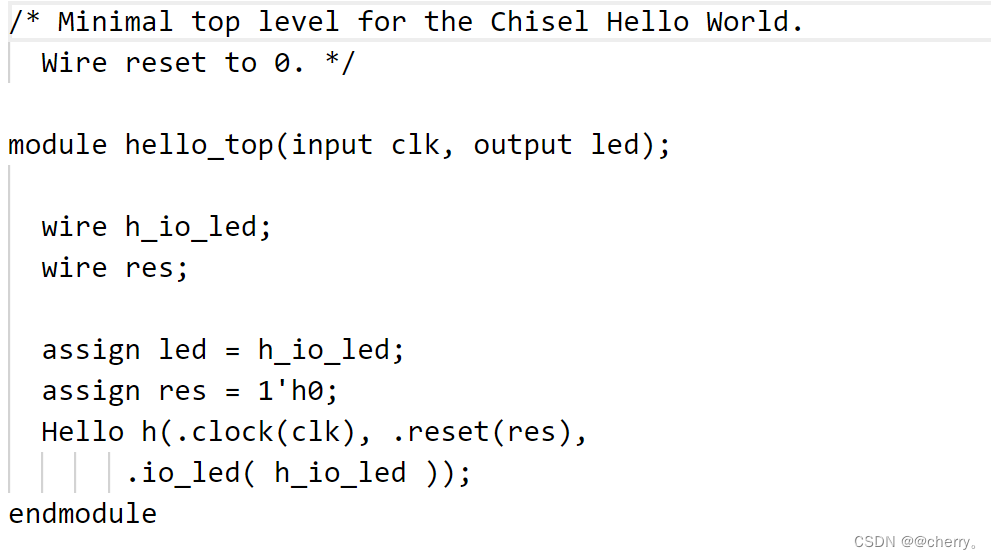

以及顶层文件 hello_top.v:

4.2 上板验证

-

创建quartus项目

板子型号为 EP4CE115F29C7 -

加入.v文件

将生成的 Hello.v文件 和 hello_top.v文件 添加到项目中,并设置hello_top.v为顶层文件:

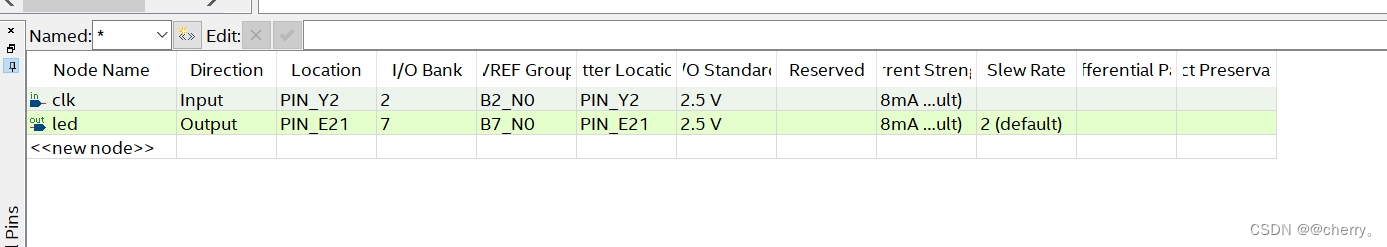

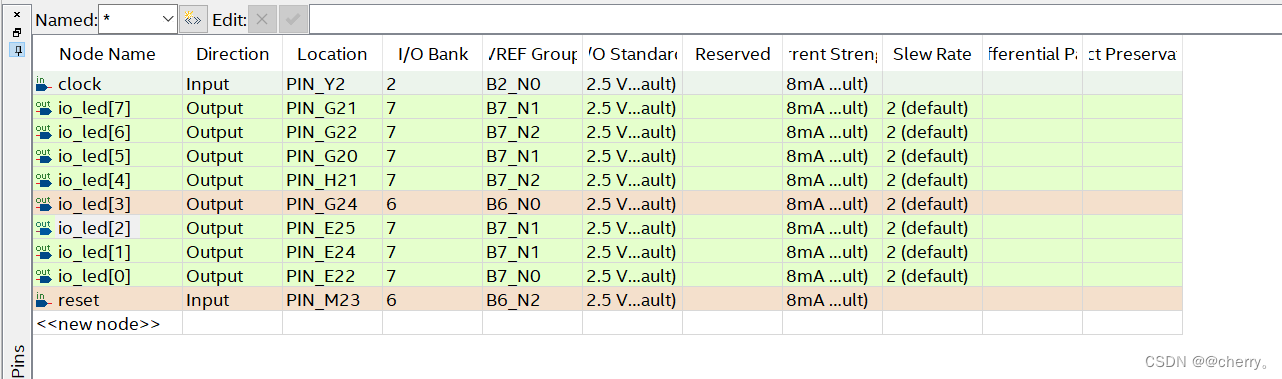

3、引脚绑定

4、烧入

实验结果如下:

五、在DE2-115开发板上实现流水灯

步骤和上面相似:

修改 Hello.scala 文件为:

import chisel3._ import chisel3.util._ class Hello extends Module { val io = IO(new Bundle { val led = Output(UInt(8.W)) // 8 位 LED 输出 }) val maxCount = (50000000 / 10).U // 调整这个参数改变流水灯的速度(DE2-115 使用 50MHz 时钟) val counter = RegInit(0.U(32.W)) val position = RegInit(0.U(3.W)) // 计数器逻辑 counter := counter + 1.U when(counter === maxCount) { counter := 0.U when(position === 7.U) { position := 0.U }.otherwise { position := position + 1.U } } // LED 输出逻辑 io.led := (1.U << position) } object Hello extends App { (new chisel3.stage.ChiselStage).emitVerilog(new Hello()) }

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

修改后再次运行

hello.v 文件

module Hello( input clock, input reset, output [7:0] io_led ); `ifdef RANDOMIZE_REG_INIT reg [31:0] _RAND_0; reg [31:0] _RAND_1; `endif // RANDOMIZE_REG_INIT reg [31:0] counter; // @[Hello.scala 10:24] reg [2:0] position; // @[Hello.scala 11:25] wire [31:0] _counter_T_1 = counter + 32'h1; // @[Hello.scala 14:22] wire [2:0] _position_T_1 = position + 3'h1; // @[Hello.scala 20:28] assign io_led = 8'h1 << position; // @[Hello.scala 25:18] always @(posedge clock) begin if (reset) begin // @[Hello.scala 10:24] counter <= 32'h0; // @[Hello.scala 10:24] end else if (counter == 32'h4c4b40) begin // @[Hello.scala 15:30] counter <= 32'h0; // @[Hello.scala 16:13] end else begin counter <= _counter_T_1; // @[Hello.scala 14:11] end if (reset) begin // @[Hello.scala 11:25] position <= 3'h0; // @[Hello.scala 11:25] end else if (counter == 32'h4c4b40) begin // @[Hello.scala 15:30] if (position == 3'h7) begin // @[Hello.scala 17:28] position <= 3'h0; // @[Hello.scala 18:16] end else begin position <= _position_T_1; // @[Hello.scala 20:16] end end end // Register and memory initialization `ifdef RANDOMIZE_GARBAGE_ASSIGN `define RANDOMIZE `endif `ifdef RANDOMIZE_INVALID_ASSIGN `define RANDOMIZE `endif `ifdef RANDOMIZE_REG_INIT `define RANDOMIZE `endif `ifdef RANDOMIZE_MEM_INIT `define RANDOMIZE `endif `ifndef RANDOM `define RANDOM $random `endif `ifdef RANDOMIZE_MEM_INIT integer initvar; `endif `ifndef SYNTHESIS `ifdef FIRRTL_BEFORE_INITIAL `FIRRTL_BEFORE_INITIAL `endif initial begin `ifdef RANDOMIZE `ifdef INIT_RANDOM `INIT_RANDOM `endif `ifndef VERILATOR `ifdef RANDOMIZE_DELAY #`RANDOMIZE_DELAY begin end `else #0.002 begin end `endif `endif `ifdef RANDOMIZE_REG_INIT _RAND_0 = {1{`RANDOM}}; counter = _RAND_0[31:0]; _RAND_1 = {1{`RANDOM}}; position = _RAND_1[2:0]; `endif // RANDOMIZE_REG_INIT `endif // RANDOMIZE end // initial `ifdef FIRRTL_AFTER_INITIAL `FIRRTL_AFTER_INITIAL `endif `endif // SYNTHESIS endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

(这个实验直接把hello.v文件设为top文件即可,不需要加其他文件了)

然后依照和上面一样即可

引脚绑定信息如下:

实验效果:需要按住key0

六、心得体会

初次使用chisel,说实话遇到了许多的困难,无论是软件安装还是例子的寻找的遇到了一定的问题,最后磕磕绊绊终于完成了本次实验。

Chisel以Scala为基础,它的抽象级别高,极大提升了硬件设计效率,让代码更简洁且易于维护。通过Chisel,我体验了用近似软件工程的思维做硬件设计的便捷,特别是在模块化、参数化设计上的优势,这为复用代码和快速迭代创造了条件。Chisel结合Scala的强大生态,使得测试和验证更加高效,同时降低了硬件设计的学习曲线,尤其适合教学和研究用途。

感谢这些文章

https://blog.csdn.net/weixin_43681766/article/details/124905667

https://blog.csdn.net/zhengwenbang/article/details/108483335