- 1【leetcode】数组专场,二分查找,左右边界问题_算法边界问题

- 2[海森推荐]人工智能-人工智能好书推荐_人工智能从小白到大神pdf

- 3Windows系统缺失api-ms-win-crt-private-l1-1-0.dll文件的完美办法_api-ms-win-crt-private-|1-1-0.dll

- 4终端报错"xcrun: error: unable to find utility “xcodebuild”, not a developer tool or

- 5Springboot2.0 实现进销存项目

- 6不会做的题汇总

- 720240115在ubuntu20.04.6下查看显卡信息_ubuntu查看显卡型号和显存

- 8为什么越来越多的网站用户选择接入安全加速SCDN

- 9合合信息旗下启信宝3·15黄金市场洞察:新增企业量5年连降

- 10Spring AI - 使用向量数据库实现检索式AI对话_spring向量数据库

基于FPGA的UDP协议栈设计第七章_RGMII模块设计

赞

踩

前言:

该部分内容主要需要掌握各种IO和时钟相关的原语使用

一、GMII和RGMII简介

以太网的通信离不开PHY芯片,PHY芯片实现实现了RGMII接口到网口(RJ45)的转换,RGMII接口就是PHY芯片和FPGA之间的接口。

GMII:GMII(Gigabit Media Independant Interface),千兆MII接口。GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps。同时兼容MII所规定的10/100 Mbps工作方式。GMII接口数据结构符合IEEE以太网标准,该接口定义见IEEE 802.3-2000。信号定义如下:

RGMII:RGMII(Reduced Gigabit Media Independant Interface),精简GMII接口。相对于GMII相比,RGMII具有如下特征:

发送/接收数据线由8条改为4条

TX_ER和TX_EN复用,通过TX_CTL传送

RX_ER与RX_DV复用,通过RX_CTL传送

1 Gbit/s速率下,时钟频率为125MHz

100 Mbit/s速率下,时钟频率为25MHz

10 Mbit/s速率下,时钟频率为2.5MHz

信号定义如下:

ETH_RXC:接收数据参考时钟, 1000Mbps 速率下,时钟频率为 125MHz,时钟为上下沿同时采样;100Mbps 速率下,时钟频率为 25MHz; 10Mbps 速率下,时钟频率为2.5MHz, ETH_RXC 由 PHY 侧提供。

ETH_RXCTL( ETH_RX_DV):接收数据控制信号。

ETH_RXD:四位并行的接收数据线。

ETH_TXC:发送参考时钟, 1000Mbps 速率下,时钟频率为 125MHz,时钟为上下沿同时采样;100Mbps 速率下,时钟频率为 25MHz; 10Mbps 速率下,时钟频率为2.5MHz, ETH_TXC 由 MAC 侧提供。

ETH_TXCTL( ETH_TXEN):发送数据控制信号。

ETH_TXD:四位并行的发送数据线。

ETH_RESET_N:芯片复位信号,低电平有效。

ETH_MDC:数据管理时钟( Management Data Clock),该引脚对 ETH_MDIO 信号提供了一个同步的时钟。

ETH_MDIO:数据输入/输出管理( Management Data Input/Output),该引脚提供了一个双向信号用于传递管理信息。

其中 ETH_RXC、 ETH_RXCTL 和 ETH_RXD 为 MAC 接收侧引脚; ETH_TXC、 ETH_TXCTL 和

ETH_TXD 为 MAC 发送侧引脚; ETH_MDC 和 ETH_MDIO 为 MDIO 接口引脚,用于配置 PHY 芯片内部寄存器; ETH_RST_N 为 PHY 芯片硬件复位信号。由于 PHY 芯片的内部寄存器在默认配置下也可以正常工作,因此本次实验没有对 MDIO 接口进行读写操作,只用到了以太网的 RGMII 接口信号和复位信号。RGMII 使用 4bit 数据接口,在 1000Mbps 通信速率下, ETH_TXC 和 ETH_RXC 的时钟频率为125Mhz,采用上下沿 DDR( Double Data Rate)的方式在一个时钟周期内传输 8 位数据信号,即上升沿发送/接收低 4 位数据,下降沿发送/接收高 4 位数据。 ETH_TXCTL 和 ETH_RXCTL 控制信号同样采用 DDR的方式在一个时钟周期内传输两位控制信号,即上升沿发送/接收数据使能( TX_EN/RX_ DV)信号,下降沿发送/接收使能信号与错误信号的异或值( TX_ERR xor TX_EN、 RX_ERR xor RX_DV)。当 RX_DV 为高电平(表示数据有效), RX_ERR 为低电平(表示数据无错误),则异或的结果值为高电平,因此只有当ETH_RXCTL 和 ETH_TXCTL 信号的上下沿同时为高电平时,发送和接收的数据有效且正确。

以下内容参考正点原子达芬奇开发板资料

1.1、接收数据过程

由上图可知, RXC 的上下边沿与 RXD 和 RX_CTL 信号对齐,相位相同。

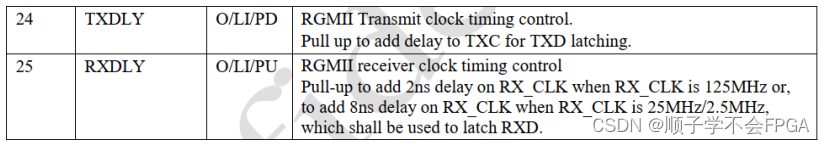

由上图可知, RXC 的上下边沿与 RXD 和 RX_CTL 信号的中间位置对齐, RXC 的时钟周期为 8ns,单个高电平或者低电平为 4ns, RXC 相对于 RXD 和 RX_CTL 延时约 2ns。YT8531(达芬奇开发板PHY芯片) RGMII 接收端口的信号对齐模式由硬件上的引脚外接上下拉电阻进行配置,如图 53.1.11 所示。从下图中可以看出, RXC 时钟相对于 RXD 信号,在 1000M 的速率下会增加约 2ns 的延时。我们知道在开发板硬件原理图中 YT8531 的管脚 RXD0_RXDLY 和 RXD1_TXDLY 接的是上拉电阻,因此 RXC 和RXD 之间以及 TXC 和 TXD 之间在千兆网下都会有 2ns 的延时, RGMII 接收端口的时序图如图 53.1.10 所示。

注:一般来说开发板默认配置的PHY应该都是带延时的 ,像达芬奇这种直接就焊电路板就把配置定好了,但有的板卡要自己修改寄存器数值。

1.2、发送数据过程

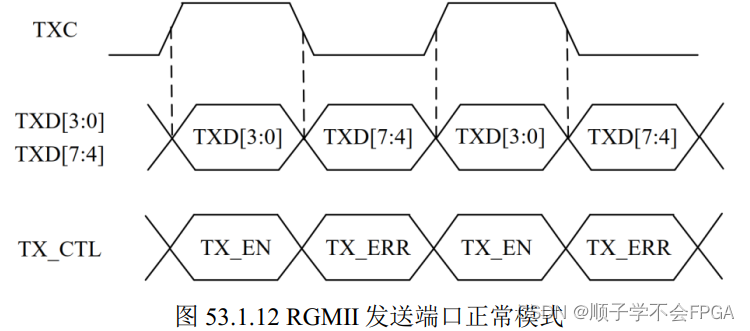

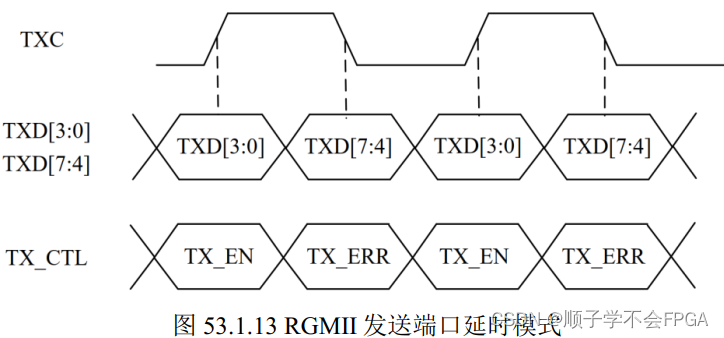

RGMII 发送端口正常模式下,需要满足 TXC 的上下边沿与 TXD 和 TX_CTL 信号对齐,相位相同。 YT8531 在硬件上面也做 TX 端的 delay 模式,可根据实际情况,选择是否在代码中进行延时

(因为一般对端设备的接收端会有延时处理的功能,因此发送端也可以不延时),延时后的时序图如下所示:

由 RGMII 的接口时序可知, RGMII 发送端口在 TXC 时钟的上升沿传输 TXD 的低 4 位和 TX_CTL 的

使能信号;下降沿传输 TXD 的高 4 位和 TX_CTL 的错误信号(实际上是使能信号和错误信号的异或值);RGMII 接收端口在 RXC 时钟的上升沿传输 RXD 的低 4 位和 RX_CTL 的使能信号;下降沿传输 RXD 的高4 位和 RX_CTL 的错误信号(实际上是使能信号和错误信号的异或值)。

二、IDDR、ODDR、IDEALY2和ODELAY2

该部分内容详见上一篇内容:IDDR、ODDR、IDEALY2和ODELAY2详解

三、BUFG和BUFIO

BUFIO :IO时钟网络,它只能驱动IO Block里面的逻辑,不能驱动CLB里面的LUT,REG等逻辑。

BUFR :是regional时钟网络,它的驱动范围只能局限在一个clock region的逻辑,但是它可以同时驱动IO和内部逻辑。

BUFG :是全局时钟网络,它可以驱动所有的IO和逻辑,并且可以被Transceiver所驱动。

BUFR相比BUFG的最大优势是skew和功耗都比较小,在源同步的设计中,这一点也是很关键的。

四、FPGA代码设计

有了以上知识,该模块设计就简单多了

至于如何适用百兆以太网,只需要在使用ODDR时在一个时钟周期内上升沿和下降沿都传输相同数据即可

设计代码为本人参考FPGA奇哥系列网课自行编写

module RGMII_Tri( /*--------rgmii port--------*/ input i_rxc , input [3 :0] i_rxd , input i_rx_ctl , output o_txc , output [3 :0] o_txd , output o_tx_ctl , /*--------data port--------*/ input idelay_clk , input dly_clk, output o_rxc , input [7 :0] i_send_data , input i_send_valid , output [7 :0] o_rec_data , output o_rec_valid , output o_rec_end , output [1:0] o_speed , output o_link ); //parameter define parameter IDELAY_VALUE = 0; reg [7 :0] ri_send_data =0 ; reg ri_send_valid=0 ; reg [7 :0] ro_rec_data = 0 ; reg ro_rec_valid= 0 ; reg ro_rec_end = 0 ; reg r_cnt_10_100= 0 ; reg r_tx_cnt_10_100 = 0 ; reg [1 :0] ro_speed=0 ; reg ro_link =0 ; reg [1 :0] r_rec_valid=0 ; wire w_rxc_bufr ; wire w_rxc_bufio ; wire w_rxc_idelay ; wire [3 :0] w_rxd_ibuf ; wire w_rx_ctl_ibuf ; wire [7 :0] w_rec_data ; wire [1 :0] w_rec_valid ; wire [3 :0] w_send_d1 ; wire [3 :0] w_send_d2 ; wire w_send_valid ; wire i_speed1000 ; wire w_txc ; wire w_txc_90 ; wire w_rxc_bufr_dly; wire [3:0] w_rxd_idly; wire w_rx_ctl_idly; assign w_txc = ~w_rxc_bufr; assign o_rxc = w_rxc_bufr; assign o_speed = ro_speed ; assign o_link = ro_link ; assign i_speed1000 = 1; assign o_rec_data = ro_rec_data ; assign o_rec_valid = ro_rec_valid; assign o_rec_end = ro_rec_end ; OBUF #( .DRIVE (12 ), // Specify the output drive strength .IOSTANDARD ("DEFAULT" ), // Specify the output I/O standard .SLEW ("SLOW" ) // Specify the output slew rate ) OBUF_inst ( .O (o_txc ), // Buffer output (connect directly to top-level port) .I (w_txc ) // Buffer input ); BUFIO BUFIO_inst ( .O (w_rxc_bufio ), .I (i_rxc ) ); BUFG BUFG_inst ( .O(w_rxc_bufr), // 1-bit output: Clock output .I(i_rxc) // 1-bit input: Clock input ); genvar rxd_i; generate for(rxd_i = 0 ;rxd_i < 4 ;rxd_i = rxd_i + 1) begin IBUF #( .IBUF_LOW_PWR ("TRUE" ), .IOSTANDARD ("DEFAULT" ) ) IBUF_U ( .O (w_rxd_ibuf[rxd_i] ), // Buffer output .I (i_rxd[rxd_i] ) // Buffer input (connect directly to top-level port) ); (* IODELAY_GROUP = "rgmii_rx_delay" *) IDELAYCTRL IDELAYCTRL_inst ( .RDY(), // 1-bit output: Ready output .REFCLK(idelay_clk), // 1-bit input: Reference clock input .RST(1'b0) // 1-bit input: Active high reset input ); //rgmii_rx_ctl??????????????? (* IODELAY_GROUP = "rgmii_rx_delay" *) IDELAYE2 #( .IDELAY_TYPE ("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE .IDELAY_VALUE (IDELAY_VALUE), // Input delay tap setting (0-31) .REFCLK_FREQUENCY(200.0) // IDELAYCTRL clock input frequency in MHz ) u_delay_rxd ( .CNTVALUEOUT (), // 5-bit output: Counter value output .DATAOUT (w_rxd_idly[rxd_i]),// 1-bit output: Delayed data output .C (1'b0), // 1-bit input: Clock input .CE (1'b0), // 1-bit input: enable increment/decrement .CINVCTRL (1'b0), // 1-bit input: Dynamic clock inversion input .CNTVALUEIN (5'b0), // 5-bit input: Counter value input .DATAIN (1'b0), // 1-bit input: Internal delay data input .IDATAIN (w_rxd_ibuf[rxd_i]), // 1-bit input: Data input from the I/O .INC (1'b0), // 1-bit input: Increment / Decrement tap delay .LD (1'b0), // 1-bit input: Load IDELAY_VALUE input .LDPIPEEN (1'b0), // 1-bit input: Enable PIPELINE register .REGRST (1'b0) // 1-bit input: Active-high reset tap-delay input ); IDDR #( .DDR_CLK_EDGE ("SAME_EDGE_PIPELINED" ), .INIT_Q1 (1'b0 ), .INIT_Q2 (1'b0 ), .SRTYPE ("SYNC" ) ) IDDR_u0 ( .Q1 (w_rec_data[rxd_i] ), // 1-bit output for positive edge of clock .Q2 (w_rec_data[rxd_i +4] ), // 1-bit output for negative edge of clock .C (w_rxc_bufio ), .CE (1 ), .D (w_rxd_idly[rxd_i] ), .R (0 ), .S (0 ) ); end endgenerate IBUF #( .IBUF_LOW_PWR ("TRUE" ), .IOSTANDARD ("DEFAULT" ) ) IBUF_U ( .O (w_rx_ctl_ibuf ), // Buffer output .I (i_rx_ctl ) // Buffer input (connect directly to top-level port) ); (* IODELAY_GROUP = "rgmii_rx_delay" *) IDELAYE2 #( .IDELAY_TYPE ("FIXED"), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE .IDELAY_VALUE (IDELAY_VALUE), // Input delay tap setting (0-31) .REFCLK_FREQUENCY(200.0) // IDELAYCTRL clock input frequency in MHz ) u_delay_rx_ctrl ( .CNTVALUEOUT (), // 5-bit output: Counter value output .DATAOUT (w_rx_ctl_idly),// 1-bit output: Delayed data output .C (1'b0), // 1-bit input: Clock input .CE (1'b0), // 1-bit input: enable increment/decrement .CINVCTRL (1'b0), // 1-bit input: Dynamic clock inversion input .CNTVALUEIN (5'b0), // 5-bit input: Counter value input .DATAIN (1'b0), // 1-bit input: Internal delay data input .IDATAIN (w_rx_ctl_ibuf), // 1-bit input: Data input from the I/O .INC (1'b0), // 1-bit input: Increment / Decrement tap delay .LD (1'b0), // 1-bit input: Load IDELAY_VALUE input .LDPIPEEN (1'b0), // 1-bit input: Enable PIPELINE register .REGRST (1'b0) // 1-bit input: Active-high reset tap-delay input ); IDDR #( .DDR_CLK_EDGE ("SAME_EDGE_PIPELINED" ), .INIT_Q1 (1'b0 ), .INIT_Q2 (1'b0 ), .SRTYPE ("SYNC" ) ) IDDR_u0 ( .Q1 (w_rec_valid[0] ), // 1-bit output for positive edge of clock .Q2 (w_rec_valid[1] ), // 1-bit output for negative edge of clock .C (w_rxc_bufio ), .CE (1 ), .D (w_rx_ctl_idly ), .R (0 ), .S (0 ) ); always@(posedge w_rxc_bufr) begin if(!i_speed1000 && (&w_rec_valid)) r_cnt_10_100 <= r_cnt_10_100 + 1; else r_cnt_10_100 <= 'd0; end always@(posedge w_rxc_bufr) begin if(&w_rec_valid && i_speed1000) ro_rec_valid <= 'd1; else ro_rec_valid <= r_cnt_10_100; end always@(posedge w_rxc_bufr) begin if(i_speed1000) ro_rec_data <= w_rec_data; else ro_rec_data <= {w_rec_data[3:0],ro_rec_data[7:4]}; end always@(posedge w_rxc_bufr) begin r_rec_valid <= w_rec_valid; end always@(posedge w_rxc_bufr) begin if(!w_rec_valid && r_rec_valid) ro_rec_end <= 'd1; else ro_rec_end <= 'd0; end always@(posedge w_rxc_bufr) begin if(w_rec_valid == 'd0) begin ro_speed <= w_rec_data[2:1]; ro_link <= w_rec_data[0]; end else begin ro_speed <= ro_speed; ro_link <= ro_link ; end end /*---------rgmii send--------*/ always@(posedge w_rxc_bufr) begin ri_send_data <= i_send_data; ri_send_valid <= i_send_valid; end always@(posedge w_rxc_bufr) begin if(i_send_valid) r_tx_cnt_10_100 <= r_tx_cnt_10_100 + 1; else r_tx_cnt_10_100 <= 'd0; end genvar txd_i; generate for(txd_i = 0 ;txd_i < 4 ; txd_i = txd_i + 1) begin assign w_send_d1[txd_i] = i_speed1000 ? i_send_data[txd_i] : r_tx_cnt_10_100 == 0 ? i_send_data[txd_i] : ri_send_data[txd_i + 4]; assign w_send_d2[txd_i] = i_speed1000 ? i_send_data[txd_i + 4] : r_tx_cnt_10_100 == 0 ? i_send_data[txd_i] : ri_send_data[txd_i + 4]; ODDR #( .DDR_CLK_EDGE ("OPPOSITE_EDGE" ), .INIT (1'b0 ), .SRTYPE ("SYNC" ) ) ODDR_u ( .Q (o_txd[txd_i] ), .C (w_txc ), .CE (1 ), .D1 (w_send_d1[txd_i] ), .D2 (w_send_d2[txd_i] ), .R (0 ), .S (0 ) ); end endgenerate assign w_send_valid = i_speed1000 ? i_send_valid : i_send_valid | ri_send_valid; ODDR#( .DDR_CLK_EDGE ("OPPOSITE_EDGE" ), .INIT (1'b0 ), .SRTYPE ("SYNC" ) ) ODDR_uu0 ( .Q (o_tx_ctl ), .C (w_txc ), .CE (1 ), .D1 (w_send_valid ), .D2 (w_send_valid ), .R (0 ), .S (0 ) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

- 175

- 176

- 177

- 178

- 179

- 180

- 181

- 182

- 183

- 184

- 185

- 186

- 187

- 188

- 189

- 190

- 191

- 192

- 193

- 194

- 195

- 196

- 197

- 198

- 199

- 200

- 201

- 202

- 203

- 204

- 205

- 206

- 207

- 208

- 209

- 210

- 211

- 212

- 213

- 214

- 215

- 216

- 217

- 218

- 219

- 220

- 221

- 222

- 223

- 224

- 225

- 226

- 227

- 228

- 229

- 230

- 231

- 232

- 233

- 234

- 235

- 236

- 237

- 238

- 239

- 240

- 241

- 242

- 243

- 244

- 245

- 246

- 247

- 248

- 249

- 250

- 251

- 252

- 253

- 254

- 255

- 256

- 257

- 258

- 259

- 260

- 261

- 262

- 263

- 264

- 265

- 266

- 267

- 268

- 269

- 270

- 271

- 272

- 273

- 274

- 275

- 276

- 277

- 278

- 279

- 280

- 281

- 282

- 283

- 284

- 285

- 286

- 287

- 288

- 289

- 290

- 291

- 292

- 293

- 294

- 295

- 296

- 297

- 298

- 299

- 300

- 301

- 302

- 303

- 304

- 305

- 306

- 307