热门标签

热门文章

- 1鸿蒙开发:深入了解Arkts语言中的Want对象及其运用_arkts want

- 2python表示空类型的关键字_Python中的空值判断

- 3系统设计学习(三)限流与零拷贝

- 4Page_Load不执行_c# webform 代码不进入 page_load

- 5appium下载安装及环境配置及夜神模拟器下载、nodejs安装

- 6tar --exclude用法

- 7Android开发:Android Studio Design界面不显示layout界面的解决方法_android studio没有layout

- 8使用sqlmap 对接口进行json格式参数传入_sqlmap post json

- 9LAPACK的C/C++接口及代码实例_lapack函数库怎么用

- 10鸿蒙会不会跟安卓一样,华为发布“鸿蒙系统”后,安卓系统会不会像WP系统一样消亡?...

当前位置: article > 正文

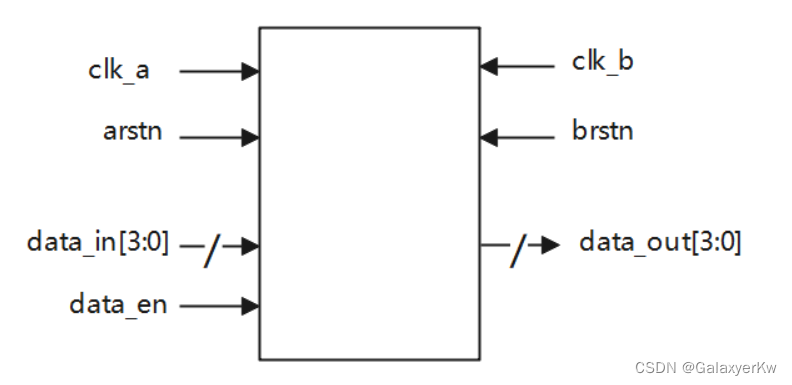

【Verilog】跨时钟域处理(一)——多bit MUX同步_mux同步器

作者:2023面试高手 | 2024-03-07 16:57:46

赞

踩

mux同步器

跨时钟域处理的概念

简单来讲,“跨时钟域处理”即:

①输入和输出的参照时钟不同。

②中间过程的多个步骤会由不同的时钟控制。

跨时钟域处理一般涉及“打拍”,即输入和输出中间空几个时钟周期作为缓冲,其目的在于:

打拍(缓冲)可以减小亚稳态概率。

打拍的经验原则:

一般的,在时钟切换的时候,依照后来的时钟打两拍。

(如由clk_a切换到clk_b,那么需要clk_b先空打两拍,再进行别的操作。)

【详细了解:CDC:跨时钟域处理】

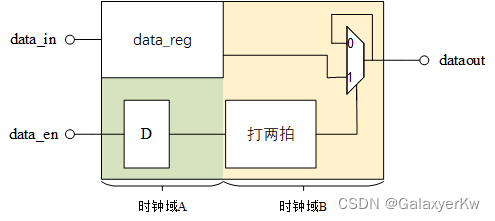

多bit MUX同步的概念和框架

在data_en为高期间,data_in将保持不变,data_en为高至少保持3个B时钟周期。表明,当data_en为高时,可将数据进行同步。data_in端数据变化频率很低,相邻两个数据间的变化,至少间隔10个B时钟周期。

多bit MUX同步 解析

时钟clk_a负责:

① 数据data_in输入时,参照时钟a。(打一拍)

② 使能信号data_en输入时,参照时钟a。(打一拍)

时钟clk_b负责:

① 使能信号data_en延时打两拍,即过两个D触发器。这个过程参照时钟b。

② 数据最终输出dataout,输出时参照时钟b。

多bit MUX同步 代码实现

1. 时钟域clk_a: data_in和data_en寄存。(打一拍)

//clk_a打一拍接受数据和接受使能信号en

reg [3:0] data_reg;

always@(posedge clk_a or negedge arstn)

begin

if(!arstn) data_reg <= 0;

else data_reg <= data_in;

end

reg en_data_reg;

always@(posedge clk_a or negedge arstn)

begin

if(!brstn) en_data_reg <= 0;

else en_data_reg <= data_en; //存入

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

2. 时钟域clk_b: en信号打两拍 + dataout输出

//clk_b负责使能信号en的打拍 reg en_clap_one; //1 reg en_clap_two; //2 always@(posedge clk_b or negedge brstn) begin if(!brstn) en_clap_one <= 0; else en_clap_one <= en_data_reg; //第一拍 end always@(posedge clk_b or negedge brstn) begin if(!brstn) en_clap_two <= 0; else en_clap_two <= en_clap_one; //第二拍 end //clk_b负责输出 always@(posedge clk_b or negedge brstn) begin if(!brstn) dataout <= 0; else dataout <= (en_clap_two) ? data_reg : dataout; end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

完整代码:

module mux( input clk_a , input clk_b , input arstn , input brstn , input [3:0] data_in , input data_en , output reg [3:0] dataout ); /* 跨时钟域传输:输入和输出的参照时钟不同。中间过程的多个步骤会由不同的时钟控制。 本题:clk_a接受数据--->clk_b延时两拍,然后数据才输出。 */ //clk_a打一拍接受数据和接受使能信号en reg [3:0] data_reg; always@(posedge clk_a or negedge arstn) begin if(!arstn) data_reg <= 0; else data_reg <= data_in; end reg en_data_reg; always@(posedge clk_a or negedge arstn) begin if(!brstn) en_data_reg <= 0; else en_data_reg <= data_en; //存入 end //clk_b负责使能信号en的打拍 reg en_clap_one; //1 reg en_clap_two; //2 always@(posedge clk_b or negedge brstn) begin if(!brstn) en_clap_one <= 0; else en_clap_one <= en_data_reg; //第一拍 end always@(posedge clk_b or negedge brstn) begin if(!brstn) en_clap_two <= 0; else en_clap_two <= en_clap_one; //第二拍 end //clk_b负责输出 always@(posedge clk_b or negedge brstn) begin if(!brstn) dataout <= 0; else dataout <= (en_clap_two) ? data_reg : dataout; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/2023面试高手/article/detail/206590

推荐阅读

相关标签