热门标签

热门文章

- 1华为v30鸿蒙系统,荣耀V30怎么升级鸿蒙系统 荣耀V30升级鸿蒙系统步骤教程

- 2libgcc_a挖矿木马应急响应及分析_5.133.65.53

- 3MySql常用函数之 group_concat()、group by、count()、case when then、unin all、instr()、find_in_set()等使用介绍_group concat

- 4uni-app中统一调用接口服务_uniapp小程序中怎么实现每个页面都需要调用同一个接口

- 5‘dependencies.dependency.version‘ for XXX:jar is missing

- 6Huawei LiteOS 概览

- 7uiautomatorviewer闪退、提示Could not create the Java Virtual Machine等问题的处理_启动uiautomatorviewer 报 error: could not create the

- 8【java学习】系统错误处理机制:异常(Exception)、断言(assert)和日志(log)_简述断言(assert)的优缺点

- 9android自动计时器,Android中几种常用的定时器

- 10uniapp中request请求token失效后重新获取token且重新请求_uni-request 监听失败重新发起请求

当前位置: article > 正文

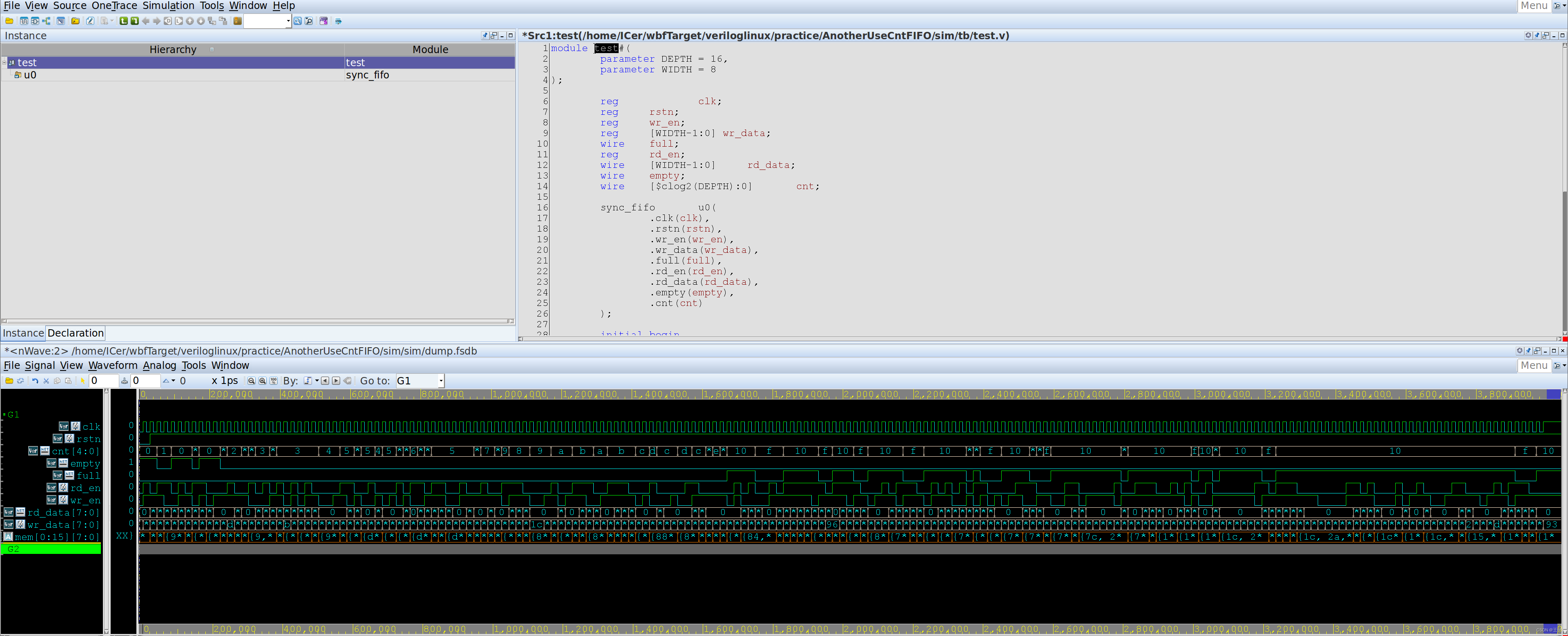

Verilog:同步FIFO使用计数器的写法_fifo写法

作者:从前慢现在也慢 | 2024-03-07 17:52:18

赞

踩

fifo写法

同步FIFO(First in first out),先入先出。

Deign Spec:

- 输入信号:clk;

- 输入信号:异步复位信号:rstn;

- 输入信号:写使能:wr_en;

- 输入信号:写数据:wr_data;//时序逻辑,先判断写使能 wr_en 是否有效,有效情况下如果没有写满,则写入数据,如果满了,判断读使能 rd_en ,如果读使能有效能可以继续写数据。

- 输入信号:读使能:rd_en;

- 输出信号:读数据:rd_data;//时序逻辑,先判断读使能 rd_en 是否有效,有效情况下如果内存非空,则取上一个周期指针位置的数据作为读数据,如果内存为空,则判断写使能,如果写使能有效则直接将写数据 wr_data 作为读数据输出,无效时输出0。

- 输出信号:内存满信号:full;//如果计数器 cnt 等于内存深度,则 full 为1

- 输出信号:内存空信号:empty;//如果计数器 cnt 为0,则 empty 为

- 读指针:rd_ptr;//时序逻辑,先判断写使能 rd_en 是否有效,有效情况如果内存非空则+1,如果内存空了,判断 wr_en 是否有效,如果有效则+1,否则不变。

- 写指针:wr_ptr;//时序逻辑,先判断写使能 wr_en 是否有效,有效情况如果内存非满则+1,如果内存满了,判断 rd_en 是否有效,如果有效则+1,否则不变。

- 内存:mem;//内存深度要为 2^n 大小,即指针可以通过+1自动循环。

- 计数器:cnt;//如果 wr_en 和 rd_en 同时有效,则无论内存空满,cnt不变。如果单纯是 wr_en 有效且非满的情况下,cnt+1,如果单纯是 rd_en 有效且非空的情况下 cnt-1

RTL代码:

- module sync_fifo#(

- parameter DEPTH = 16, //DEPTH = 2^n

- parameter WIDTH = 8

- )(

- input clk,

- input rstn,

-

- //write

- input wr_en, //write enable

- input [WIDTH-1:0] wr_data, //write data

- output full,

-

- //read

- input rd_en, //read enable

- output reg [WIDTH-1:0] rd_data, //read data

- output empty,

-

- output reg [$clog2(DEPTH):0] cnt

- );

-

- reg [$clog2(DEPTH)-1:0] rd_ptr, wr_ptr;

- reg [WIDTH-1:0] mem [0:DEPTH-1];

-

- //********** read start **********//

- always@(posedge clk, negedge rstn) begin

- if(~rstn) begin

- rd_ptr <= 0;

- end

- else if(rd_en && ~empty) begin

- rd_ptr <= rd_ptr + 1'b1;

- end

- else if(rd_en && empty && wr_en) begin

- rd_ptr <= rd_ptr + 1'b1;

- end

- end

-

- always@(posedge clk, negedge rstn) begin

- if(~rstn) begin

- rd_data <= 0;

- end

- else if(rd_en && ~empty) begin

- rd_data <= mem[rd_ptr];

- end

- else if(rd_en && empty && wr_en) begin

- rd_data <= wr_data;

- end

- else begin

- rd_data <= 0;

- end

- end

- //********** read end **********//

-

- //********** write start **********//

- always@(posedge clk, negedge rstn) begin

- if(~rstn) begin

- wr_ptr <= 0;

- end

- else if(wr_en && ~full) begin

- wr_ptr <= wr_ptr + 1'b1;

- end

- else if(wr_en && full && rd_en) begin

- wr_ptr <= wr_ptr + 1'b1;

- end

- end

-

- always@(posedge clk) begin

- if(wr_en && ~full) begin

- mem[wr_ptr] <= wr_data;

- end

- else if(wr_en && full && rd_en) begin

- mem[wr_ptr] <= wr_data;

- end

- end

- //********** write end **********//

-

- //********** cnt **********//

- always@(posedge clk, negedge rstn) begin

- if(~rstn) begin

- cnt <= 0;

- end

- else if(wr_en && rd_en) begin

- cnt <= cnt;

- end

- else if(wr_en && ~full) begin

- cnt <= cnt + 1'b1;

- end

- else if(rd_en && ~empty) begin

- cnt <= cnt - 1'b1;

- end

- end

-

- assign full = (cnt == DEPTH);

- assign empty = (cnt == 0);

-

- endmodule

TB代码:

- module test#(

- parameter DEPTH = 16,

- parameter WIDTH = 8

- );

-

- reg clk;

- reg rstn;

- reg wr_en;

- reg [WIDTH-1:0] wr_data;

- wire full;

- reg rd_en;

- wire [WIDTH-1:0] rd_data;

- wire empty;

- wire [$clog2(DEPTH):0] cnt;

-

- sync_fifo u0(

- .clk(clk),

- .rstn(rstn),

- .wr_en(wr_en),

- .wr_data(wr_data),

- .full(full),

- .rd_en(rd_en),

- .rd_data(rd_data),

- .empty(empty),

- .cnt(cnt)

- );

-

- initial begin

- clk = 0;

- rstn = 0;

- wr_en = 0;

- wr_data = 0;

- rd_en = 0;

- #30 rstn = 1;

- end

-

- always #10 clk = ~clk;

-

- always@(posedge clk) begin

- if(({$random()}%16)<10) wr_en <= 1;

- else wr_en <= 0;

- if(({$random()}%16)<7) rd_en <= 1;

- else rd_en <= 0;

- end

-

- always@(posedge clk) begin

- wr_data <= {$random()} & 8'hff;

- end

-

- initial begin

- #4000 $finish;

- end

-

- endmodule

波形:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/从前慢现在也慢/article/detail/206798

推荐阅读

相关标签