热门标签

热门文章

- 1Ubuntu密码忘记怎么办 Ubuntu重置root密码方法_ubuntu忘记root密码

- 2Homebrew介绍和使用

- 3文本分类任务(weibo_senti_100k为数据集)

- 4VSCode 开发C/C++实用插件分享——codegeex_vscode c/c++ ai助手 gee

- 5Python的自定义模块和调用方法___all__ = ['__version__']

- 6【uCOS-II学习笔记1】启动、创建任务、优先级获取、任务调度_os_meminit 函数参数

- 7mysql里Date类型的处理_mysql date

- 8MongoDB中GridFS的文件删除、备份、导入、合并(释放磁盘空间)及重建索引(mongodump/mongorestore/compat/reindex)

- 9jenkins+git+maven+nodejs安装(linux系统)

- 10远程代码托管平台--GitHub、Gitee的使用

当前位置: article > 正文

Vivado+Vitis操作流程(Hello World例程)_vivado vitis

作者:2023面试高手 | 2024-04-12 02:42:01

赞

踩

vivado vitis

一、Vivado端

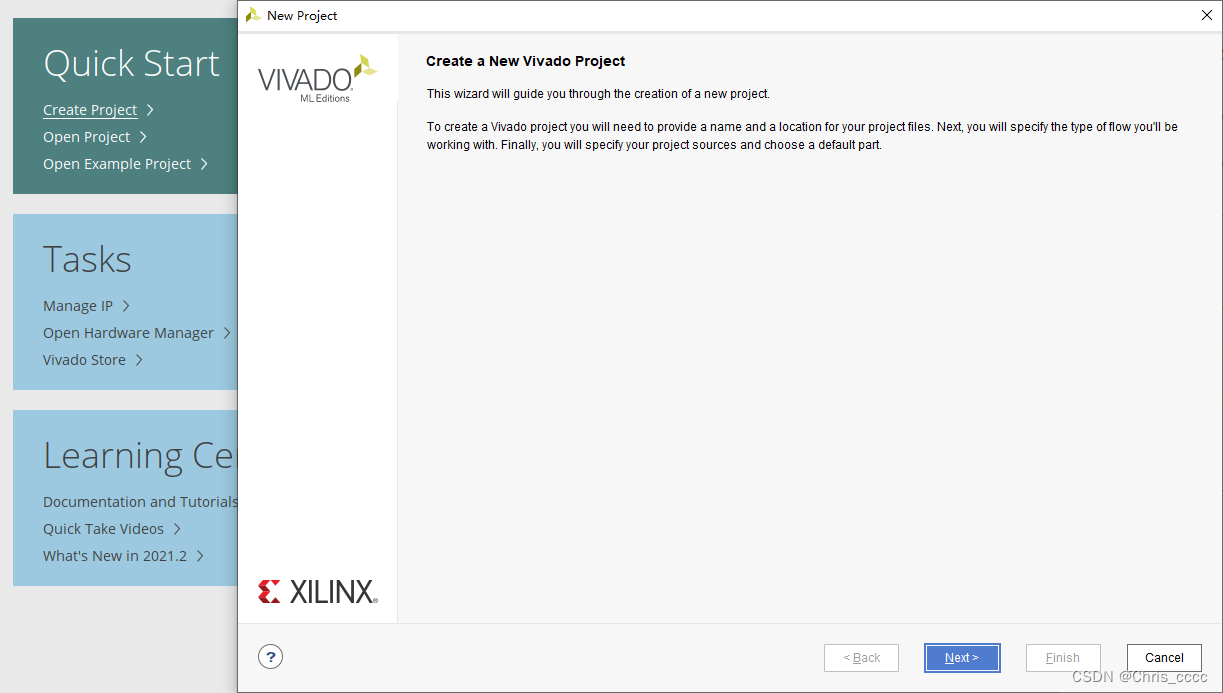

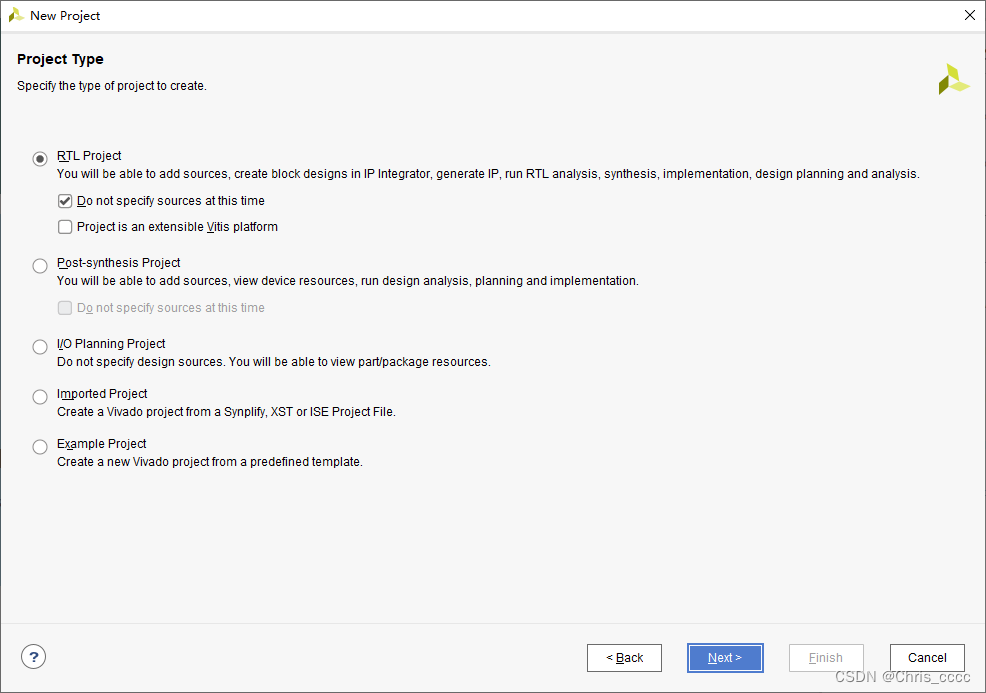

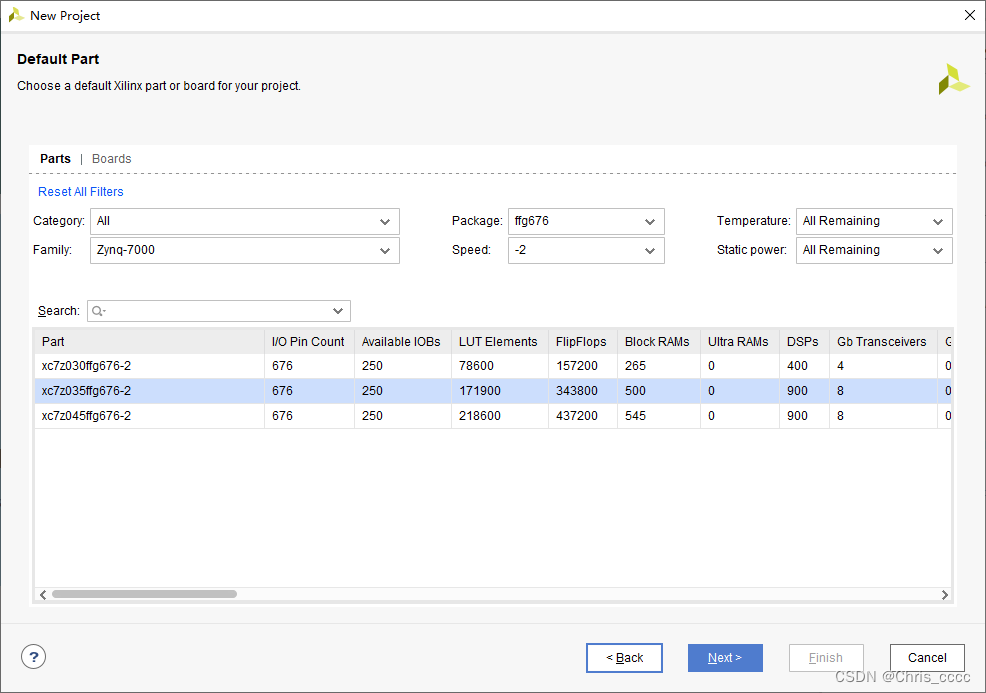

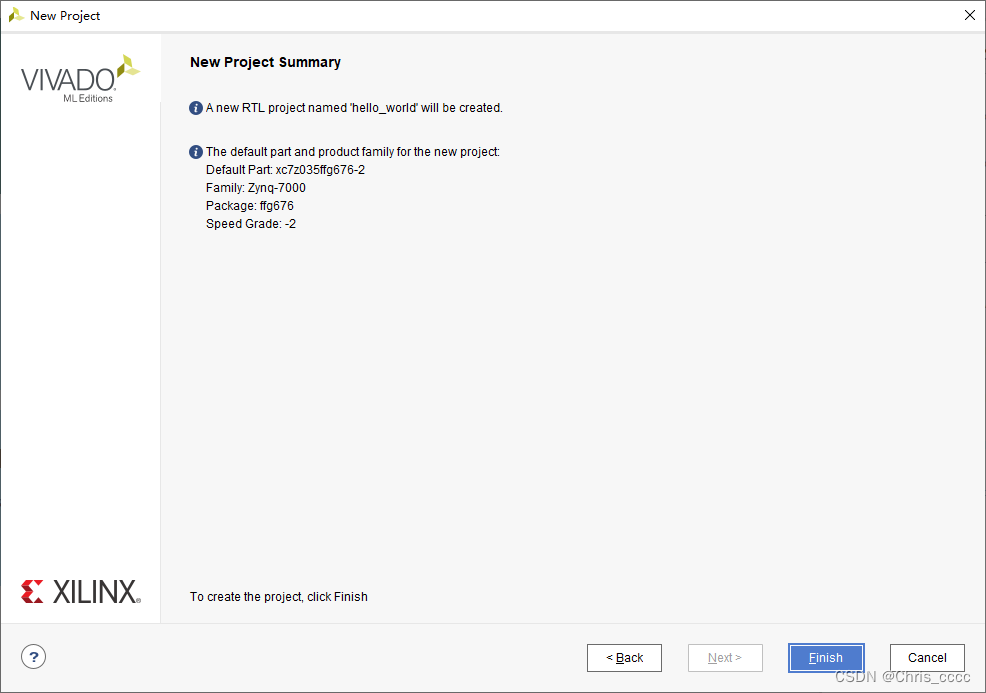

1. 新建Vivado工程

- 新建工程【Create Project】【Next>】

- 工程命名并选择保存路径【Next>】

- 工程类型【Next>】

- 根据自身需要选择器件型号【Next>】

- 工程信息 确认信息无误【Finish】

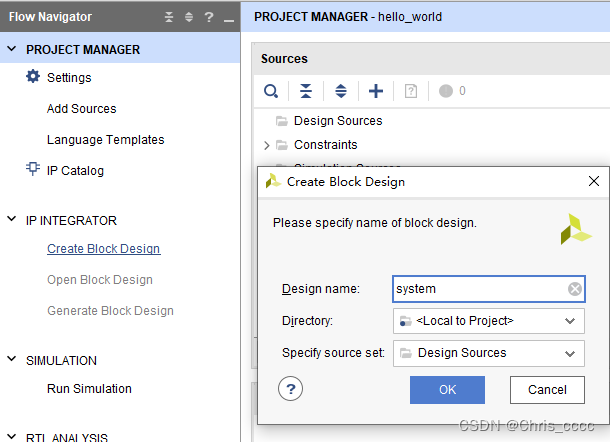

2. 新建Block Design文件

- 【Create Block Design】修改名称【OK】

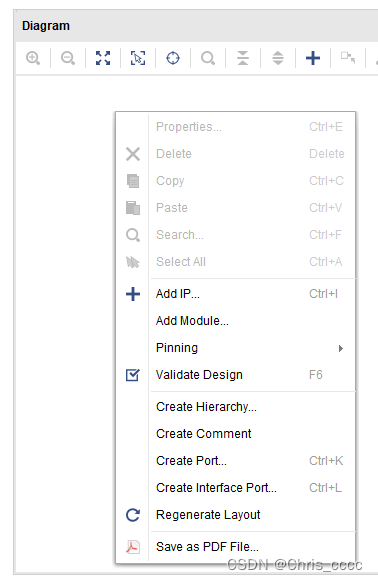

- 打开Diagram窗口 右击空白处或ctrl+i【Add IP...】

- 添加需要的ZYNQ7 Processing System

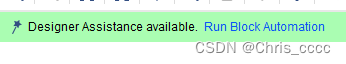

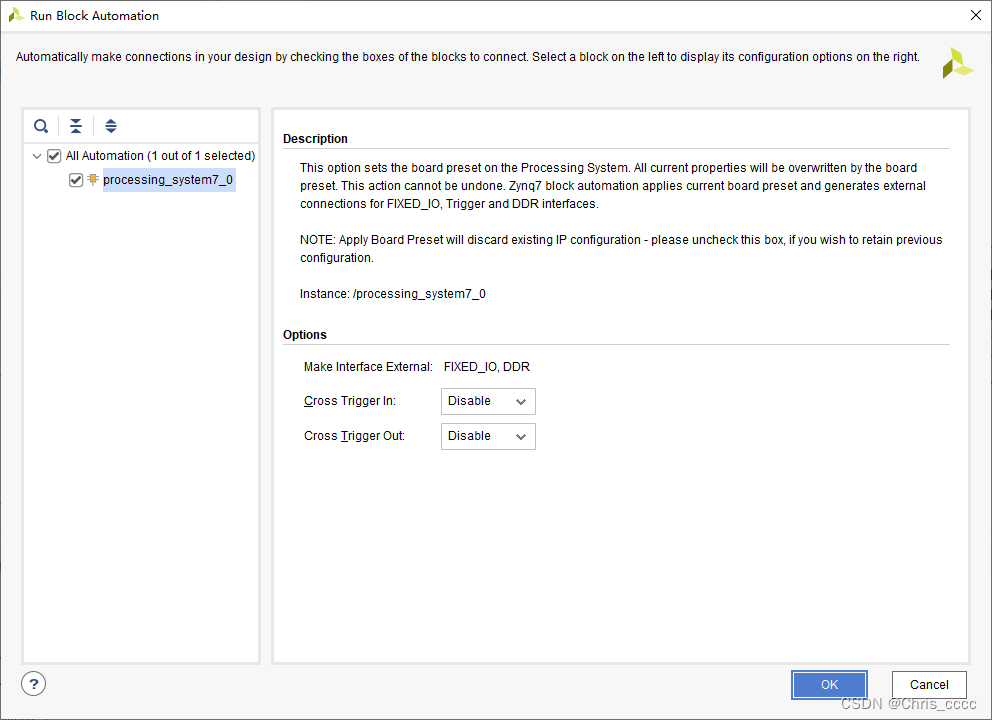

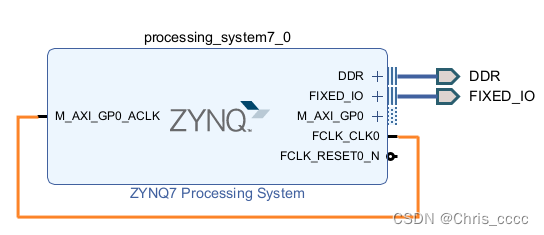

- 自动连线【Run Block Automatic】【OK】

- 手动连接M_AXI_GP0_ACLK和FCLK_CLK0

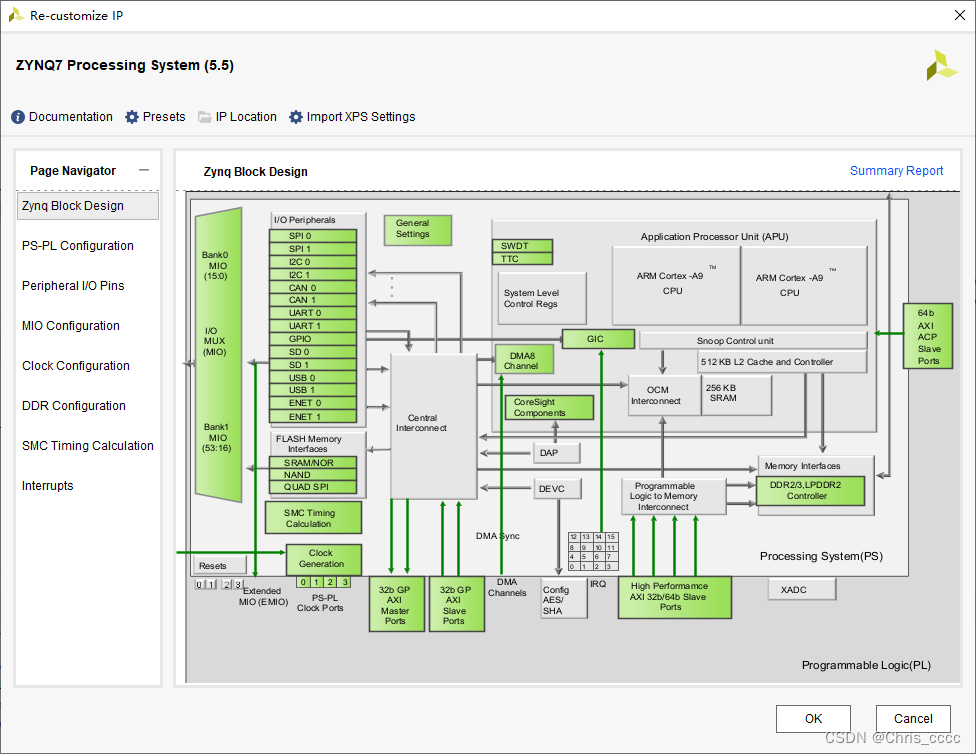

- 双击ZYNQ 器件进入配置界面 根据需要进行配置【OK】

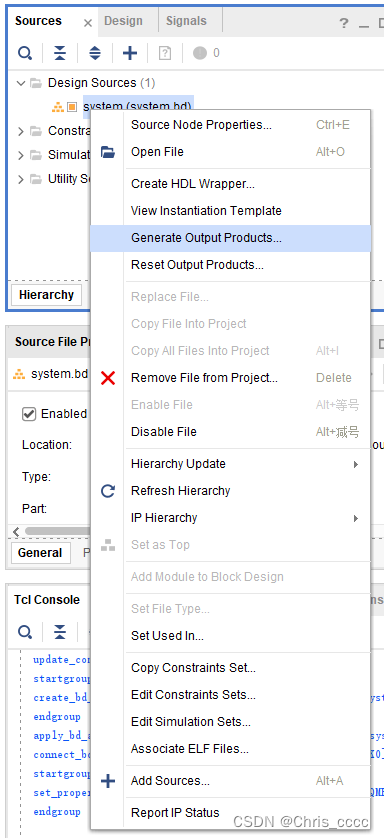

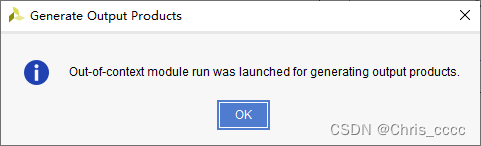

- Sources窗口找到.bd文件 右击选择【Generate Output Products...】

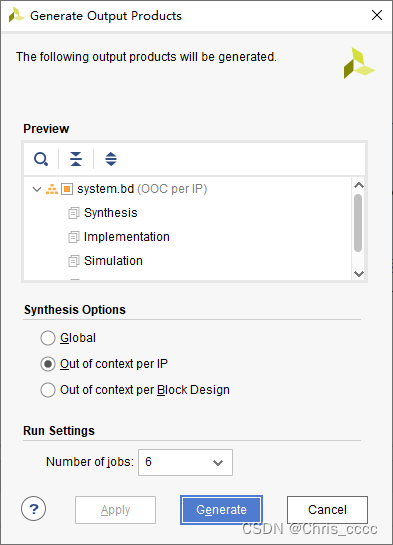

- 【Generate】

- 【OK】

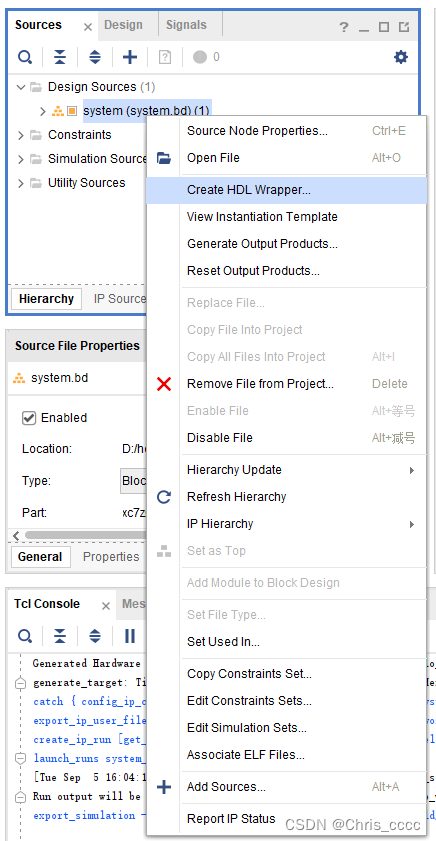

- Sources窗口找到.bd文件 右击选择【Create HDL Wrapper...】

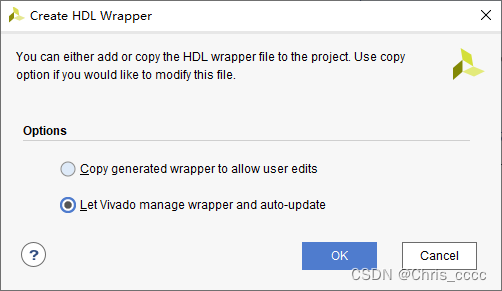

- 勾选【Let Vivado manage wrapper and auto-update】【OK】

3. 工程编译并生成比特流

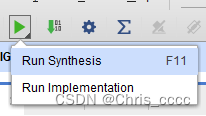

- 运行【Run Synthesis】

- 生成比特流【Generate Bitstream】

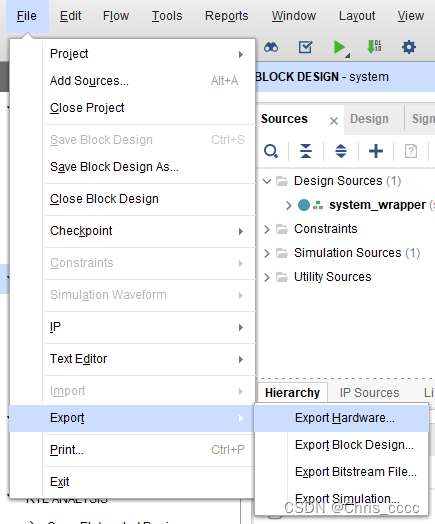

- 导出硬件【Export Hardware...】

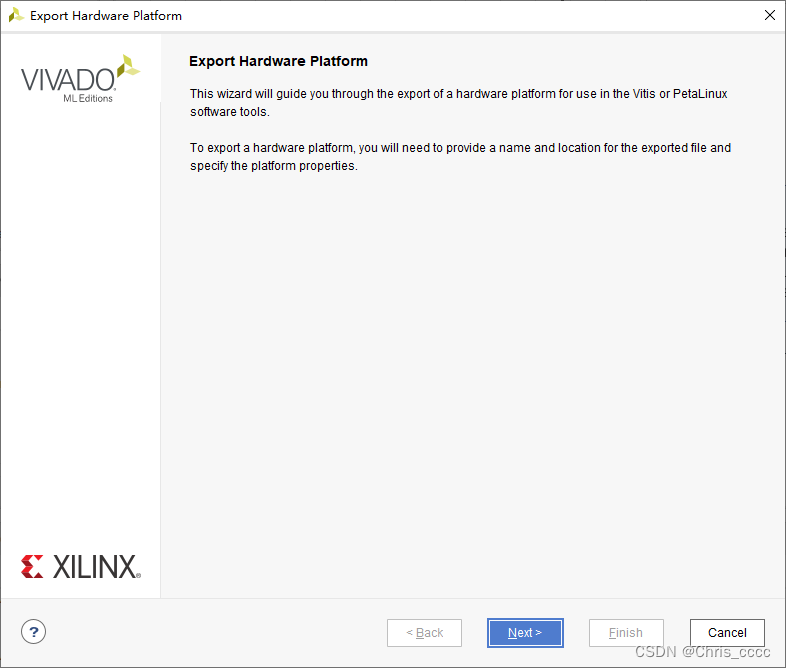

- 导出硬件平台(Vitis and PetaLinux)【Next>】

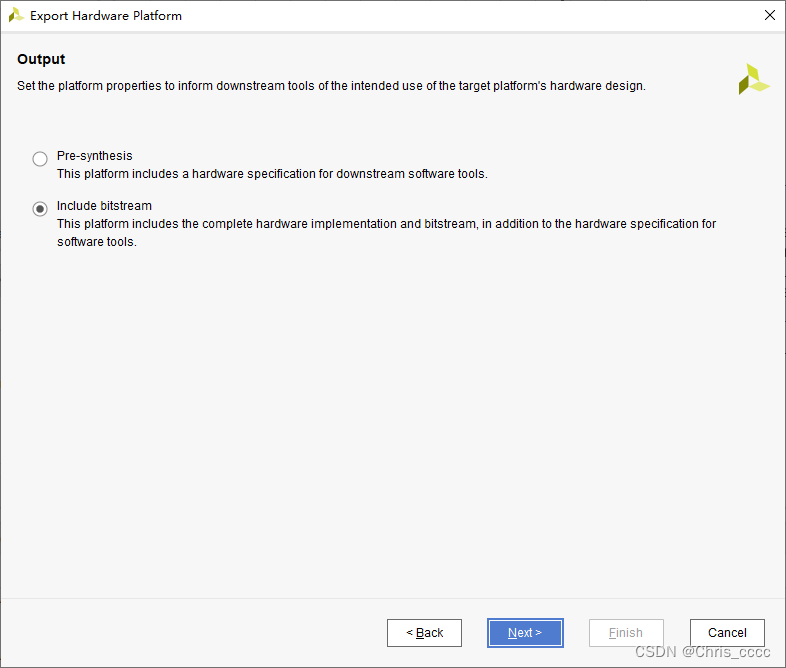

- 输出 勾选【Include bitstream】【Next>】

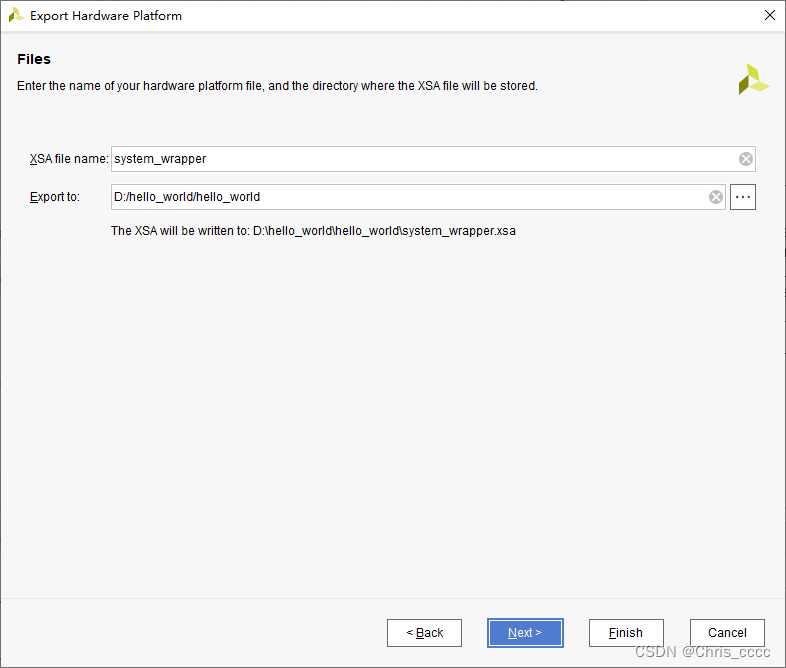

- 命名并为生成的.xsa文件设置存放路径【Next>】

- 信息【Finish】

二、Vitis端

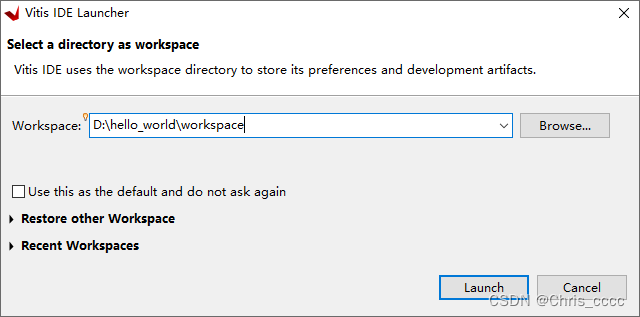

- 打开Vitis(内部打开:Tools->Launch Vitis IDE)

- 设置工作路径【Launch】

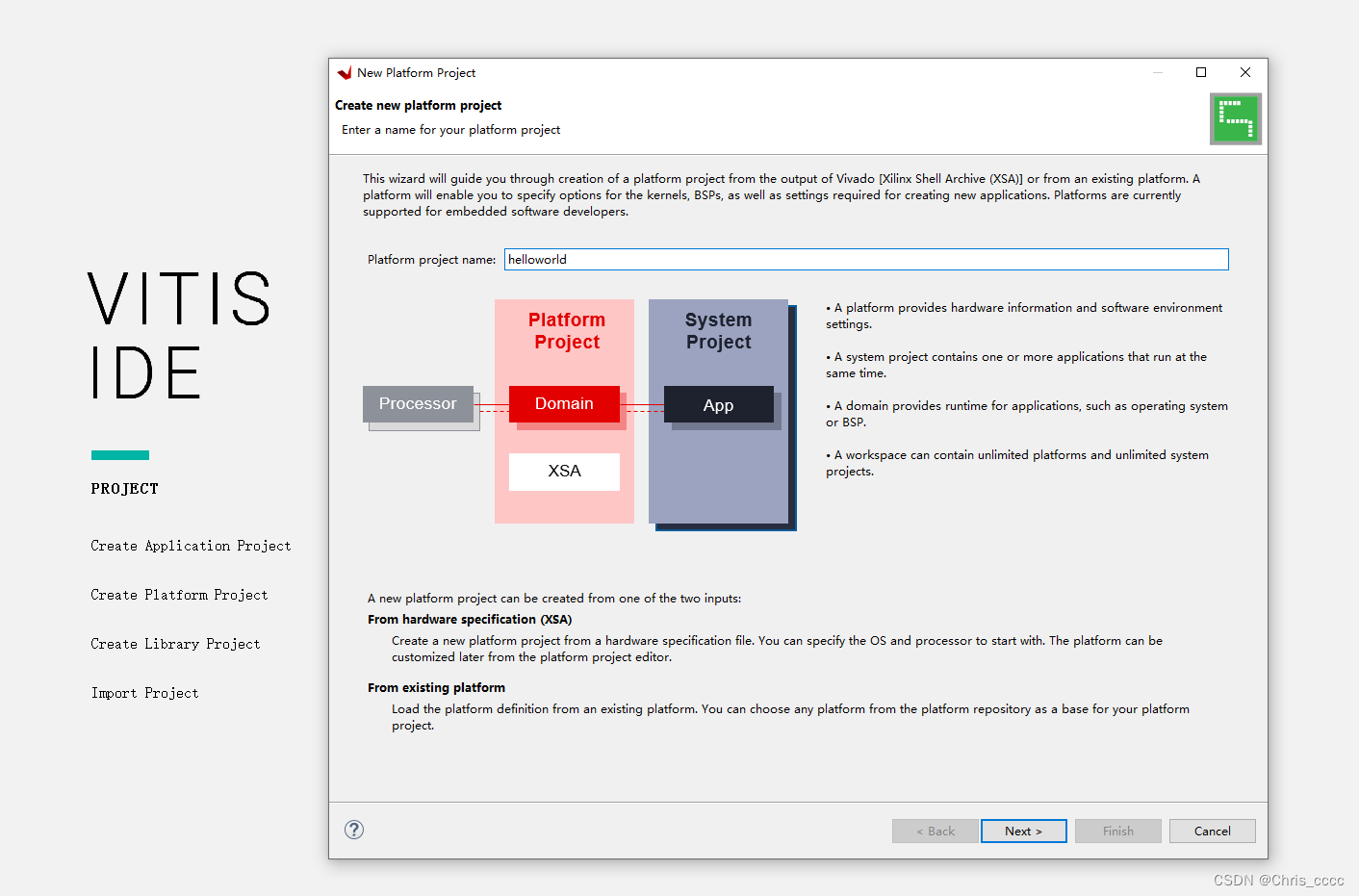

1. 新建平台工程

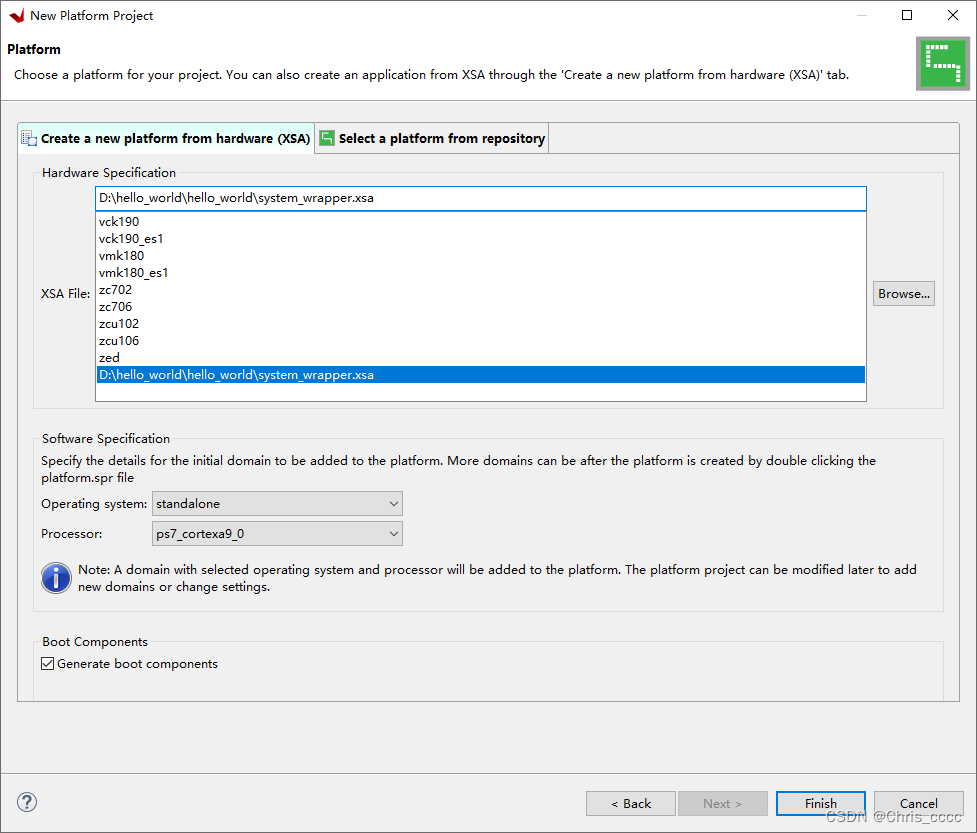

- 【Create Platform Project】为平台项目命名【Next>】

- 【Browse】选择刚才生成的.xsa文件【Finish】

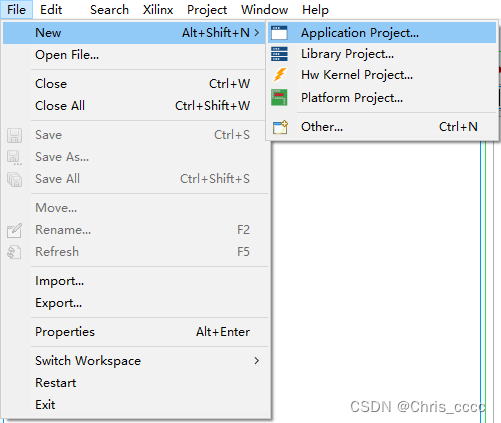

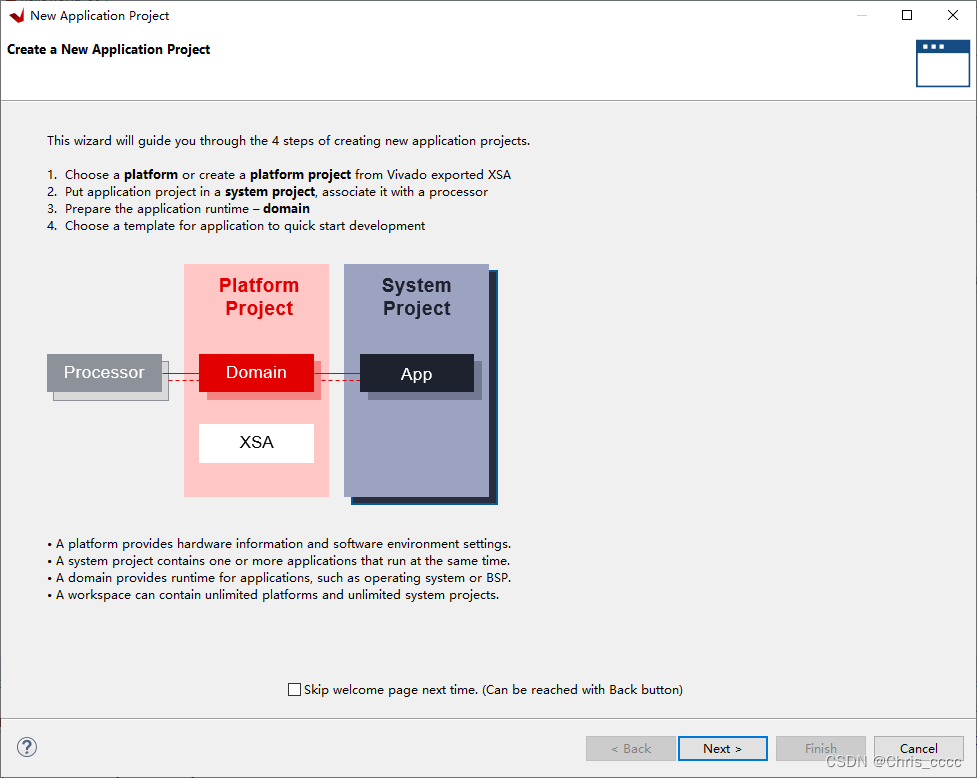

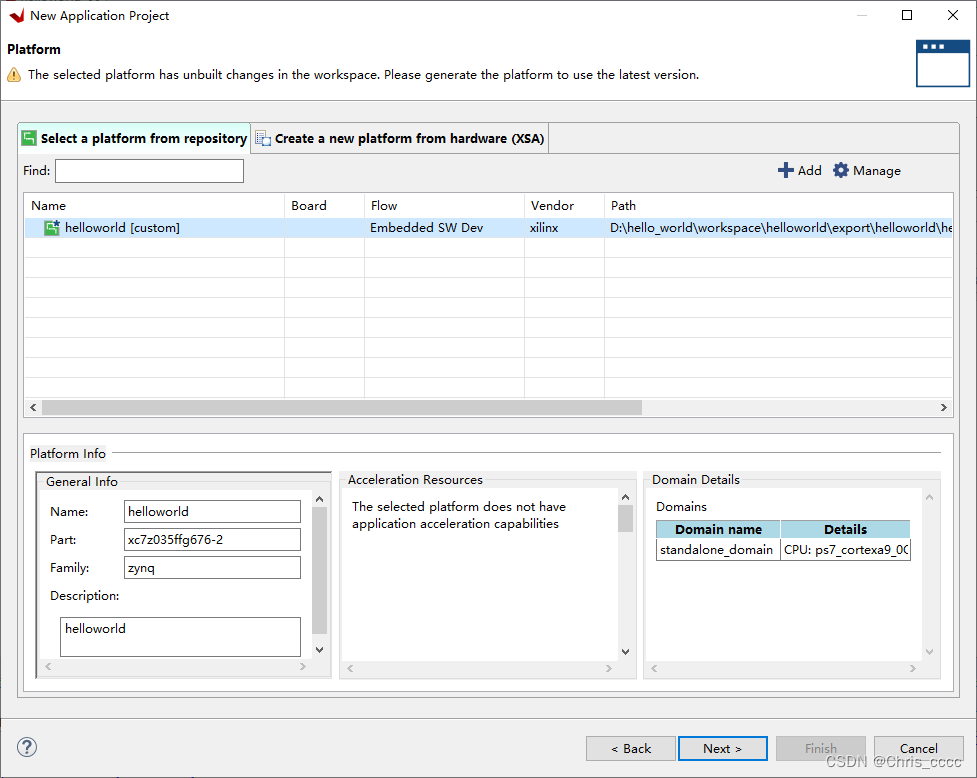

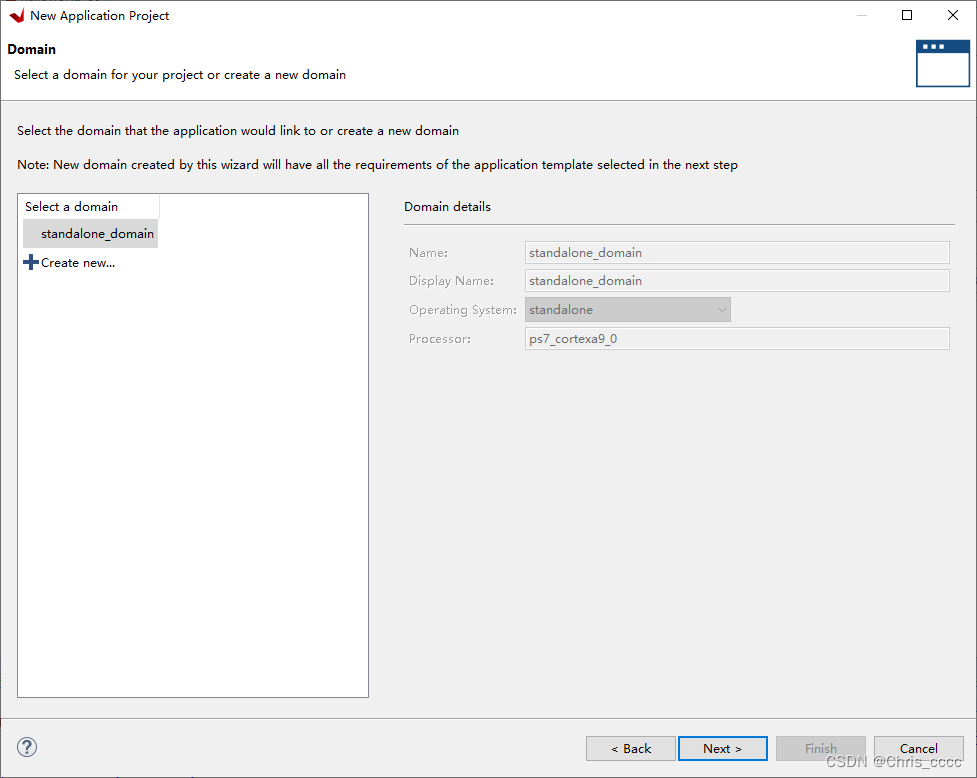

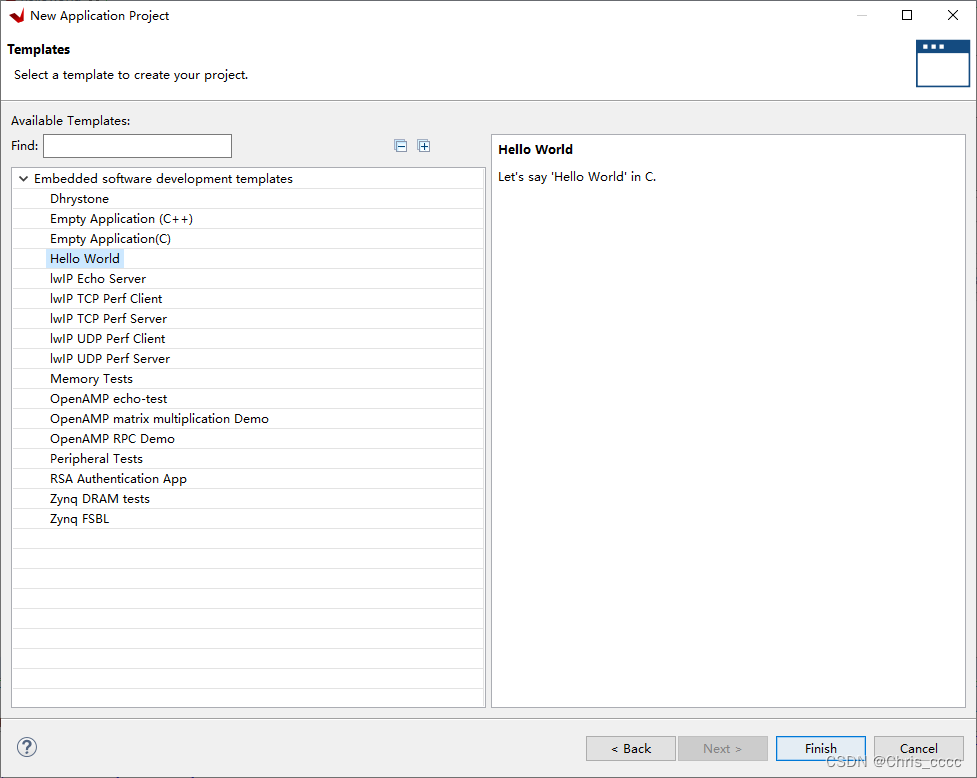

2. 新建应用工程

- 【Next>】

- 选择helloworld 【Next>】

- 命名 【Next>】

- 【Next>】

- 选择Hello World 【Finish】

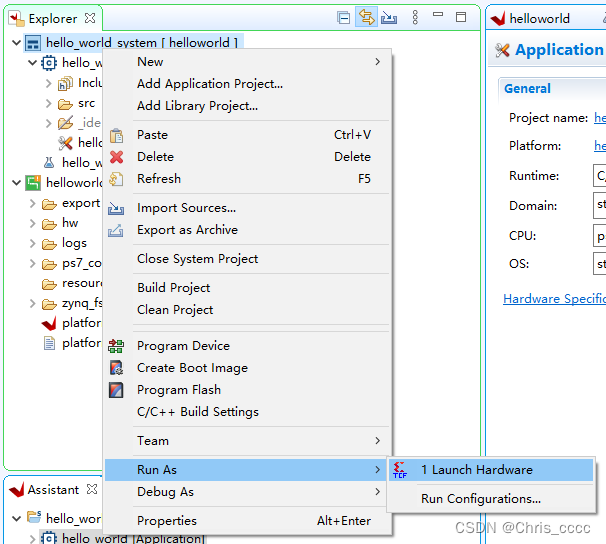

3. 运行验证

- 右击hello world工程进行编译 【1 Launch Hardware】

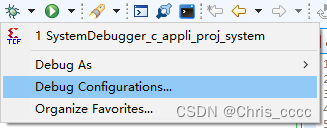

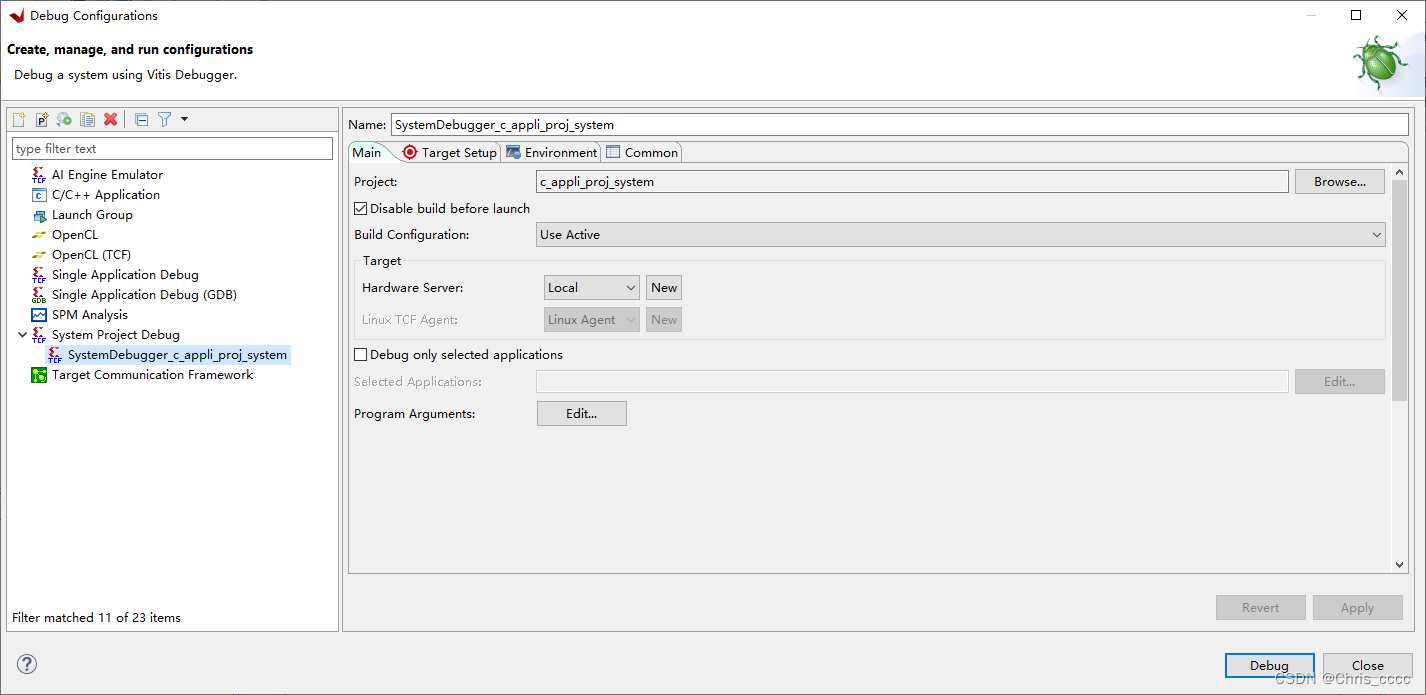

- 【Debug Configurations...】

- 【Debug】 注意此处应该在System Project Debug下

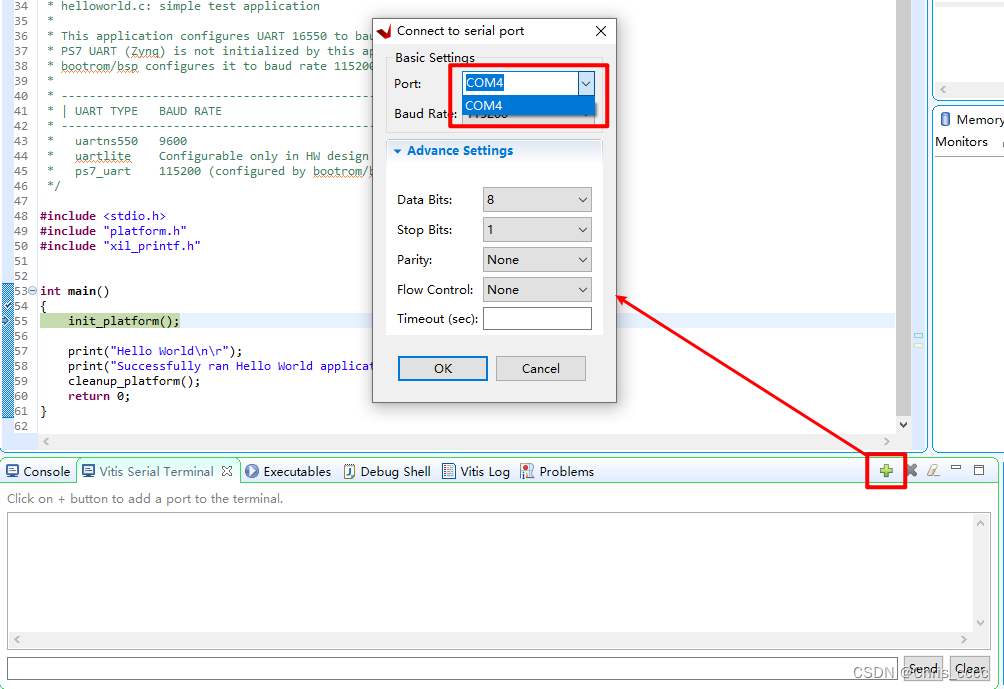

- 打开Vitis Serial Terminal 配置接口信息 【OK】

- Resume 运行

- 运行结果如下

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/2023面试高手/article/detail/408810?site

推荐阅读

相关标签