- 1爬虫scrapy_scrapy爬虫

- 2GitHub 无法访问?这里有神器级解决方案_github 访问不了

- 3【ubuntu20.04】安装GeographicLib

- 4接口01_精通Postman接口测试基础应用_appkey和app-secret在进行api请求时怎么用 postman

- 5NLP实战 | BERT文本分类及其魔改(附 Python 代码)_bert文本分类实战(附代码讲解)

- 6C语言中的数据结构--链表的应用2(3)

- 7【SpringCloud深入浅出系列】SpringCloud组件之集成Hystrix Dashboard_springcloud整合hystrix-dashboard

- 8基于SpringBoot+Vue的二手图书交易系统(源码+文档+部署+讲解)_二手图书交易系统java源码vue

- 9Windows应用程序设计基础(常用控件3)_windows控件

- 10独立看门狗和窗口看门狗_窗口狗

FPGA学习4-Vivado和Vitis学习_vivado vitis

赞

踩

1、vivado上建立工程(FPGA学习3)

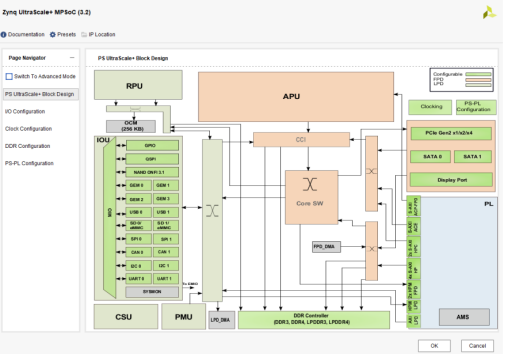

2、点击“Create Block Design”,创建一个 Block 设计,即图形化设计,弹出对话框名字Design name尽量简短,否则在 Windows 下编译会有问题。

![]()

3、点击“+”(Add IP),搜索IP核,我的开发板是zynq,找到IP核后双击这个IP核,在左侧的窗口进入编辑,参考xilinx的ug1085。

下面的配置是根据硬件原理图来设置。

4、在 I/O Configuration 窗口,配置BANK电压,如配置 BANK0~BANK2 电压为 LVCMOS18,BANK3 电压为 LVCMOS33。根据模块上的硬件配置来配置 Low Speed 管脚,如开发板上用QSPI,勾选 QSPI,并设置为”Single”模式,Data Mode 为”x4“,勾选 Feedback Clk。

5、勾选 SD 1,配置 SD 卡。选择 MIO 46..51(MIO为多功能IO口,根据硬件原理图上连接),Slot Type 选择 SD 2.0,Data Transfer Mode 选择 4Bit,勾选 CD,用于检测 SD 卡插入,选择 MIO45;勾选 I2C 1,用于 EEPROM 等的 I2C,选择 MIO 32..33;勾选串口 UART 1,选择 MIO 24..25;勾选 TTC 0~TTC 3(独立通道的计数器)。

6、High Speed 部分首先配置 PS 端以太网,勾选 GEM 3,选择 MIO 64..75,勾选 MDIO 3,选择 MIO 76..77;勾选 USB 0,选择 MIO 52..63,勾选 USB 3.0,选择 GT Lane1(原理图上MGTR1,MGT0给PCIE);USB reset 选share mio,avtive low usb0里选 MIO 44

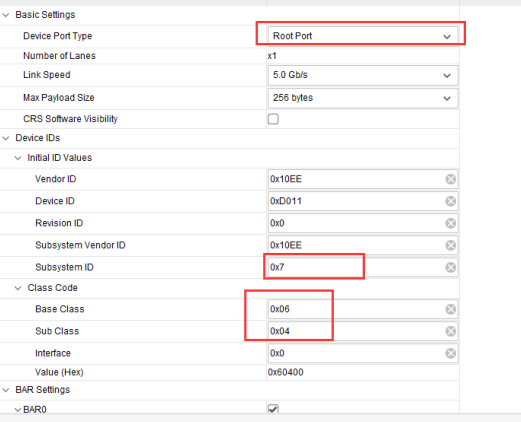

7、勾选PCIE,endpoint mode reset选MIO37,勾选 Switch To Advanced Mode,在PCIe Configuration进行配置

8、时钟配置

在 Clock Configuration 界面,Input Clocks 窗口配置参考时钟,其中 PSS_REF_CLOCK 为 ARM

的参考时钟默认为 33.333MHz;PCIe 选择 Ref Clk0,100MHz;Display Port 选择 Ref Clk2,

27MHz;USB0 选择 Ref Clk1,