热门标签

热门文章

- 1CSS字体样式属性调试_"cssstyle(\"font-size:20px\")"

- 2浅谈最广泛应用的金融风控算法-评分卡_xgboost, iv, woe

- 3Android Studio如何通过结合SQLite数据库实现简单的注册,登录功能。_android之利用sqlite实现登陆和注册

- 4使用HanLP进行分词和实体抽取_hanlp分词

- 5 Live回顾 | 氪信张伟:基于核心AI技术的银行信贷风控与反欺诈应用 ...

- 6B站【千锋】Linux云计算基础视频教程_650集完全入门 课堂笔记_千峰云计算笔记

- 7go mod tidy引入私有仓库包时报错terminal prompts disabled_go mod tidy could not read username for

- 8单片机毕设分享 基于单片机的智能盲人头盔系统 - 导盲杖 stm32_单片机 头盔

- 9【独家源码】ssm更美个人美妆穿搭分享微信小程序95827应对计算机毕业设计困难的解决方案_微信小程序 换装 源码

- 10网络安全与密码学--AES加密

当前位置: article > 正文

SystemVerilog Assertions应用指南 第一章(1.25章节 “first_match”运算符)_systemverilog的assertion first_match

作者:2023面试高手 | 2024-04-19 22:19:34

赞

踩

systemverilog的assertion first_match

任何时候使用了逻辑运算符(如“and”和“or”)的序列中指定了时间窗,就有可能出现同一个检验具有多个匹配的情况。“ first match”构造可以确保只用第一次序列匹配,而丢弃其他的匹配。当多个序列被组合在一起,其中只需时间窗内的第一次匹配来检验属性剩余的部分时,“ first match”构造非常有用。

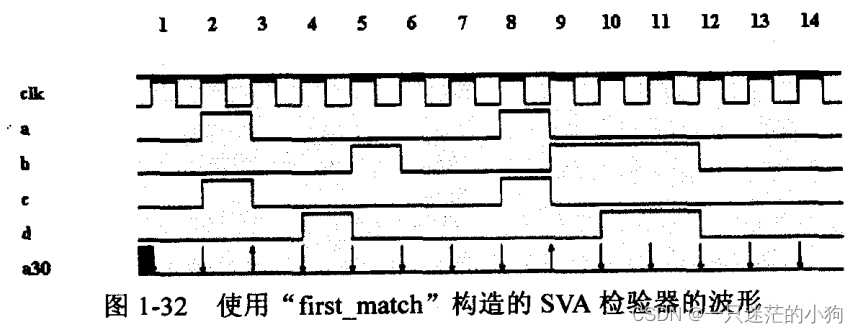

当检验属性p30时,第一次匹配保留下来,其他匹配都被丢弃了。

- sequence s30a;

- @(posedge clk) a ##[1:3] b;

- endsequence

-

- sequence s30b;

- @(posedge clk) c ##[2:3] d;

- endsequence

-

- property p30_fm;

- @(posedge clk) first_match(s30a or s30b);

- endproperty

-

- property p30;

- @(posedge clk) s30a or s30b;

- endproperty

-

- a30: assert property(p30);

- a30_fm: assert property(p30_fm);

在上面的例子中,属性用运算符“or”将两个序列组合在起。这个属性的几个可能的匹配如下所示。

- a ##1 b;

- a ##2 b;

- a ##3 b;

- c ##2 d;

- c ##3 d;

图1-32显示了属性p30在模拟中的响应。图中显示了两次成功,分别在时钟周期3和9在时钟周期3的成功基于序列(c##2d)的匹配。在时钟周期9的成功基于序列(a##1b)的匹配。在这两种情况中,第一次序列匹配就使得整个属性成功。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/2023面试高手/article/detail/453905

推荐阅读

相关标签