热门标签

热门文章

- 1java毕业设计区块链内容创作平台(Springboot+mysql+jdk1.8+maven3.39)

- 2Redis 多线程网络模型全面揭秘

- 3易基因|干货:m6A RNA甲基化MeRIP-seq测序分析实验全流程解析

- 4从关于用例规约与详细设计的讨论看待对规范的采纳_用例规约表写在详细设计

- 5HarmonyOS实战开发-实现一个计步器卡片应用_harmony系统运动怎么添加计时器

- 6JavaScript快速基础入门_javascript 快速入门总结

- 7source导入sql脚本报错:Failed to open file_source fail to open file

- 8JDK1.8源码之HashMap(二)——插入及扩容

- 9Open3D(C++)点云处理算法汇总(C++长期更新版)_open3d c++

- 10【大数据Hive】hive 多字段分隔符使用详解_hive字段分隔符

当前位置: article > 正文

3线8线译码器74LS138设计VHDL代码74138_74ls138译码器verilog代码

作者:2023面试高手 | 2024-05-13 12:10:34

赞

踩

74ls138译码器verilog代码

名称:3线8线译码器74LS138设计

软件:QuartusII

语言:VHDL

代码功能:

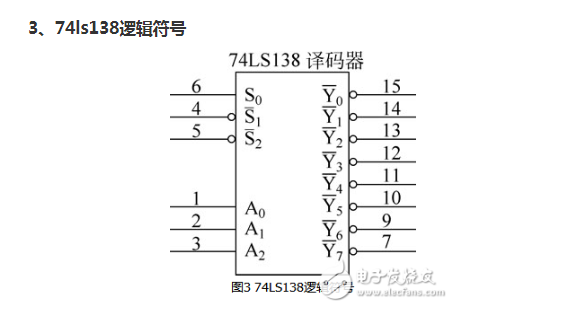

3线8线译码器74LS138的设计

使用VHDL代码

74138

FPGA代码Verilog/VHDL代码资源下载网:www.hdlcode.com

代码下载:

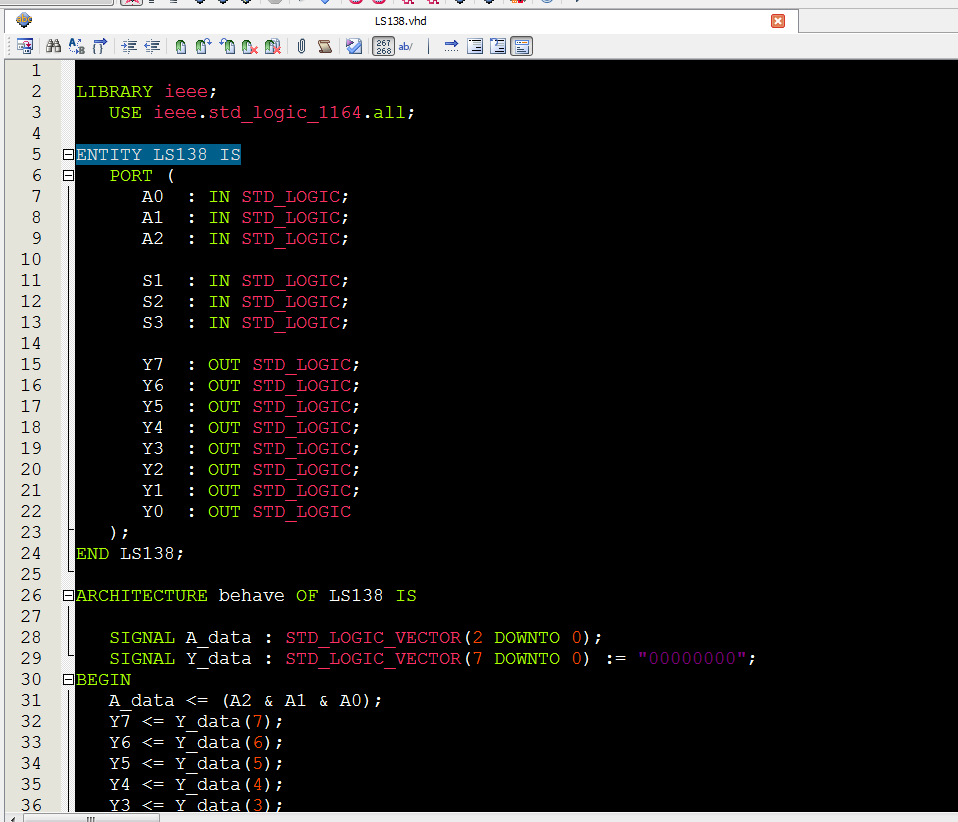

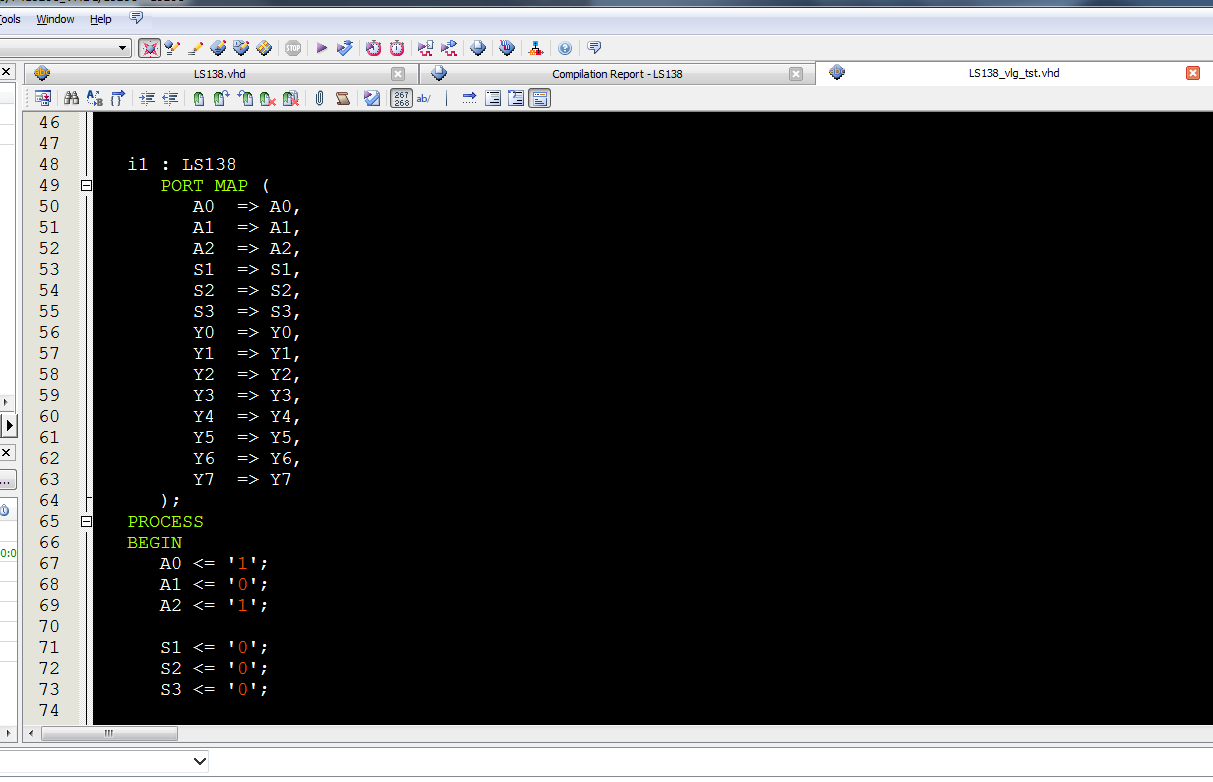

部分代码展示

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY LS138 IS PORT ( A0 : IN STD_LOGIC; A1 : IN STD_LOGIC; A2 : IN STD_LOGIC; S1 : IN STD_LOGIC; S2 : IN STD_LOGIC; S3 : IN STD_LOGIC; Y7 : OUT STD_LOGIC; Y6 : OUT STD_LOGIC; Y5 : OUT STD_LOGIC; Y4 : OUT STD_LOGIC; Y3 : OUT STD_LOGIC; Y2 : OUT STD_LOGIC; Y1 : OUT STD_LOGIC; Y0 : OUT STD_LOGIC ); END LS138; ARCHITECTURE behave OF LS138 IS SIGNAL A_data : STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL Y_data : STD_LOGIC_VECTOR(7 DOWNTO 0) := "00000000"; BEGIN A_data <= (A2 & A1 & A0); Y7 <= Y_data(7); Y6 <= Y_data(6); Y5 <= Y_data(5); Y4 <= Y_data(4); Y3 <= Y_data(3); Y2 <= Y_data(2); Y1 <= Y_data(1); Y0 <= Y_data(0); PROCESS (S1, S2, S3, A_data) BEGIN

设计文档:

1.功能要求

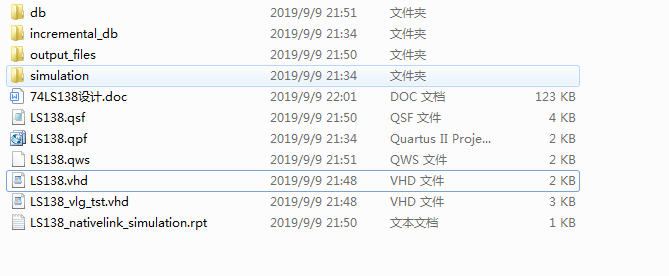

2.工程文件

3.程序文件

4.程序编译

5.仿真程序(testbench)

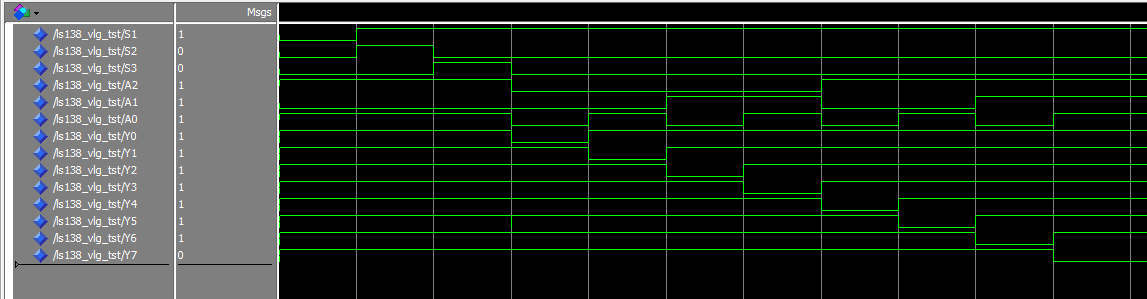

6.仿真图

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/2023面试高手/article/detail/563569

推荐阅读

相关标签