热门标签

热门文章

- 1C++对于内联函数(inline)的初步理解_在h文件中需要加inline

- 2unity动画初始为首帧_unity实现物体停留在第一帧,点击物体播放视频

- 3机器学习与信息安全

- 4树莓派 ubuntu 18 安装pybluez问题_树莓派安装pybluez 失败

- 5MBTI测试大解析:探索性格与职业的最佳搭配,助力职场成功!_mbti活动策划

- 6LangChain:LLM应用程序开发(上)——Models、Prompt、Parsers、Memory、Chains_chain = prompt | model | stroutputparser()

- 7kafka-消费基础_kafka 消费

- 8MySQL8初始化报错 --Data Dictionary initialization failed

- 9智能车摄像头采集原理_智能车ccd图像采集

- 10Matlab GUI下基于Gabor+SVM与PCA+SVM的人脸识别比较

当前位置: article > 正文

【ADC&FPGA】基于ZCU102+FMCJESDADC1的数据采集项目之篇(2):阶段目标

作者:2023面试高手 | 2024-05-29 18:33:50

赞

踩

【ADC&FPGA】基于ZCU102+FMCJESDADC1的数据采集项目之篇(2):阶段目标

(1)为什么要分阶段?

如前篇所述,终极目标是:通过纯FPGA控制把FMCJESDADC1子板上的2路ADC数据采集到FPGA内部,并对采集到的数据做解调处理。

但客观现实是:

- FMCJESDADC1上的AD9517时钟芯片、AD9520 ADC芯片及FPGA的JESD接口都没有调试过,没有现成的配置。调试过程必然需要不断修改AD9517、AD9520 、JESD各种配置。如果将配置固化在RTL中,必然调试效率很低。

- ADI参考工程的上述配置都通过软件完成,软件各种封装又很厚,需要花时间消化。且最终项目的目标是纯RTL来控制,并不需要在CPU上跑软件。

基于上述考虑,本项目分2个阶段完成。

(2)使用PetaLinux辅助调试阶段

本阶段的方案是:使用ZYNQ PS系统并允许Petalinx系统,将AD9517、AD9520、JESD控制器当做PS系统的外设。通过Linux串口即可下读写指令即可完成对AD9517、AD9520、JESD控制器的配置和状态回读,得到配置脚本。

这种方式极大提高调试效率且门槛最低。

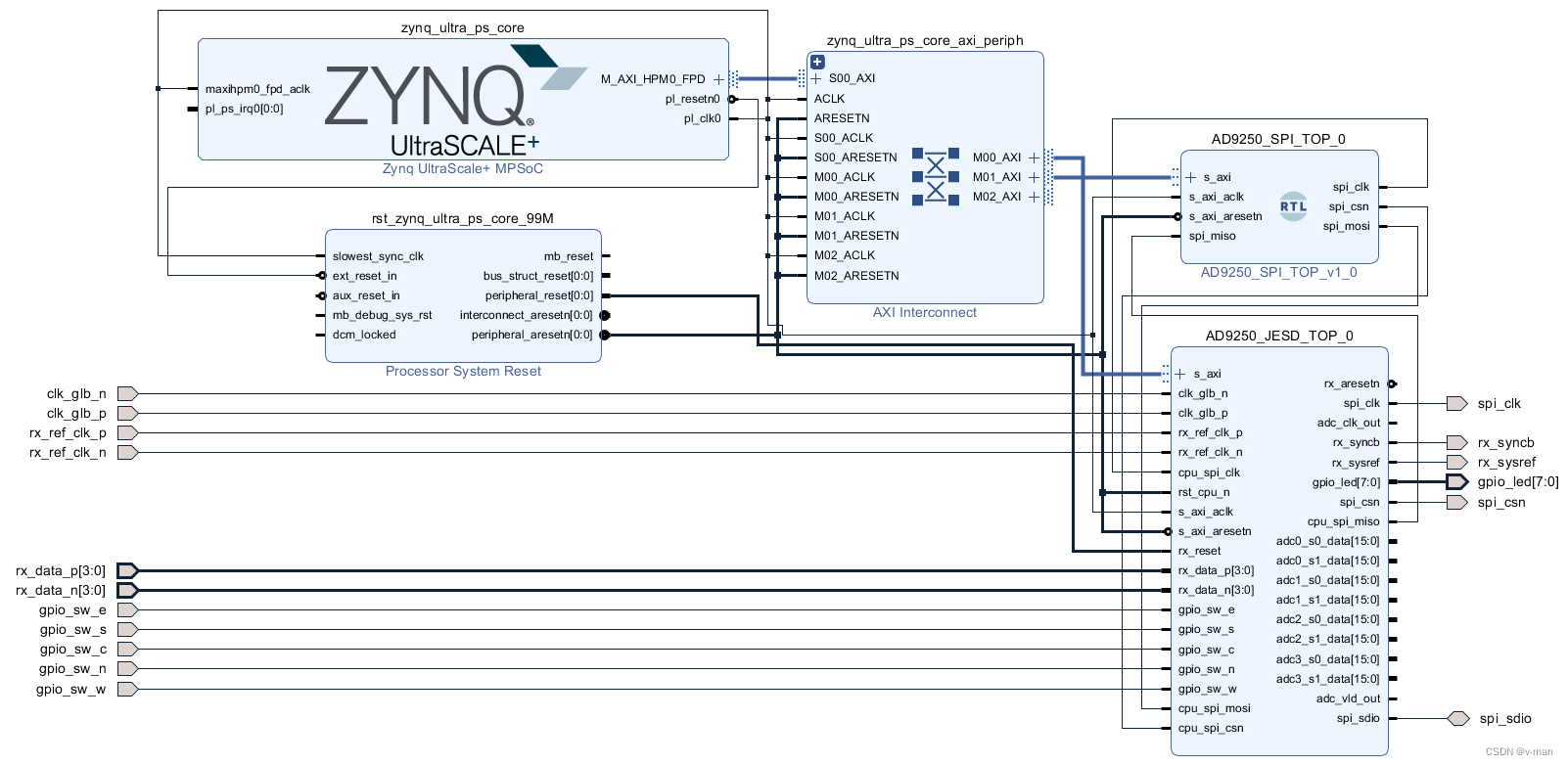

本阶段的系统架构如下:

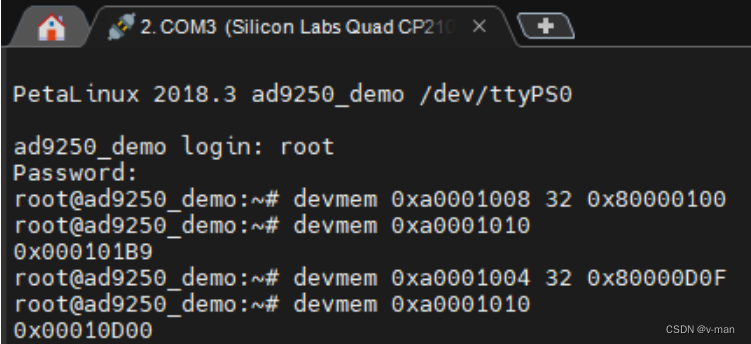

读写调试示例:

(3)使用纯RTL控制阶段

阶段(2)是为了得到所有正确的配置和流程,但最终的目标我们并不需要依赖这个处理器及配置脚本,而是纯RTL控制即可工作,这样对FPGA平台的依赖和资源使用最少。

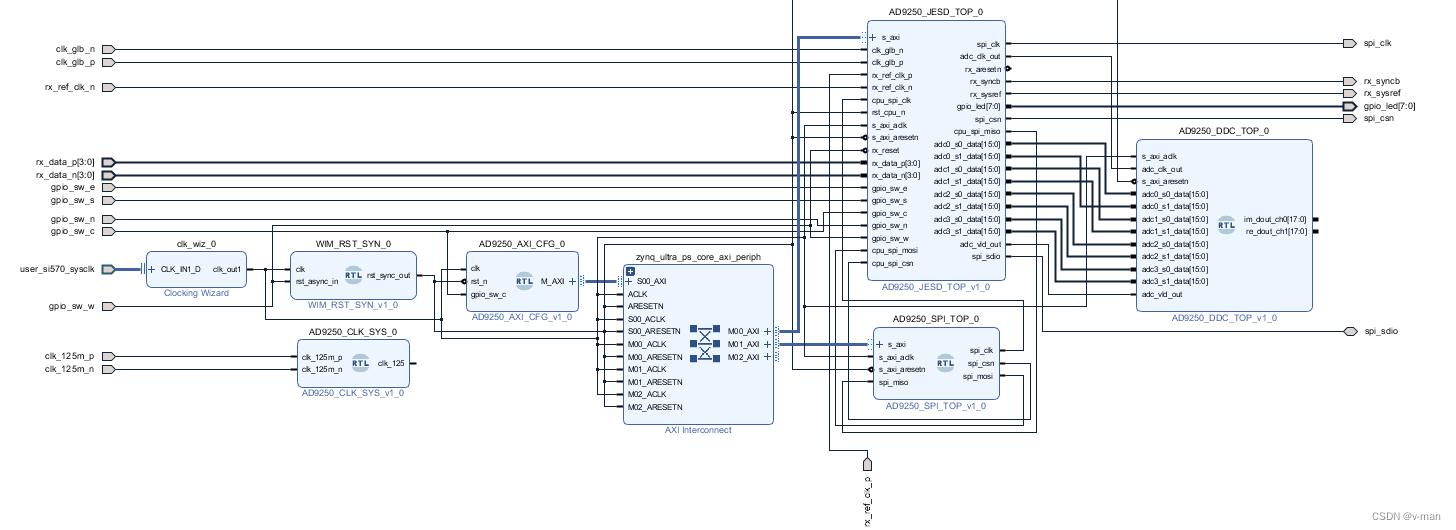

本阶段将配置脚本固化封装为一个AXI Master,只需要将该AXI Master替换掉原来PS系统的AXI Master端口。这便于移植到其它FPGA平台。

本阶段的系统架构如下:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/2023面试高手/article/detail/643535

推荐阅读

相关标签