- 1到底如何理解文本?一文读懂命名实体识别(实体消歧和实体统一)_文本实体识别

- 2Spark实战:词频统计_spark实时词频统计处理系统实战

- 3Python递归爬取今日头条指定用户一个月内发表的所有文章,视频_今日头条爬虫

- 4力扣随机一题 6/28 数组/矩阵

- 5C#中字段、属性、只读、构造函数赋值、反射赋值的相关

- 6error: exportArchive: No signing certificate “iOS Distribution“ found_no signing certificate "ios distribution" found

- 7SpringCloud全家桶 (第四期:Zuul网关之ZuulFilter过滤器)_zuulfilter执行顺序

- 82345恶意篡改修复_dh2345.top

- 9大模型的高考数学成绩单:及格已经非常好了

- 10Postman 还能做自动化接口测试?早学会早下班!

FPGA编程入门_quartus怎么生成rtl图

赞

踩

一、基于Quartus件完成一个1位全加器的设计,分别采用:1)原理图输入 以及 2)Verilog编程 这两种设计方法。开发板基于Intel DE2-115。

原理图实现1位全加器

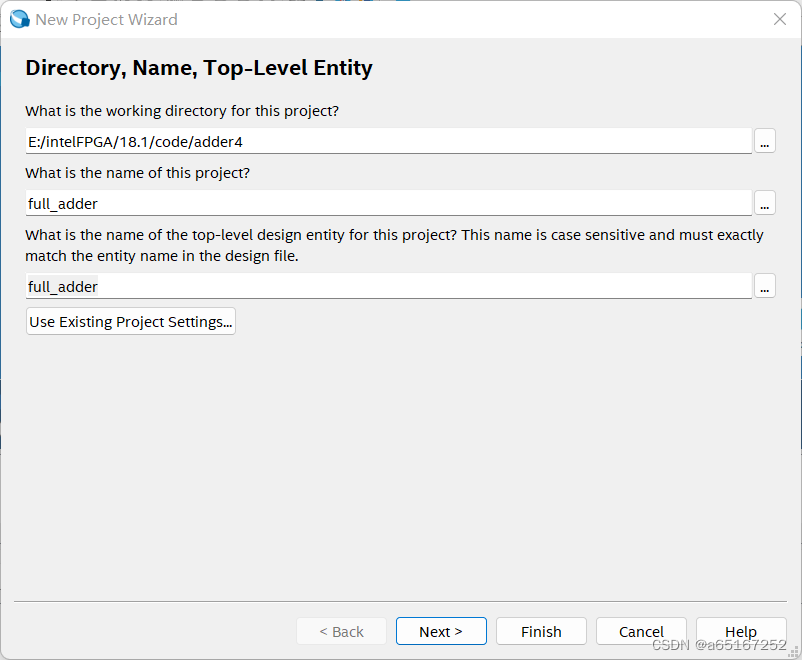

1.创建项目

2.选择文件夹 取项目名字

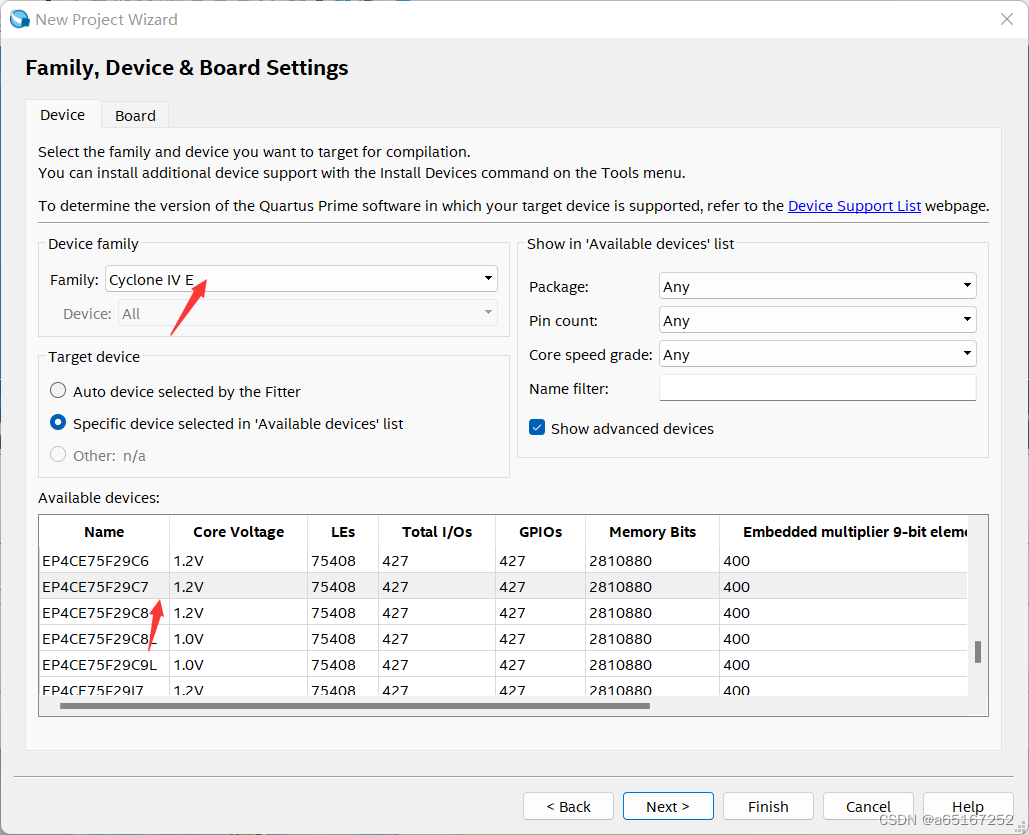

3.选择芯片

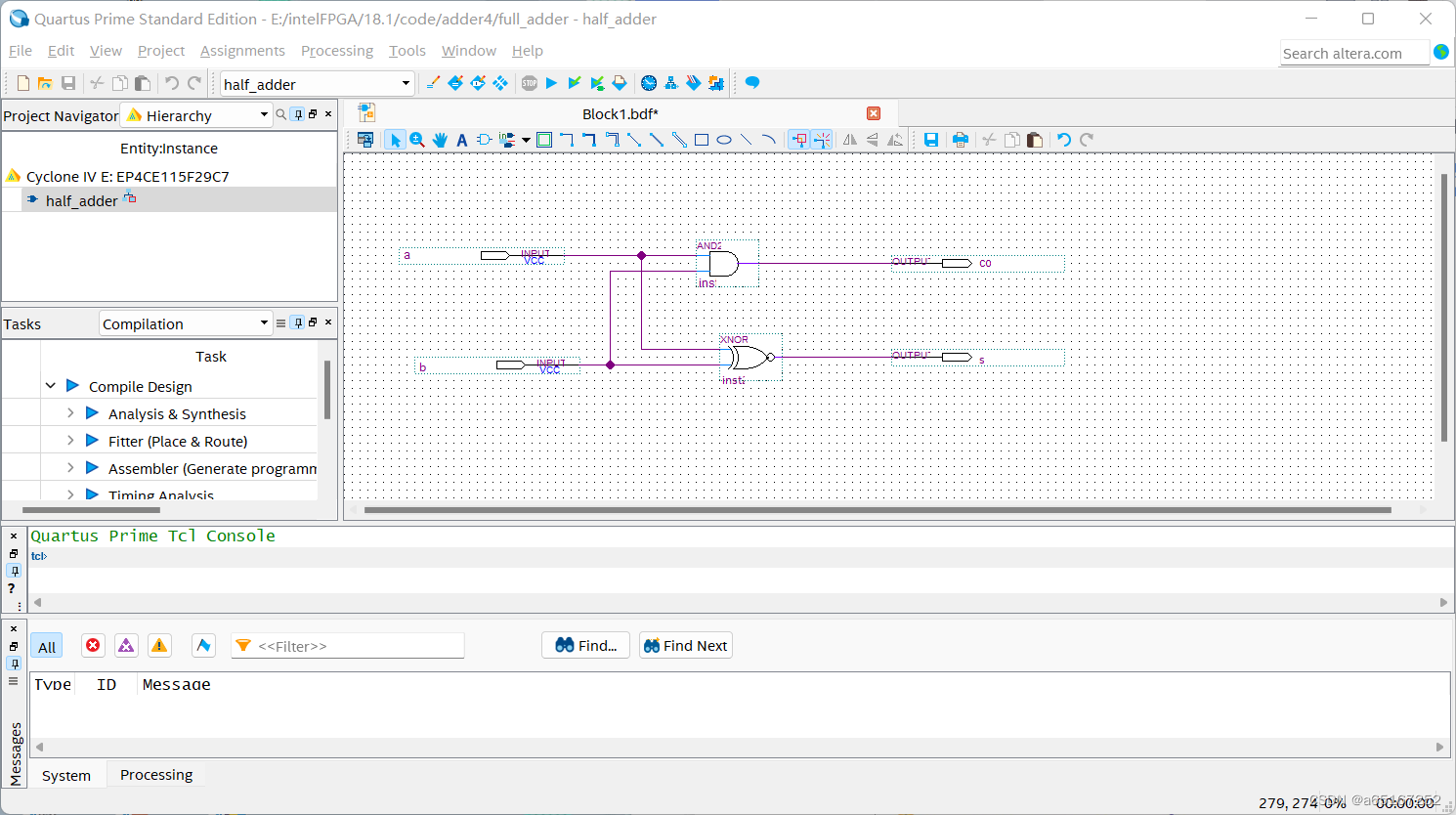

4.输入半加器原理图

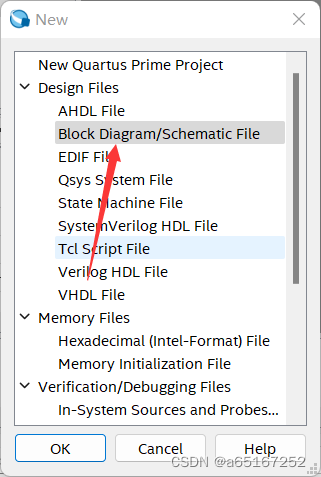

选择file,然后点击new

5.添加元件

完成原理图

6.保存然后编译

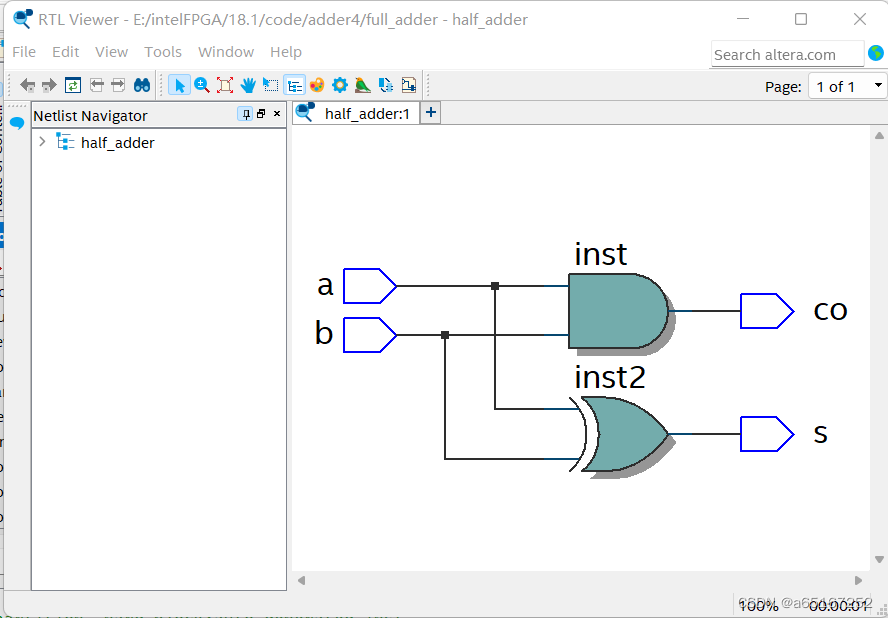

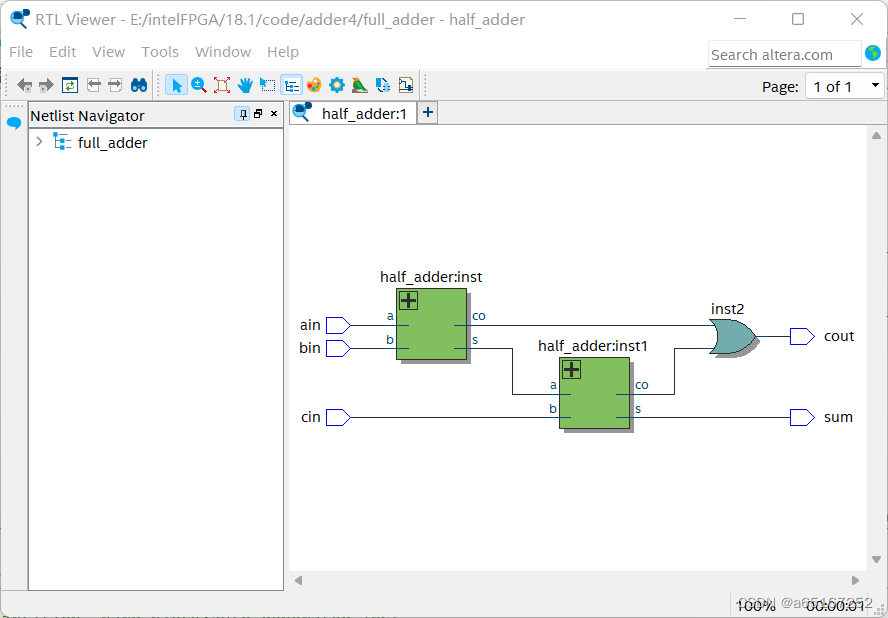

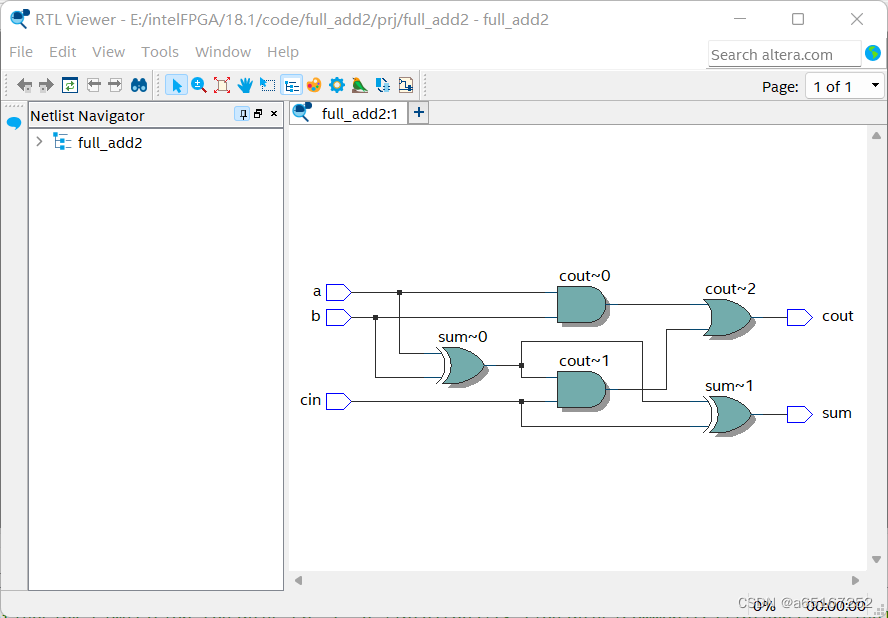

RTL图:

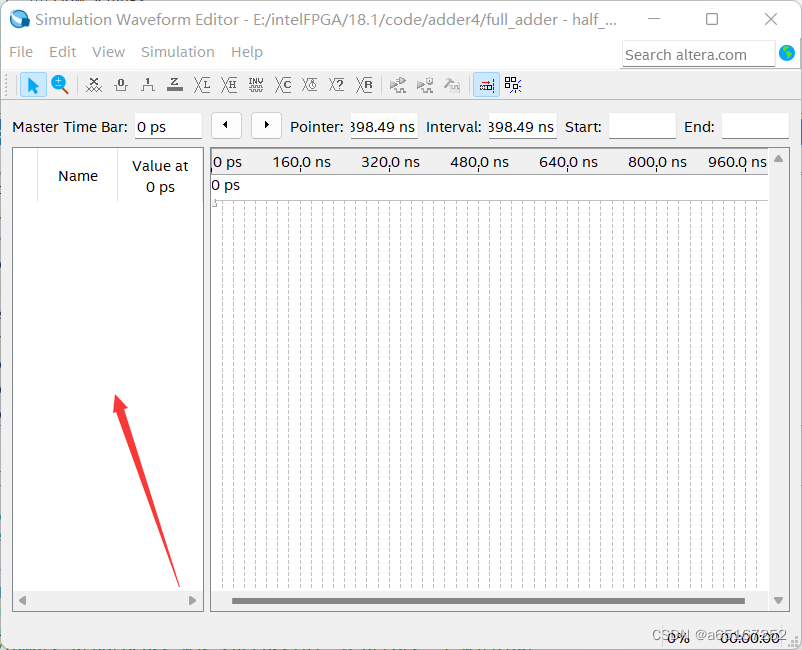

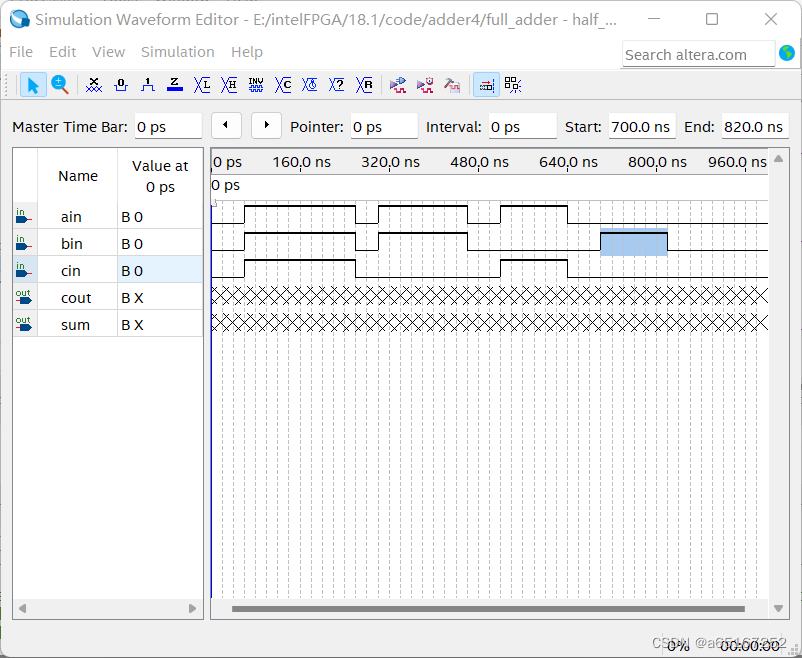

7.创建一个向量波形文件,点击new选择

点击空白区域

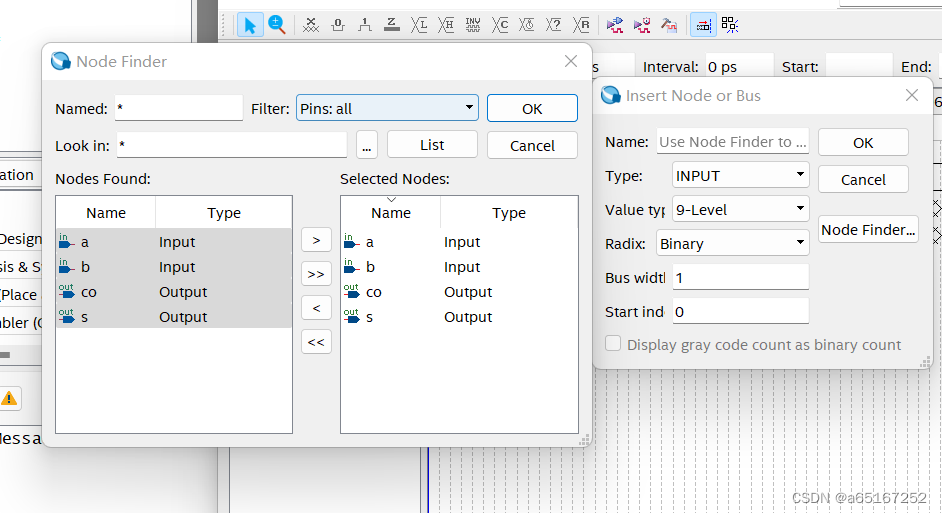

点击node finder 然后点击list 人然后点击>>

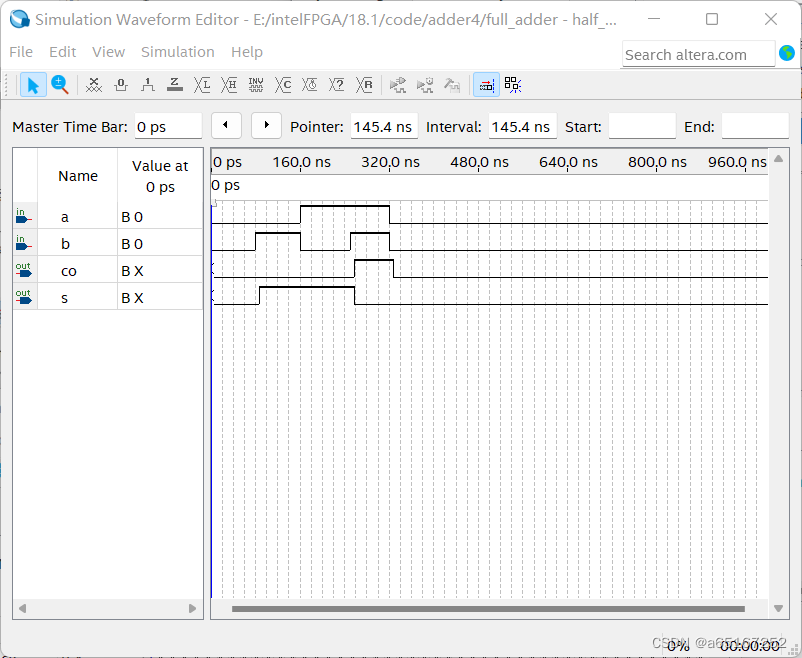

8.编辑信号

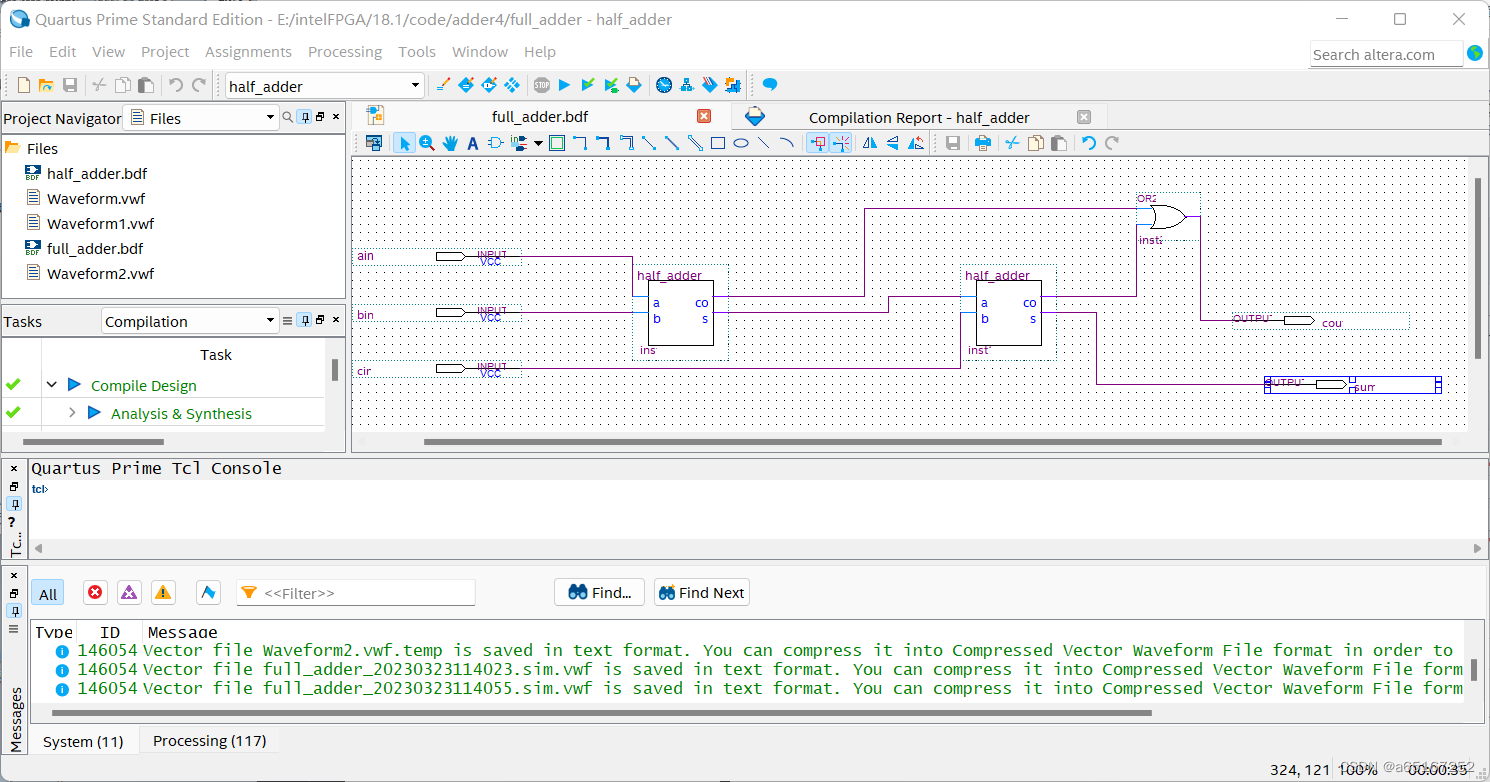

输入全加器原理图

9.将设计项目设置为可调用的元件

在打开半加器原理图文件half_adder.bdf的情况下,选择菜中File中的Create/Update→CreateSymbolFilesforCurrentFile项,即可将当前文件half_adder.bdf变成一个元件符号存盘,以待在高层次设计中调用

10.再按照半加器原理图绘制

11.实现仿真

按半加器步骤

编辑信号

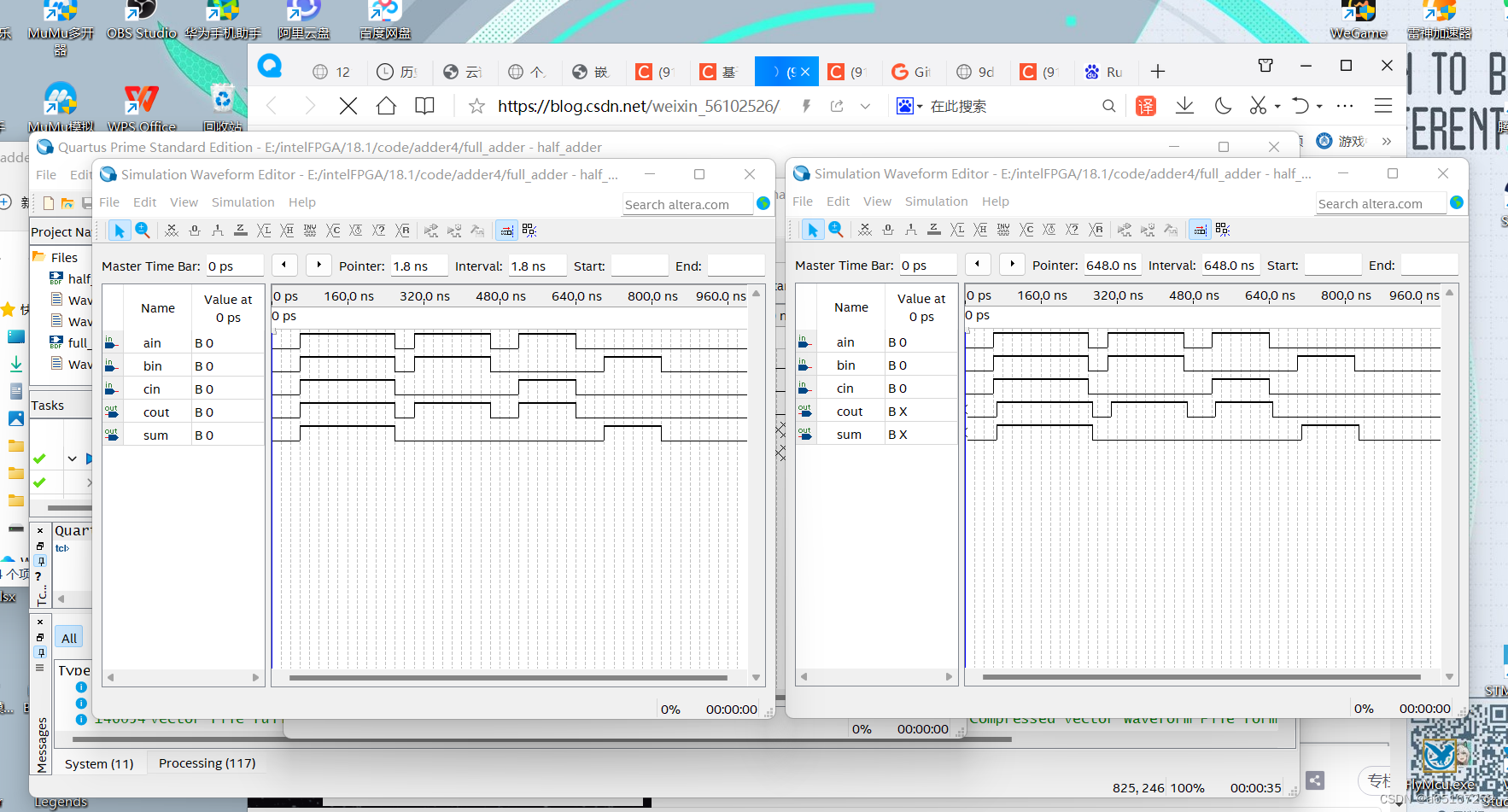

12.功能时序仿真结果

13.RTL图:

Verilog实现1位全加器

1.创建三个文件夹prj rtl tb文件

然后再rtl中写入代码:

module full_add2

(

input a, //加数

input b, //被加数

input cin, //进位输入

output sum, //结果输出

output cout //进位输出

);

assign sum = a^b^cin;

assign cout = (a&b)|((a^b)&cin);

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

在tb文件中写入代码:

`timescale 1 ns/ 1 ns

module full_add2_tb();

reg a;

reg b;

reg cin;

reg clk;

// wires

wire cout;

wire sum;

initial begin

clk = 0;

a = 0;

b = 0;

cin = 0;

end

always #10 clk = ~clk; //时钟频率50Hz

always@(posedge clk)begin

a = {$random}%2;

b = {$random}%2;

cin = ($random)%2;

end

full_add2 u_full_add2 (

.a (a),

.b (b),

.cin (cin),

.cout (cout),

.sum (sum)

);

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

创建项目如上 只不过在最后一步选择modelsim-alter

然后再assignment——> setting

输入测试文件名称 然后加入测试文件 然后okokok 完成

RTL图像:

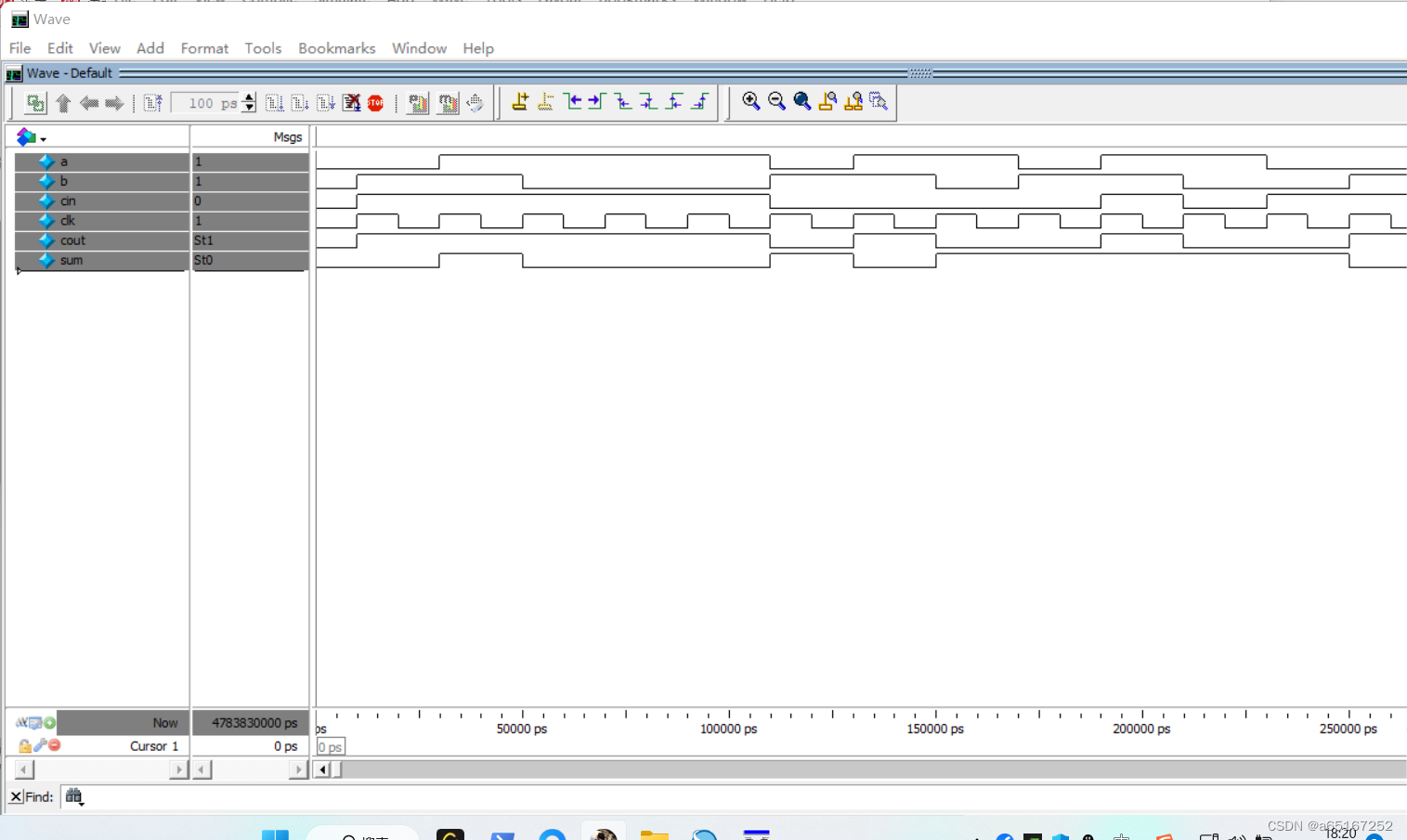

wave图像:

二、在此基础上,用原理图以及Verilog 编程两种方式,完成4位全加器的设计,对比二者生成的 RTL差别;使用modelsim验证逻辑设计的正确性

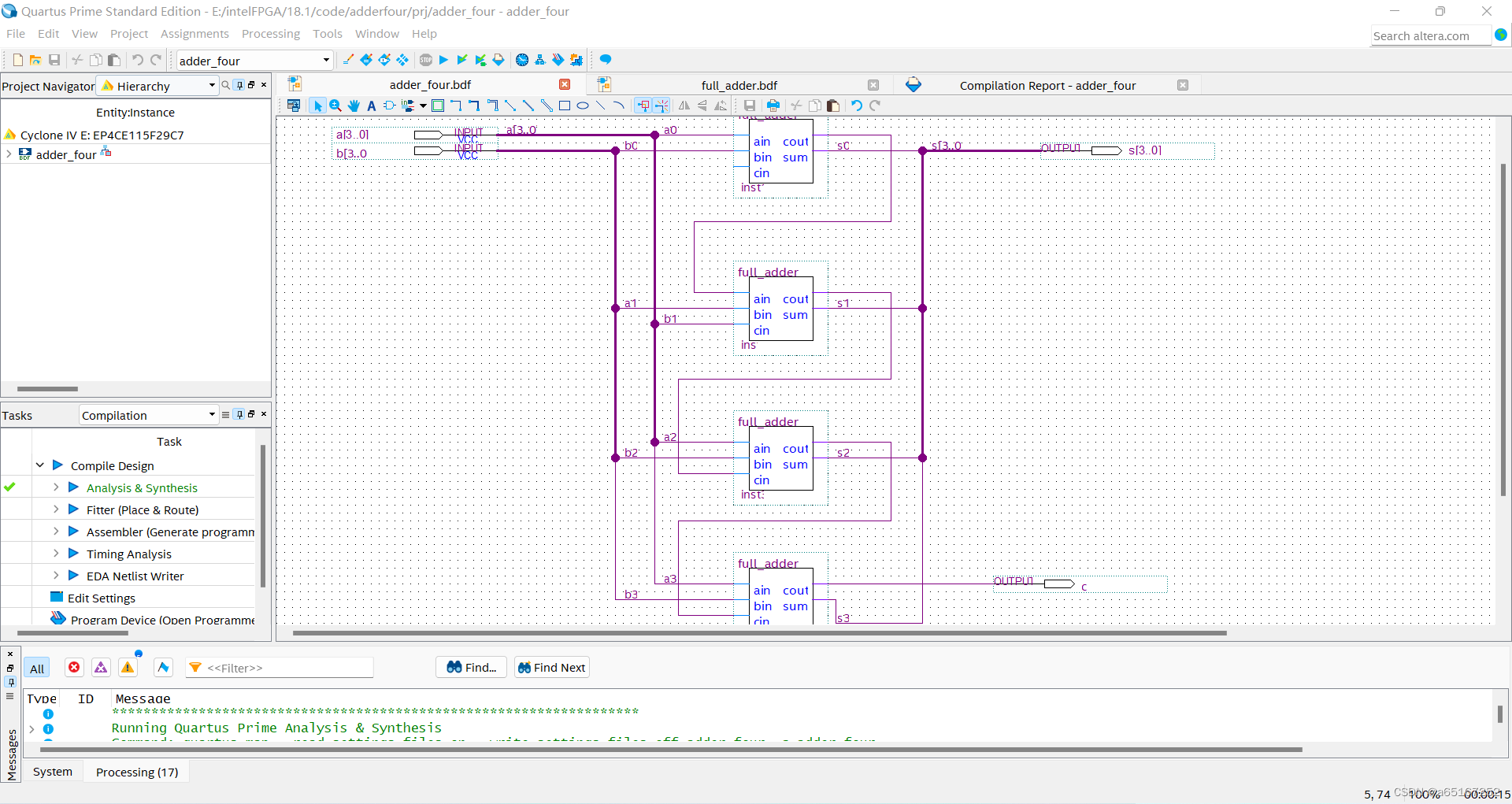

原理图实现4位全加器

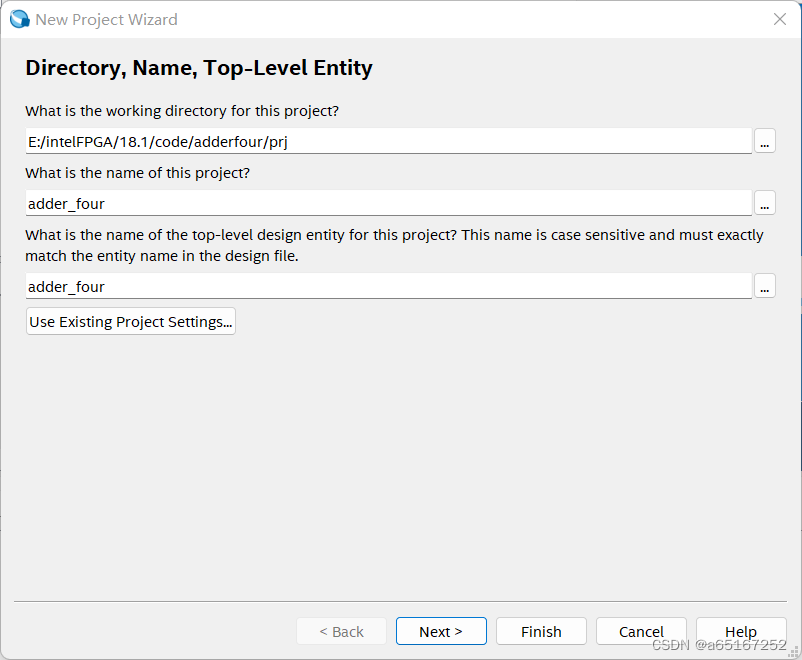

创建项目:

其余步骤如同一位全加速器

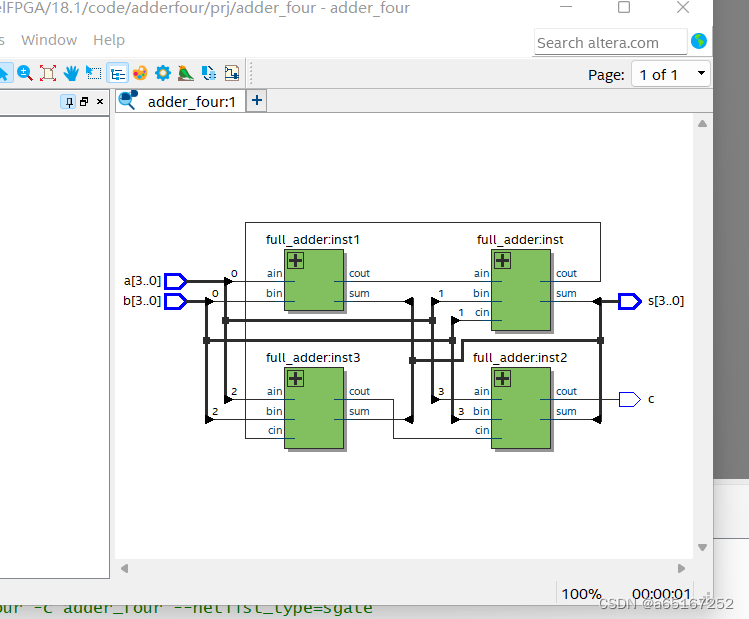

电路图:

分别调入元件full_adder和输入输出引脚input和output。并如图用点击拖动的方法连接好电路。输入各引脚名:a[3…0]、b[3…0], c和s[3…0],并设置总线和命名线路。

设置总线

然后依次如图设置

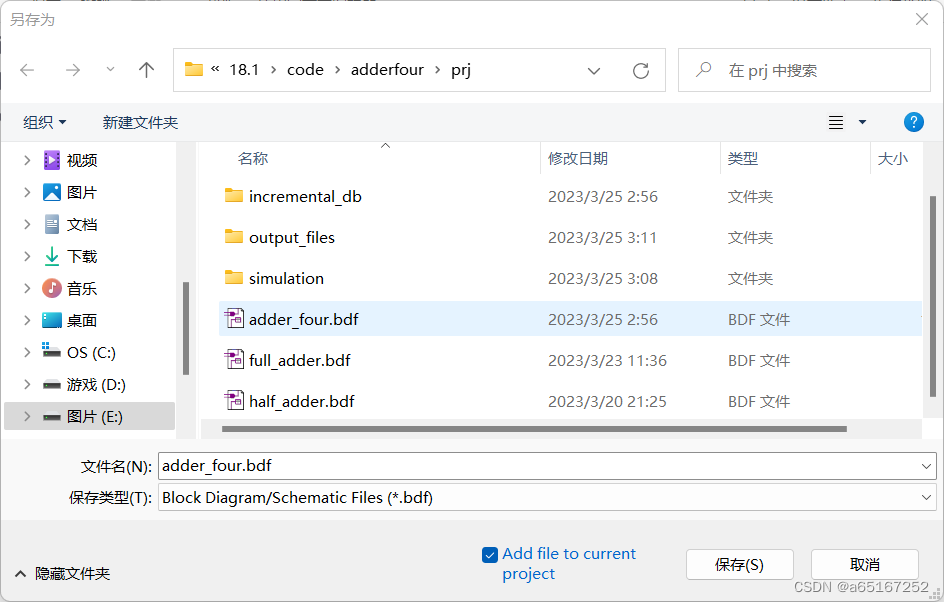

保存文件,选择菜单File - Save As,选择刚才为自己的工程建立的目录…\adder下,将已设计好的原理图文件取名为:adder_four.bdf(注意默认的后缀是.bdf),并存盘在此文件夹内

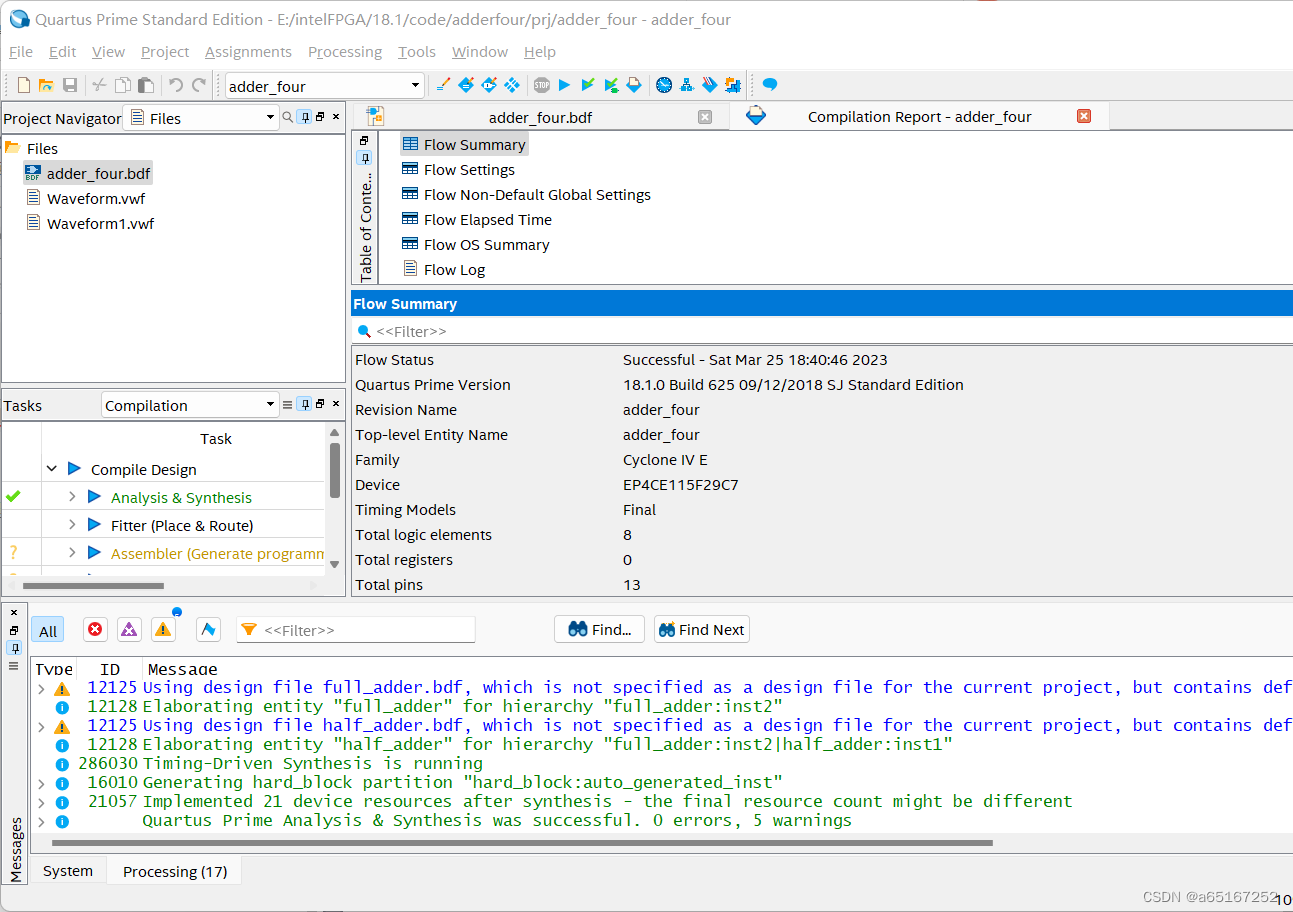

编译,点击图标进行编译,若无错误则可进行下一步,若有错进行原理图修改

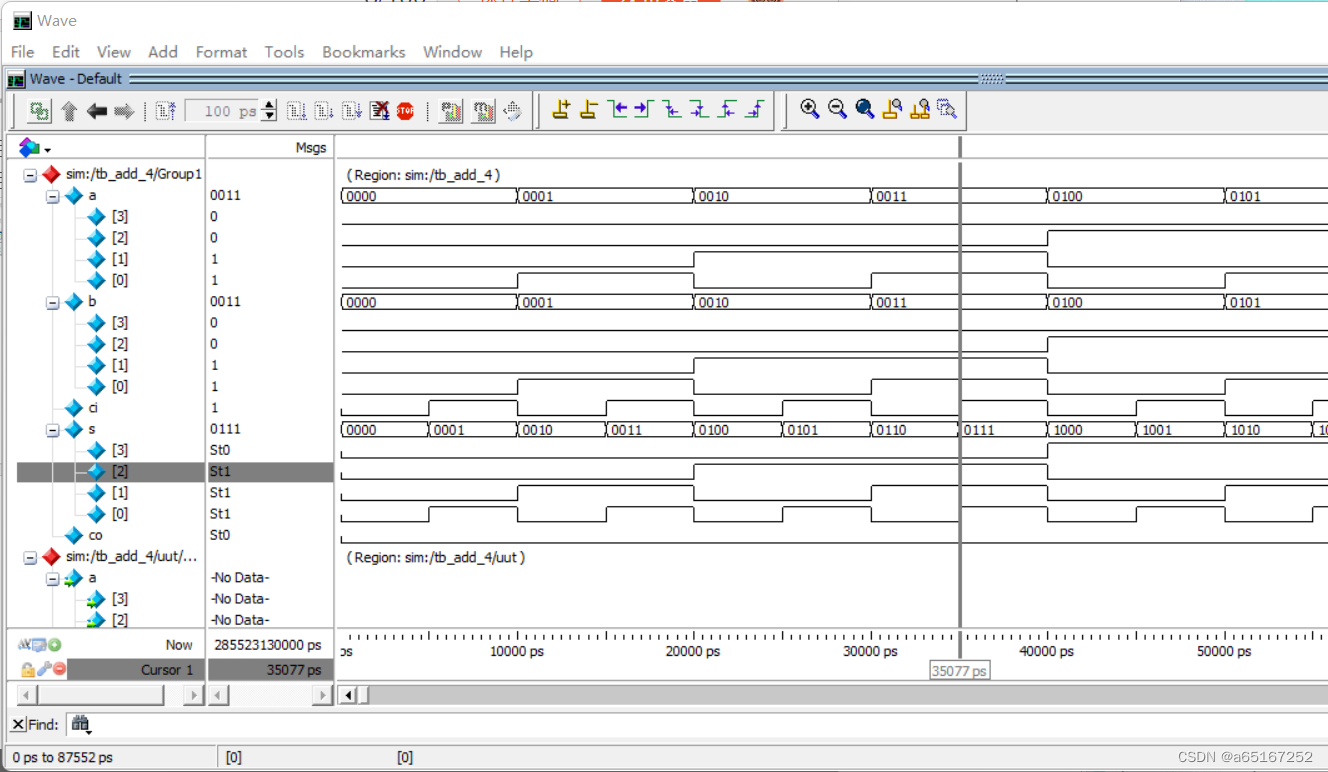

仿真

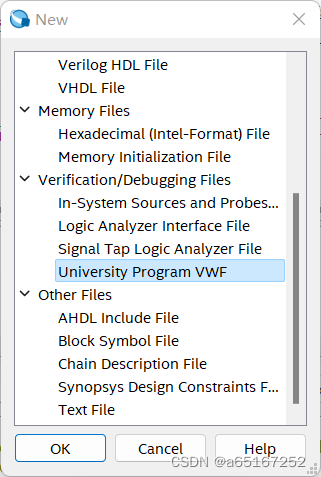

1.新建波形文件file→new→university program VWF,选择后点击OK

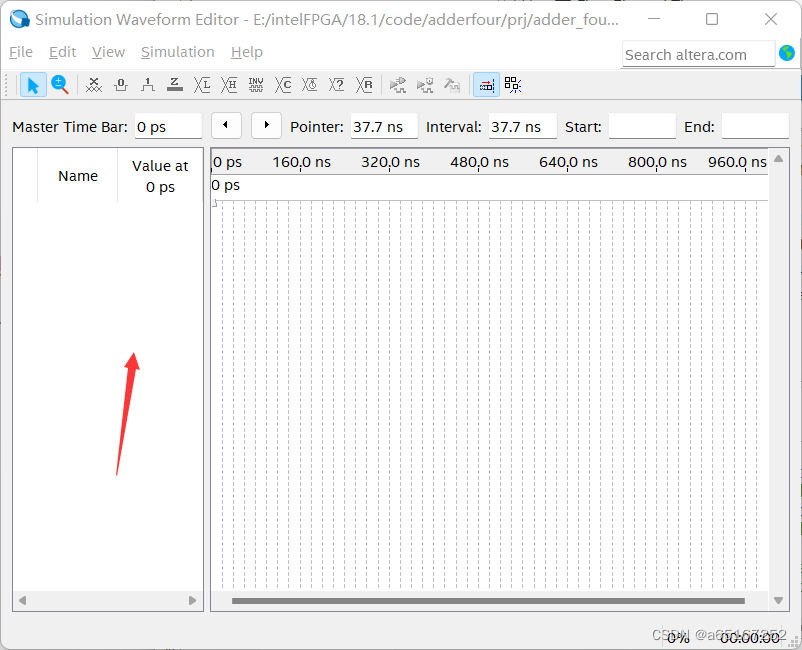

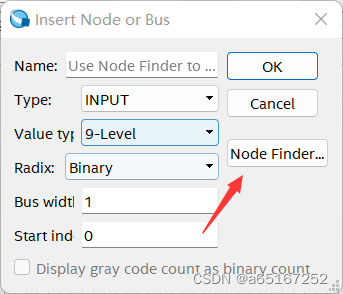

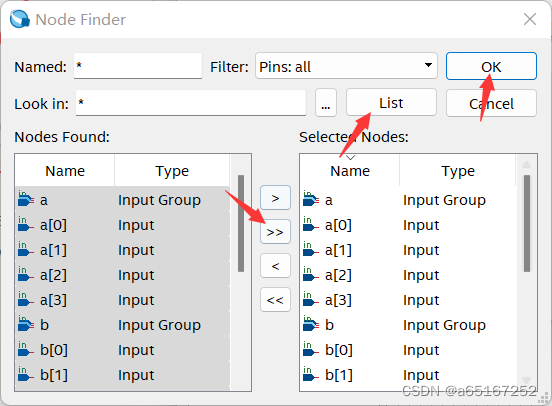

2.点击空白处,选择insert node or bus→node finder

3.点击List,左面出现则触发器中所有的输入输出引脚。再在该界面上点击>>,则把左边所有的端口都选择到右边,点击两次OK,进入波形

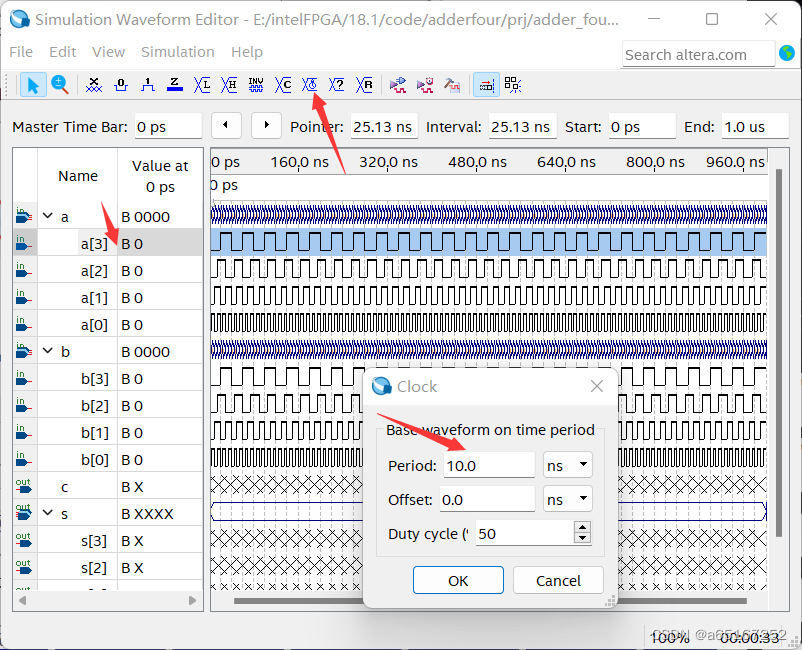

4.设置波形后保存

5.点击仿真编译按钮

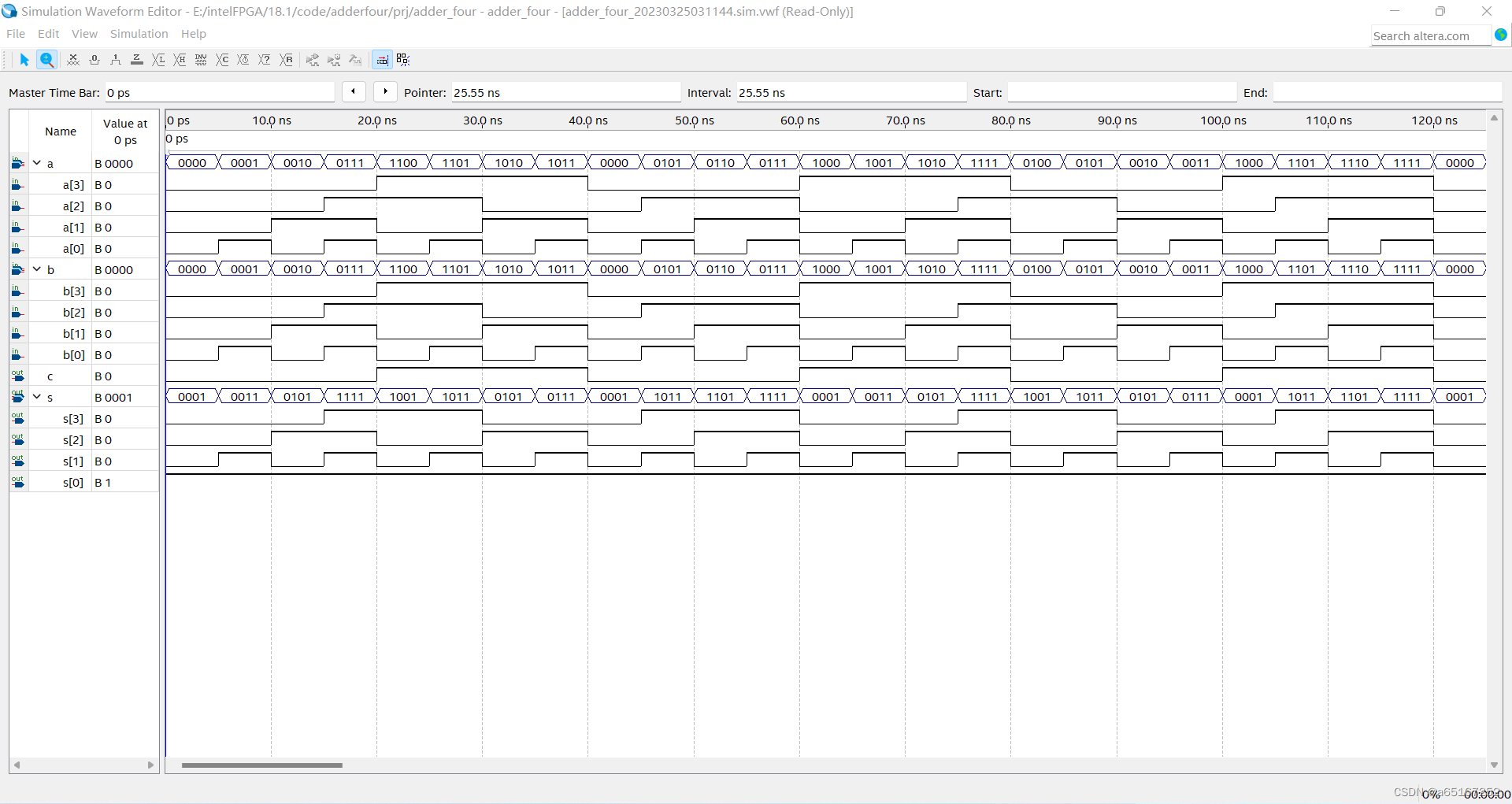

最终结果如图

输入输出满足表达式

S=A+B+CI,C1=‘1’(‘0001’)

S>15时进位C为‘1’

RTL图:

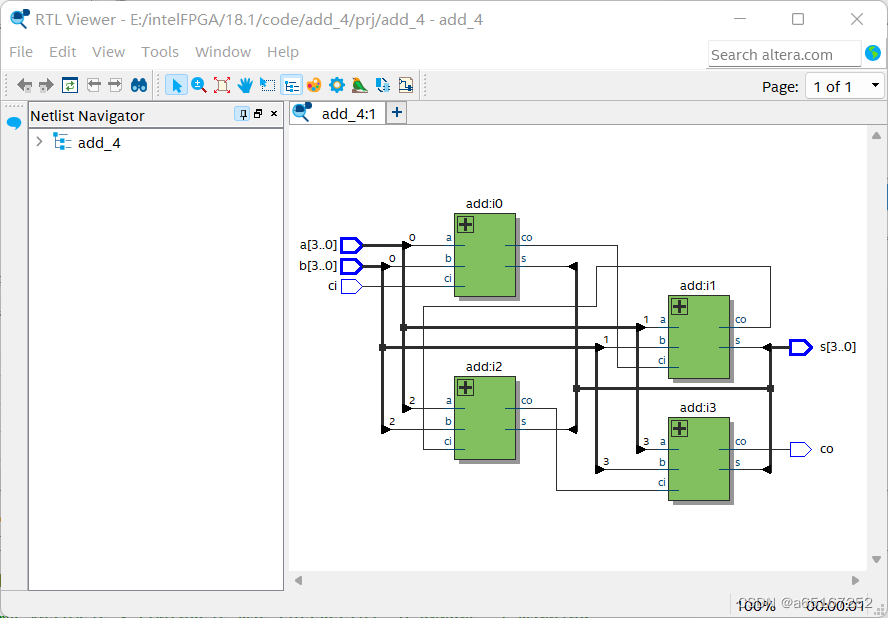

Verilog实现4位1位全加器

如上依次创建rtl prj tb文件夹

然后rtl中写入代码

module add_4(input [3:0] a,input[3:0]b,input ci,output[3:0]s,output co

);

wire[3:0] count;

add i0(a[0],b[0],ci,s[0],count[0]);

add i1(a[1],b[1],count[0],s[1],count[1]);

add i2(a[2],b[2],count[1],s[2],count[2]);

add i3(a[3],b[3],count[2],s[3],count[3]);

assign co=count[3];

endmodule

module add(input a ,input b, input ci,output s,output co);

assign s=a^b^ci;

assign co=(a&b)|(b&ci)|(a&ci);

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

.

在tb中写入测试文件:

`timescale 1 ns/ 1 ns

module tb_add_4();

reg [3:0] a;

reg [3:0] b;

reg ci;

// Outputs

wire [3:0] s;

wire co;

// Instantiate the Unit Under Test (UUT)

add_4 uut (

.a(a),

.b(b),

.ci(ci),

.s(s),

.co(co)

);

always #5 ci=~ci;

initial begin

a=4'b0000;b=4'b0000;ci=0;

repeat(16)

#10 b=b+1;

end

initial begin

a=4'b0000;b=4'b0000;ci=0;

repeat(16)

#10 a=a+1;

end

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

然后其余步骤和一位加速器没有区别

然后RTL图、wave图依次如下:

三、总结

通过本次实验,我学会了如何使用modelsim,如何将电路图换成RTL图让我们能更直观的看电路图,理解了四位全加器的基本原理,也让我基本的入门了FPGA,也让我熟练了QURTAUS的运用,收获颇多。