热门标签

热门文章

- 1《Distilling the Knowledge in a Neural Network》论文总结_distilling the knowledge in a neural network.

- 2Kafka的零拷贝_kafka零拷贝

- 3MYIR-ZYNQ7000系列-zturn教程(1)-从新建工程到下载bit文件_vivado下载bit文件

- 4基于华为eNSP的中小企业办公园区网络规划与设计_利用华为ensp模拟器分析和配置中小型企业网络论文

- 5aigc 启动器 sd-webui-aki-v4 decode_base64_to_file

- 6太兴奋了!Stable Diffusion WebUI v1.9.0它来了~重大更新!超详细讲解!_stable-diffusion-webui 更新

- 7基于Java+hadoop网络云盘上传下载系统设计与实现_使用hadoop文件接口,实现网盘功能

- 8服务端开发之Java备战秋招面试7_lpop和rpop会一直空轮训,消耗资源

- 9如何安装Microsoft Edge浏览器驱动_edge驱动安装教程

- 10SQL CRUD(阿里ODPS版)_odps增加字段

当前位置: article > 正文

Quartus II实验二 运算部件实验:并行乘法器_quartus ii乘法器模块

作者:不正经 | 2024-06-12 11:35:06

赞

踩

quartus ii乘法器模块

如果很多操作步骤忘记可以参考链接:Quartus II实验一 运算部件实验:加法器[这里是图片001]https://blog.csdn.net/qq_45037155/article/details/124202068

本实验需要建立三个工程文件

1. 设计一个4位求补器

2. 设计一个4·4的不带符号的阵列乘法器

3. 设计一个5·5的带符号的阵列乘法器

一、 建立一个工程,设计4位求补器,并加以仿真

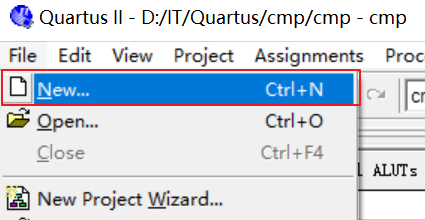

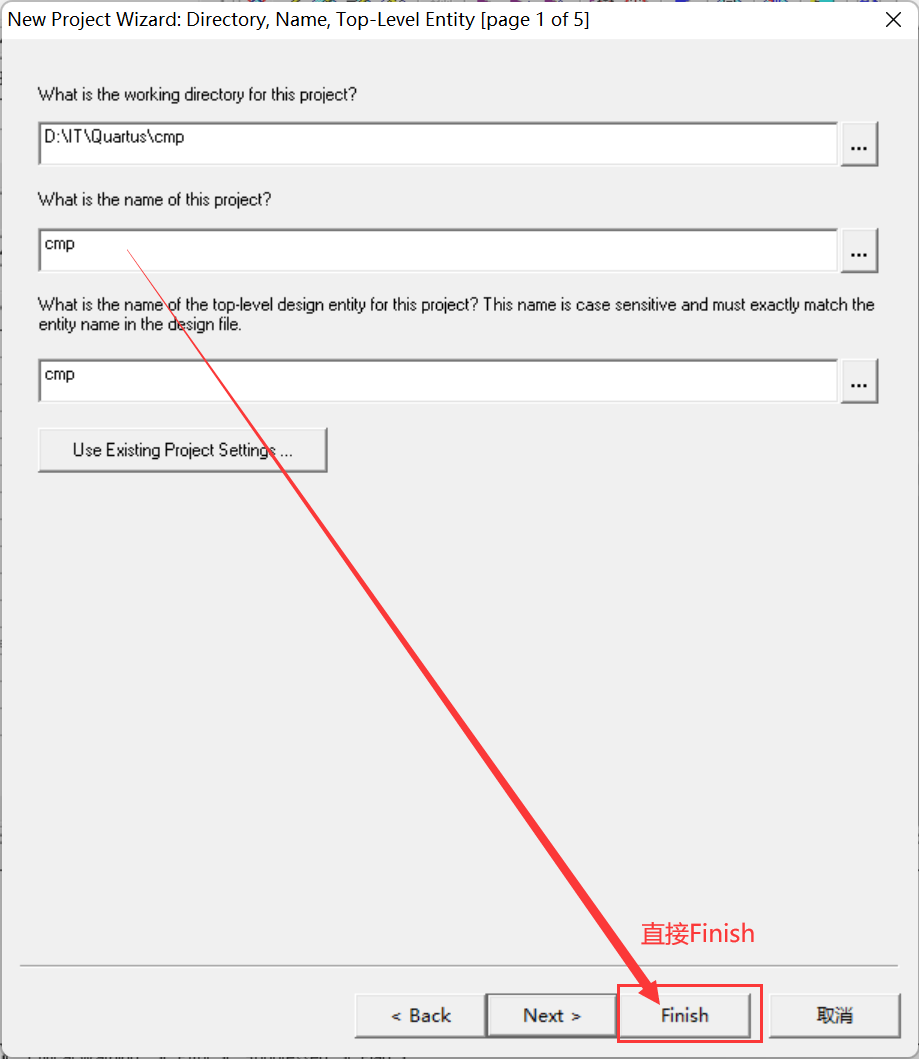

1. 新建工程 cmp

(1)保存位置 D:ITQuartuscmp

工程名称 cmp

主文件(top-level design entity)cmp

2. 设计原理图文件保存为cmp.dbf

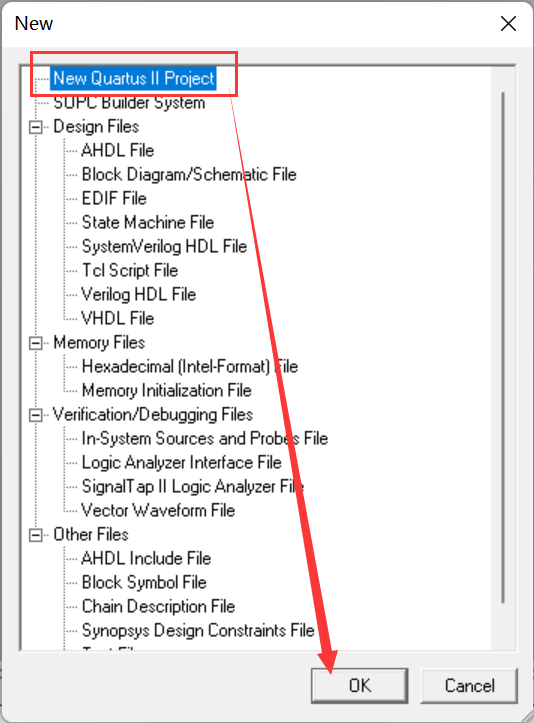

(1)新建——Block Diagram,保存为cmp

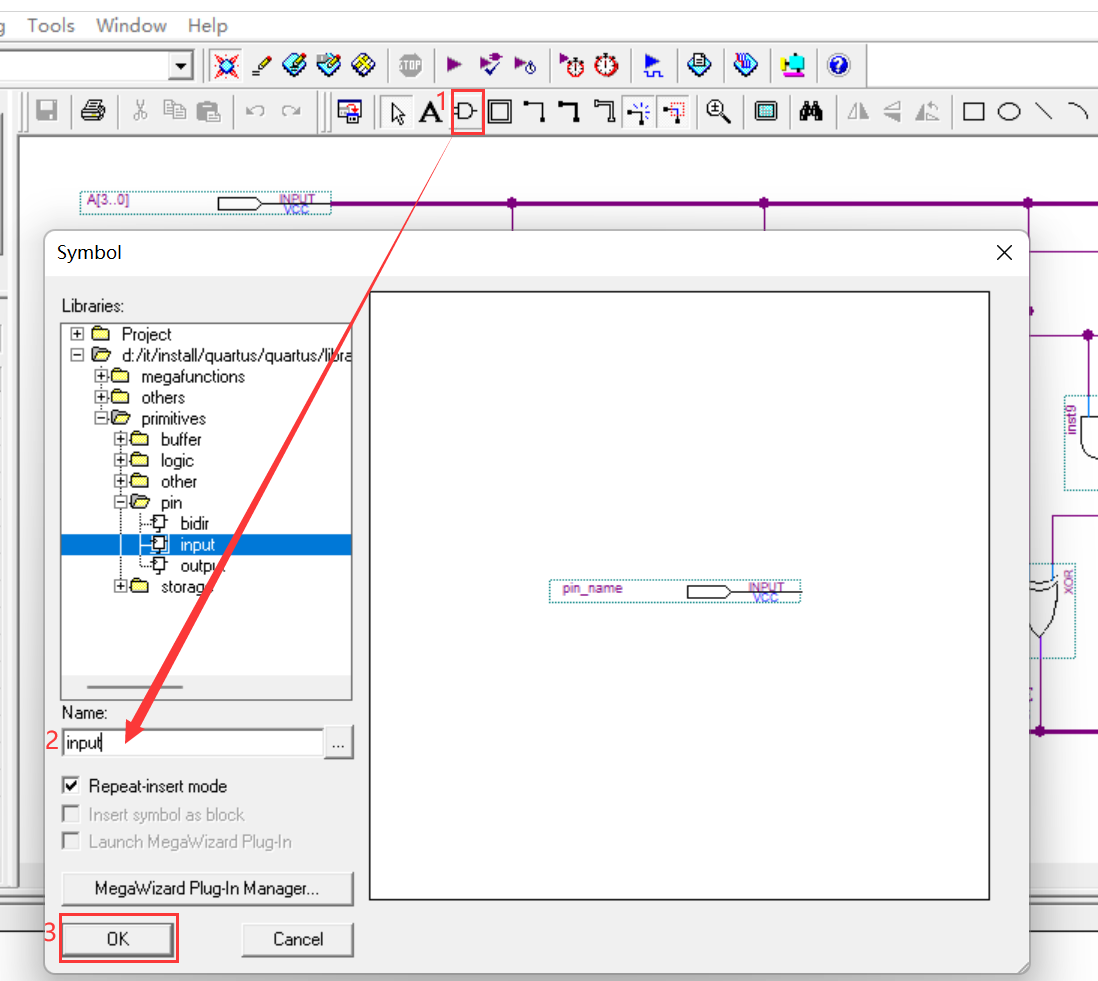

(2)添加元件:

输入信号、输出信号、2与门、2或门、异或门

Input output and2 or2 xor

修改输入信号依次位A[3…0]、Cin、E

输出信号依次为 CA[3…0]、Cout

(3)设置Cin和Cout的目的

a. 扩展4位求补器,构成4*n位的求补器

b. 低位求补器的Cout传递低位求补器是否有1的信息,

c. 高位求补器的Cin用于接收低位Cout的信息。

(4)连接元件

这里强调注意点:

a. OK选中后在图上单击即可显示,按键Esc退出使用,Delete删除

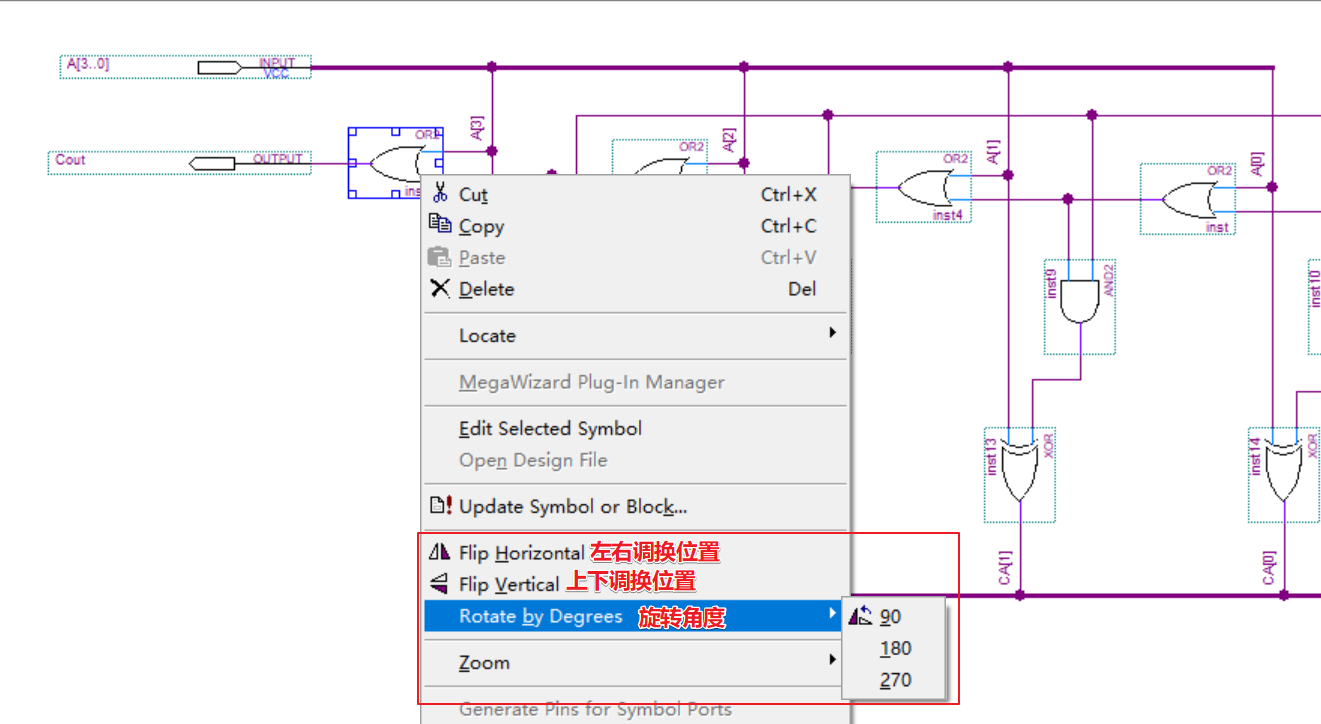

b. 对于图的形态变化如图操作

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/不正经/article/detail/707920

推荐阅读

相关标签