热门标签

热门文章

- 1编译原理(一)编译程序、解释程序、程序设计语言范型_解释型程序的流程

- 2软件测试面试?太简单了 2023测试面经 (答案+思路+史上最全)

- 3kitti数据集_基于KITTI数据集的无人驾驶感知相关功能实现(2)

- 4java测试类 main方法_为什么使用Junit Test而不用普通java main方法来完成测试?

- 5python+django计算机毕设选题列表pycharm毕业设计项目lw

- 6从服务器布置到yolov5运行到生成安卓APP,一天足矣_yolov5 tflite

- 7嵌入式的时间概念:GMT,UTC,CST,DST,RTC,NTP,SNTP,NITZ_rtc utc

- 8STM32CubeMX系列|FATFS文件系统_cubemx fatfs

- 9windows 一键更新 当前文件夹下的多个git项目_windows更新文件夹下多个git仓库

- 10(七十四)Android O Service启动流程梳理——startForegroundService

当前位置: article > 正文

小梅哥Xilinx FPGA学习笔记13——动态数码管显示_数码管显示12fpga

作者:AllinToyou | 2024-04-21 20:37:51

赞

踩

数码管显示12fpga

目录

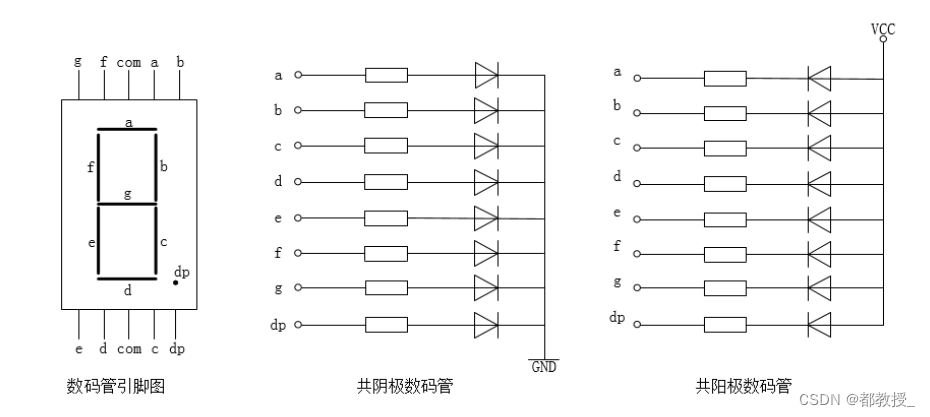

一、数码管简介

数码管是一种半导体发光器件,其基本单元是发光二极管。数码管按段数一般分为七段数码管和八段数码管,八段数码管比七段数码管多一个发光二极管(多一个小数点显示)。当然也还有一些其他类型的数码管如“N”形管、“米”字管以及工业科研领域用的 16 段管、24 段管等,在此就不详细介绍。下面将为大家详细介绍本次实验使用的八段

数码管。

八段数码管是一个八字型数码管,分为八段:

a

、

b

、

c

、

d

、

e

、

f

、

g

、

dp

,其中

dp

为小数点,每一段即为一个发光二极管,这样的八段我们称之为段选信号。

数码管分为

共阳极数码管

和

共阴极数码管

。共阳极数码管就是把发光二极管的正极连接在一起作为一个引脚,负极分开。相反的,共阴极数码管就是把发光二极管的阴极连接在一起作为一个引脚,正极分开。这两者的区别在于,公共端是接地还是接高电平。如果接地则为共阴极数码管,则段选信号为高电平时对应段才会被点亮;如果接高电平则为共阳极数码管,则段选信号为低电平时对应段才会被点亮。

下表给出不同的段点亮可显示

0~f

的值,如下表

所示。

段式数码管工作方式有两种:

静态显示和动态显示

。

静态显示的特点是每个数码管的

段选必须接一个

8

位数据线来显示字形,显示字形可一直保持,直到送入新字形码为止。那么如果点亮

8

个码管是不是需要

64

位数据线去分别控制每一个码管的段选?当然这种方

法也可以,但是其占用的

I/O

口较多,因此硬件电路比较复杂,成本较高,很少使用。

那么如何节约资源呢?以六位数码管为例,如下图

所示:

由上图可以看到,我们将六个数码管的段选信号连接在一起,而位选(

sel

)独立控制,这样六个数码管接在一起就少了

8

×

5

个

I/O

口。这里对位选信号特别说明一下:由上

图可以看到每一个数码管都有一个位选信号,而这个位选信号就控制着数码管的亮灭。这

样我们就可以通过位选信号去控制数码管亮,而在同一时刻,位选选通的数码管上显示的

字形是一样的,因为我们将

6

个数码管相对应的段选连在了一起,数码管的显示自然就相

同了,数码管的这种显示方式即为静态显示。而如果要让每个数码管显示的值不同,我们

要用到另外一种显示方式,即动态显示,将在下一章节给大家介绍。本章节先讲述

6

位共

阳极数码管的静态显示,为下个章节的动态显示做准备。

二、静态显示实验目标

根据上一小节的理论学习,我们可以设计一个这样的

6

位数码管静态显示:控制八位

数码管让其以

000000

、

111111

、

222222

一直到

FFFFFF

循环显示。每个字符显示

0.5s

后变

化。系统框图如下图所示:

2.1 设计文件

- `timescale 1ns / 1ps

-

- module seg_static(

- input Clk,

- input Reset_n,

- output reg [7:0] sel,

- output reg [7:0] seg

- );

-

- reg [3:0]num;

- reg add_flag;//数码管数值+1 标志信号

- reg [24:0]cnt_wait;//0.5s计数器

- parameter CNT_WAIT_MAX = 25000_000-1; //计数器最大值(0.5s)

-

- //十六进制数显示编码

- parameter SEG_0 = 8'b1100_0000, SEG_1 = 8'b1111_1001,

- SEG_2 = 8'b1010_0100, SEG_3 = 8'b1011_0000,

- SEG_4 = 8'b1001_1001, SEG_5 = 8'b1001_0010,

- SEG_6 = 8'b1000_0010, SEG_7 = 8'b1111_1000,

- SEG_8 = 8'b1000_0000, SEG_9 = 8'b1001_0000,

- SEG_A = 8'b1000_1000, SEG_B = 8'b1000_0011,

- SEG_C = 8'b1100_0110, SEG_D = 8'b1010_0001,

- SEG_E = 8'b1000_0110, SEG_F = 8'b1000_1110;

-

- parameter IDLE = 8'b1111_1111; //不显示状态

-

- //0.5S计数功能

- always@(posedge Clk or negedge Reset_n)

- if(!Reset_n)

- cnt_wait <= 0;

- else if (cnt_wait == CNT_WAIT_MAX)

- cnt_wait <= 0;

- else

- cnt_wait <= cnt_wait +1;

- //数码管数值+1 标志信号实现逻辑(一个高脉冲)

- always@(posedge Clk or negedge Reset_n)

- if(!Reset_n)

- add_flag <= 0;

- else if (cnt_wait == CNT_WAIT_MAX)

- add_flag <= 1;

- else

- add_flag <= 0;

-

- //num:从 4'h0 加到 4'hf 循环

- always@(posedge Clk or negedge Reset_n)

- if(!Reset_n)

- num <= 0;

- else if(add_flag)

- num <= num +1;

- else

- num <= num;

-

- //sel:选中六个数码管(位选信号)

- always@(posedge Clk or negedge Reset_n)

- if(!Reset_n)

- sel <= 8'b0000_0000;

- else

- sel <= 8'b1111_1111;

-

- //给要显示的值编码

- always@(posedge Clk or negedge Reset_n)

- if(!Reset_n)

- seg <= IDLE;

- else begin

- case (num)

- 4'd0: seg <= SEG_0;

- 4'd1: seg <= SEG_1;

- 4'd2: seg <= SEG_2;

- 4'd3: seg <= SEG_3;

- 4'd4: seg <= SEG_4;

- 4'd5: seg <= SEG_5;

- 4'd6: seg <= SEG_6;

- 4'd7: seg <= SEG_7;

- 4'd8: seg <= SEG_8;

- 4'd9: seg <= SEG_9;

- 4'd10: seg <= SEG_A;

- 4'd11: seg <= SEG_B;

- 4'd12: seg <= SEG_C;

- 4'd13: seg <= SEG_D;

- 4'd14: seg <= SEG_E;

- 4'd15: seg <= SEG_F;

- default:seg <= IDLE ; //闲置状态,不显示

- endcase

- end

- endmodule

2.2 仿真激励文件

- `timescale 1ns / 1ps

-

-

- module seg_static_tb();

-

- reg Clk;

- reg Reset_n;

- wire [7:0]sel;

- wire [7:0]seg;

-

- seg_static seg_static(

- .Clk(Clk),

- .Reset_n(Reset_n),

- .sel(sel),

- .seg (seg)

- );

-

- defparam seg_static.CNT_WAIT_MAX = 25000 - 1;

-

-

- initial Clk <= 1;

- always #10 Clk <= ~Clk;

-

- initial

- begin

- Reset_n <= 1'b0;

- #201

- Reset_n <= 1'b1;

- #8000000;

- $stop;

- end

-

- endmodule

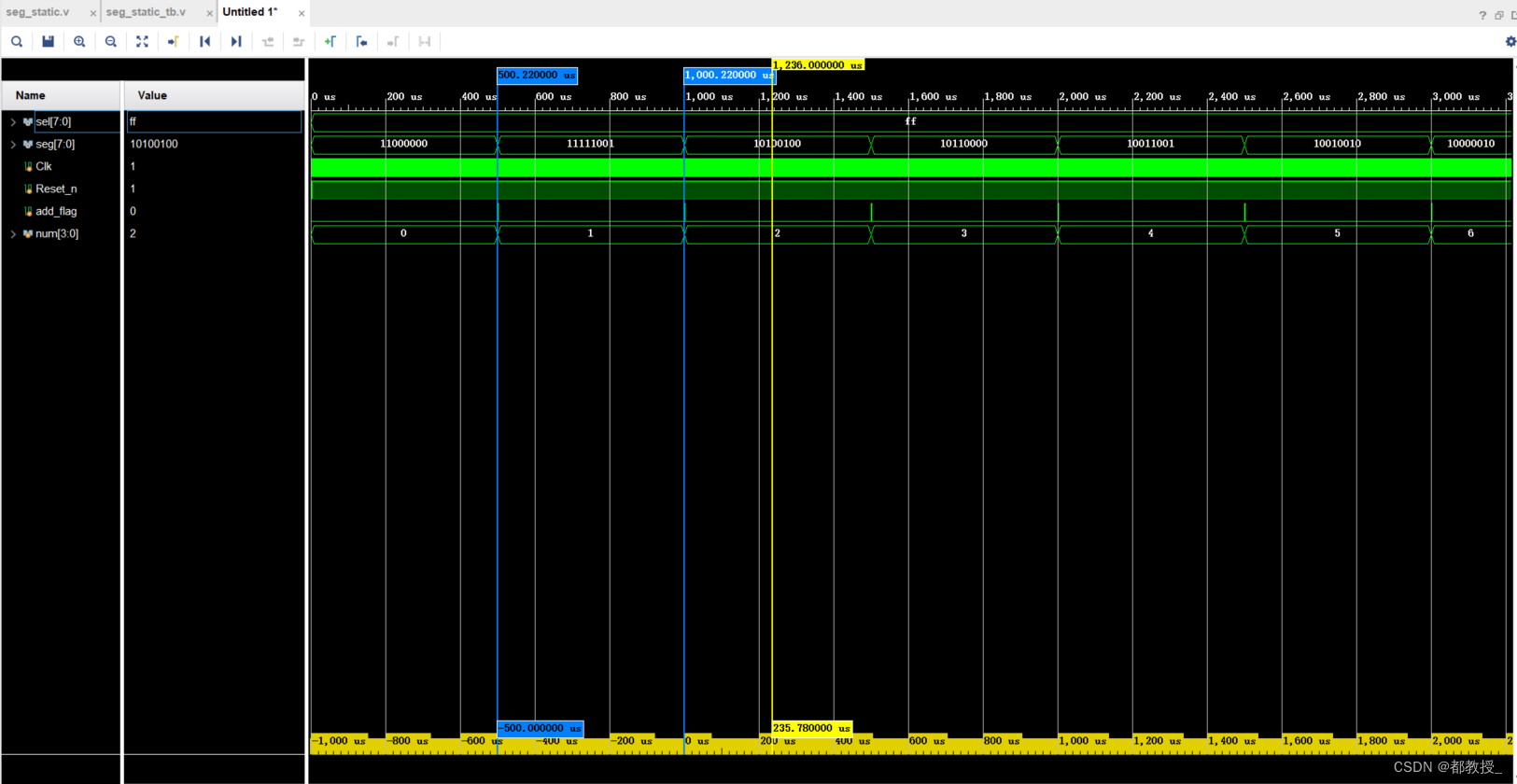

2.3 仿真图

从仿真图中可以看出

数码管上的数据每0.5s从

000000~FFFFFF

之间循环显示,试验成功。

以上是是师从野火教程。

三、 动态显示实验

在上一章节我们知道静态显示是让六个数码管的

8

位段选信号连在

8

根线上且六个数码管的位选信号同时选中点亮。但是如果我们每次只选中一个数码管点亮呢?

这样我们段选信号点亮的就只是我们选中数码管的值了,那是不是就可以给每个数码管显

示不一样的值了?但是这样我们又会发现一个新的问题:每次只点亮一个数码管,那么同

一时间六个数码管就只能看到一个数码管在亮,那不是同时显示不了六个不同的字符了

吗?针对这个问题先为大家介绍

两种现象:

首先

是人眼视觉暂留:人眼在观察景物时,光信号传入大脑神经,需经过一段短暂的

时间,光的作用结束后,视觉影像并不立即消失,这种残留的视觉称“后像”,视觉的这一现象则被称为“视觉暂留”。

其次

是数码管的余晖效应:当停止向发光二极管供电时发光二极管亮度仍能维持一段

时间。

根据这两种现象我们可以想到,如果让数码管轮流显示,而且轮流显示速度很快,这样会不会看起来六个数码管都在显示呢?事实证明是可以的,这种方式称为动态扫描。为

帮助大家理解,打个比方:若一个数码管在

1s

内点亮两次,那么我们可以很明显的看到其

亮了两次,若

1s

内点亮

10

次呢?我们可能只能看到其在快速的闪烁,若点亮

100

次

1000次呢?总有一个速度我们人眼是分辨不出来在闪烁的。所以说一个数码管让我们人眼感觉

一直在亮并不用一直给其点亮,只要我们让其亮的间隔足够短就行。这样我们就可以用不

在点亮的时间去点亮其他数码管,让其他数码管也达到这样的效果,这样就可以让我们人

眼感觉所有数码管都在同时点亮了。

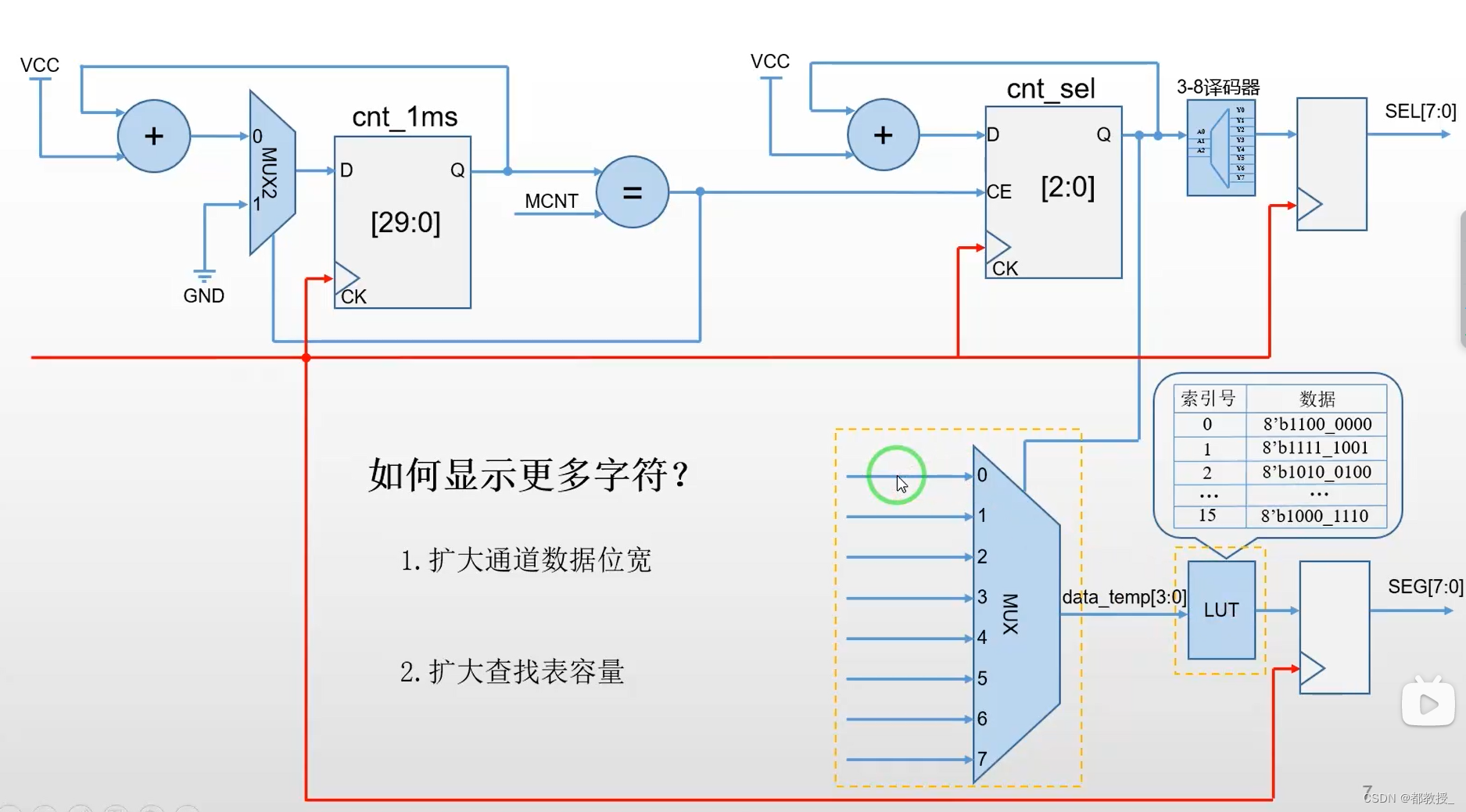

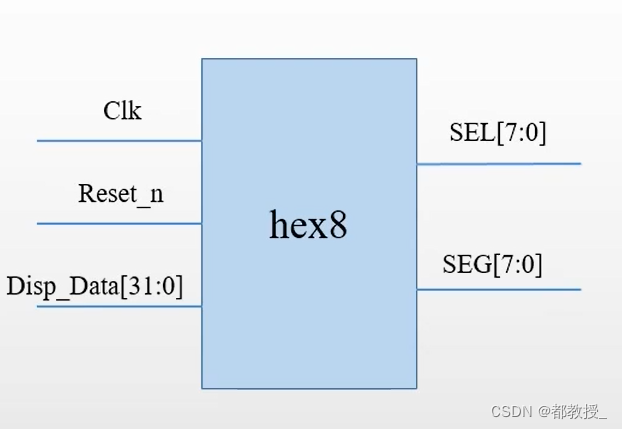

系统框图如下图所示:

3.1 设计文件

- module hex8(

- input Clk,

- input Reset_n,

- input [31:0]Disp_Data,

- output reg [7:0]SEL,

- output reg [7:0]SEG

- );

-

- reg [29:0]cnt_1ms;

- reg Flag_1ms; //每1毫秒切换一个数码管

- reg [2:0]cnt_sel;//位选信号

- parameter MCNT = 50000-1;

-

- //定时一毫秒

- always@(posedge Clk or negedge Reset_n)

- if(!Reset_n)

- cnt_1ms <= 0;

- else if(cnt_1ms == MCNT)

- cnt_1ms <= 0;

- else

- cnt_1ms <= cnt_1ms + 1;

-

- //产生一个一毫秒到来的高脉冲信号

- always@(posedge Clk or negedge Reset_n)

- if(!Reset_n)

- Flag_1ms <= 0;

- else if(cnt_1ms == MCNT)

- Flag_1ms <= 1;

- else

- Flag_1ms <= 0;

-

- //cnt_sel自加逻辑实现(每1毫秒自加一次切换一个数码管)

- always@(posedge Clk or negedge Reset_n)

- if(!Reset_n)

- cnt_sel <= 0;

- else if(Flag_1ms)

- cnt_sel <= cnt_sel + 1;

- else

- cnt_sel <= cnt_sel;

-

- //数码管的位选择逻辑

- always@(posedge Clk)begin

- case(cnt_sel)

- 0: SEL <= 8'b0000_0001;

- 1: SEL <= 8'b0000_0010;

- 2: SEL <= 8'b0000_0100;

- 3: SEL <= 8'b0000_1000;

- 4: SEL <= 8'b0001_0000;

- 5: SEL <= 8'b0010_0000;

- 6: SEL <= 8'b0100_0000;

- 7: SEL <= 8'b1000_0000;

- default:SEL <= 8'b0000_0000;

- endcase

- end

-

- reg [3:0]data_temp;//显示16种数值8 + 4 + 2 + 1+1 = 16,

- //建立一个查找表,表中列出SEG段选信号的各种情况。

- always@(posedge Clk)begin

- case(data_temp)

- 0: SEG <= 8'b1100_0000; //0

- 1: SEG <= 8'b1111_1001; //1

- 2: SEG <= 8'b1010_0100; //2

- 3: SEG <= 8'b1011_0000; //3

- 4: SEG <= 8'b1001_1001; //4

- 5: SEG <= 8'b1001_0010; //5

- 6: SEG <= 8'b1000_0010; //6

- 7: SEG <= 8'b1111_1000; //7

- 8: SEG <= 8'b1000_0000; //8

- 9: SEG <= 8'b1001_0000; //9

- 10: SEG <= 8'b1000_1000;//A

- 11: SEG <= 8'b1000_0011;//B

- 12: SEG <= 8'b1100_0110;//C

- 13: SEG <= 8'b1010_0001;//D

- 14: SEG <= 8'b1000_0110;//E

- 15: SEG <= 8'b1000_1110;//F

- default:SEL <= 8'b1111_1111;//全灭

- endcase

- end

-

- //8路选择器实现逻辑(使用组合逻辑时<=与=无区别)

- always@(*)

- case(cnt_sel)

- 0:data_temp <= Disp_Data[3:0];

- 1:data_temp <= Disp_Data[7:4];

- 2:data_temp <= Disp_Data[11:8];

- 3:data_temp <= Disp_Data[15:12];

- 4:data_temp <= Disp_Data[19:16];

- 5:data_temp <= Disp_Data[23:20];

- 6:data_temp <= Disp_Data[27:24];

- 7:data_temp <= Disp_Data[31:28];

- default:data_temp = 4'b0000;

- endcase

-

- endmodule

3.2 仿真激励文件

- //只需要对输入信号赋值

- `timescale 1ns / 1ps

- module hex8_tb();

-

- reg Clk;

- reg Reset_n;

- reg [31:0]Disp_Data;

- wire [7:0]SEL;

- wire [7:0]SEG;

-

- hex8 hex8(

- .Clk(Clk),

- .Reset_n(Reset_n),

- .Disp_Data(Disp_Data),

- .SEL(SEL),

- .SEG(SEG)

- );

-

- initial Clk = 1;

- always #10 Clk = ~Clk;

-

- initial

- begin

- Reset_n = 0;

- Disp_Data = 32'h12345678;

- #201;

- Reset_n = 1;

- #20000000;//延时20ms

- Disp_Data = 32'h9abcdef0;

- #20000000;//延时20ms

- $stop;

- end

- endmodule

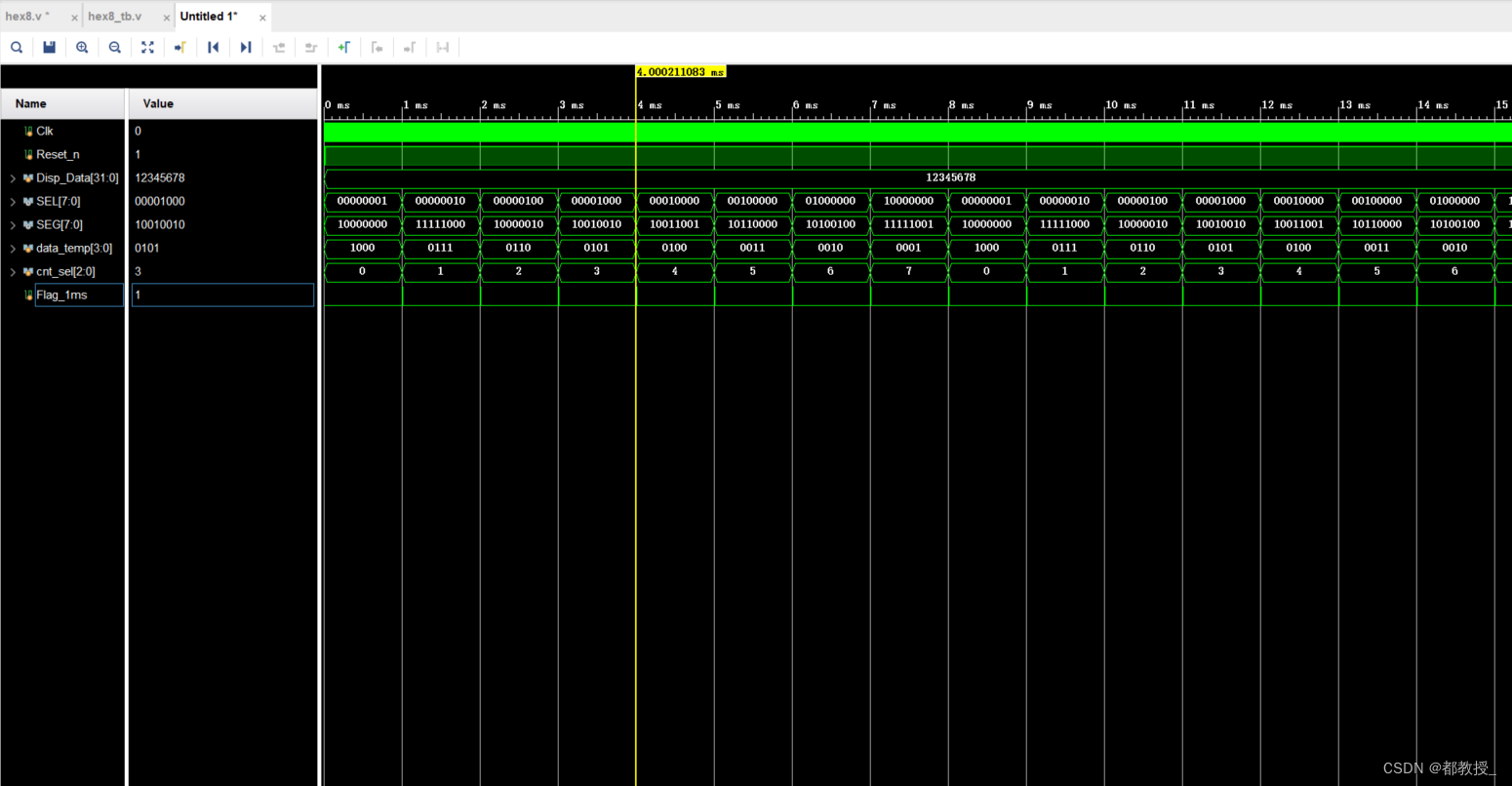

3.3 仿真图

由此,动态扫描得以实现,把想要显示的值放到32位的Disp_Data上即可,但是由于需要连接8个位选信号,8个段选信号,共16个信号线,说多不多说少也不少,所以ZYNQ使用74HC595芯片进行并转串将其变为三路输出,即将16路变为3路的芯片,岂不是更节约资源,这就要在下一章节阐述74HC595的驱动代码了。让我们转战下一小节。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/AllinToyou/article/detail/464991

推荐阅读

相关标签