- 1C语言进阶⑰(动态内存管理)四个动态内存函数+动态通讯录+柔性数组_malloc+free_简述动态内存分配的四个函数的用法c语言

- 2Morris神级遍历二叉树,时间复杂度为O(1)_遍历二叉树的时间复杂性为

- 3FPGA中打拍、异步复位、亚稳态、三段式状态机的理解_fpga打拍

- 4能够解决传统FTP传输弊端的替代工具是什么样的?_本机ftp命令不好用有什么替代的吗

- 5操作系统 实验29 同步与互斥

- 6关于高通Android 平台上qssi的介绍_高通qssi

- 7介绍分享几款免费的在线Web文件管理器_web文件目录浏览器

- 8【Redis】Redis高可用之Sentinel哨兵模式详解(Redis专栏启动)_jedisconnectionfactory连接redis哨兵

- 9k8s helm 安装prometheus-kafka-exporter 遇到问题_function "lookup" not defined

- 10Unity3d中默认函数调用顺序(MonoBehaviour)_unity monobehaviour执行时被哪个类调用

基于FPGA的DDR3学习——2.IP核设置_fpga ddr ip

赞

踩

5.IP核设置

硬件平台:xc7z035ffg676-2

Vivado软件:2018.3

(1)建立DDR3测试工程,选择DDR3 MIG IP核。

(2)进入MIG IP核配置界面

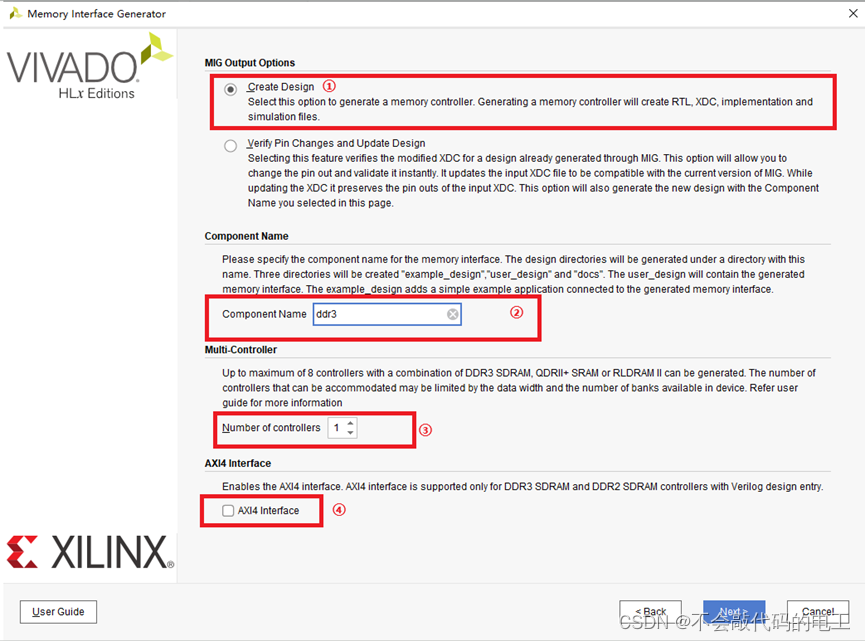

(3)创建MIG IP

①Create Design创建新设计

②Component Name,编辑MIG IP核名称,自定义

③Number of Controller,控制器数据量,此处选择1个

④AXI4 Interface,AXI4接口,测试工程选择Native Interface,不选择AXI4接口。

(4)Pin Compatible FPGAs,选择IP核兼容器件,方便DDR3 IP核工程移植。此处不选择

(5)存储器选择,由于电路板板载DDR3内存,故此处选择DDR3 SDRAM。

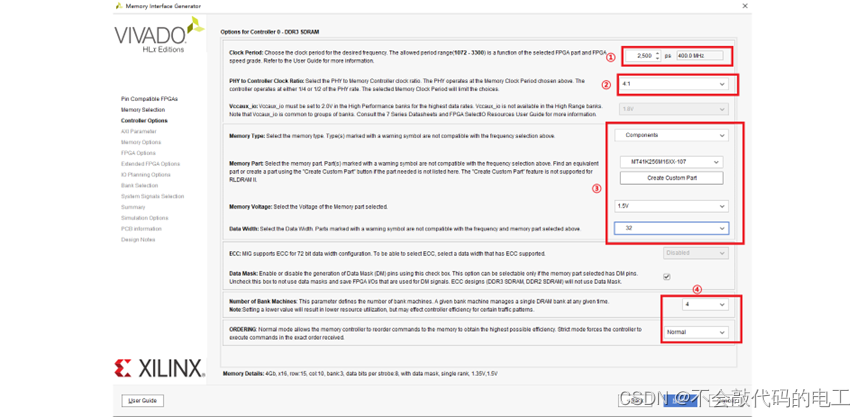

(6)Controller Options,DDR3 SDRAM配置。

①Clock Period,这个时钟为DDR3 IO接口时钟,即CK/CK#管脚时钟,图中配置为400MHZ;

②PHY to Controller Clock Ratio:DDR3 IO接口时钟和DDR3 MIG IP核用户接口时钟ui_clk比例,如①Clock Period=400MHZ,此处设置4:1,则,ui_clk=400MHZ/4=100MHZ.

③该部分设置为DDR3芯片的特性。

Memory Part,IP核给出了很多定制好的镁光系列芯片,用户可以根据自己板载DDR3直接选择,如果器件参数不能满足需求,也可以自己输出DDR3芯片相关参数,即点击Create Custon Part即可进入参数编辑页面。此处选择MT41K256M16XX-107/125;

Memory Voltage,设置存储器电压,板载为1.5V芯片,故此处选择1.5V

Data Width,选择DDR3数据位宽,板载为2片16bit DDR3,公用控制和地址,组成32bit位宽数据总线,故此处选择32;ECC校验只支持72bit位宽,故不能选择。

Data Mask,数据屏蔽位,使能后,IP核会例化相应data mask接口,此处选择使能。

④Number of Bank Machines,默认选择4;

ORDERING,选择默认Normal

(7)Memory Options,DDR3 MIG IP配置

①Input Clock Period,输入时钟设置,该时钟为DDR3 MIG IP核输入时钟,及IP核内部PLL源时钟,此处选择5000ps(200MHZ)

②Read Burst Type and Length,读突发长度和类型,DDR3只支持突发长度BL=8,此处选择突发类型为Sequential

③Output Driver Impedance Control,变成输出buffer阻抗,此处选择RZQ/7

④Controller Chip Select Pin,控制器片选信号选择,此处选择Enable

⑤On Die Termination(ODT),片上端接大小,此处选择RZQ/4

⑥Memory Address Mapping Selection,存储器地址映射,此处选择{Bank,Row,COLUMN}寻址方式

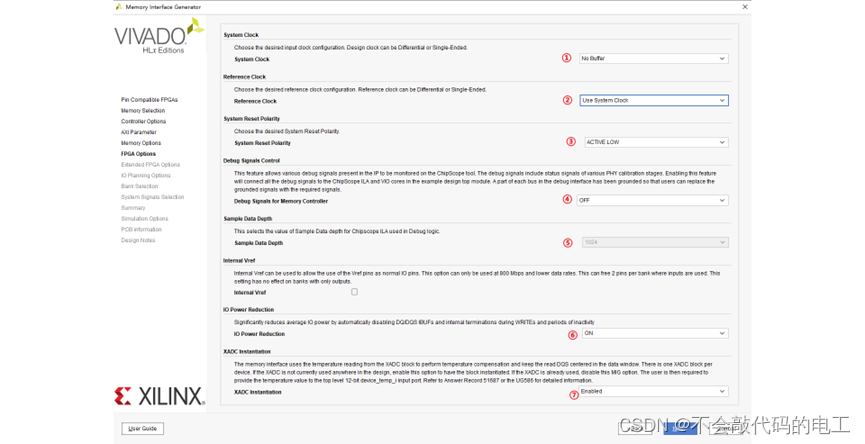

(8)DDR3 MIG IP时钟、复位、参考电压等配置

①System Clock,系统时钟输入方式,可选择单端、差分或者No Buffer,此处选择No Buffer

②Reference Clock,参考时钟,可选择单端,差分或者No Buffer或者Use System Clock,此处选择Use System Clock,即200MHZ时钟

③System Reset Polarity,IP核复位信号极性,此处选择ACTIVE LOW,即低电平复位

④Debug Signals for Memory Controller,是否选择存储器调试接口,此处选择No

⑤Sample Data Depth,是否使用 内部参考电压,IP核支持DDR3参考电压输出,此处不勾选,即使用板载参考电压

⑥IO Power Reduction选择IO功耗降低,此处选ON,即打开功耗降低功能

⑦XADC Instantiation是否例化XDAC,此处选择Enable

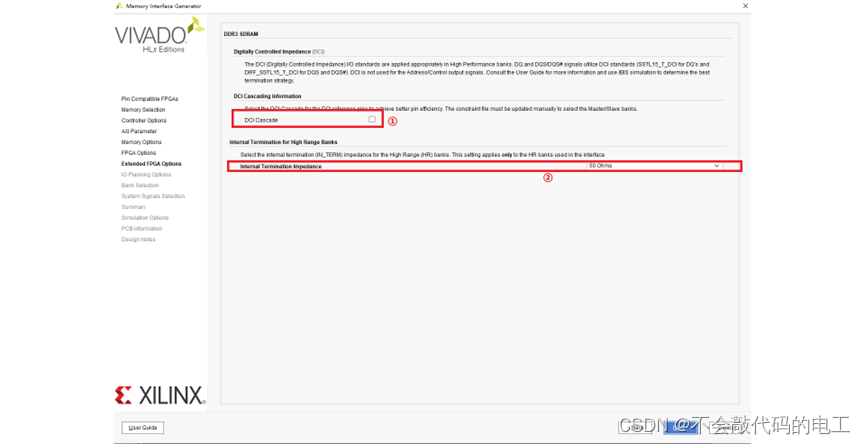

(9)FPGA内部端接及DCI级联设置

①DCI Cascade,DCI级联选择,这里不勾选

②Internal Termination Impedance,内部端接阻抗,此处选择50 ohms

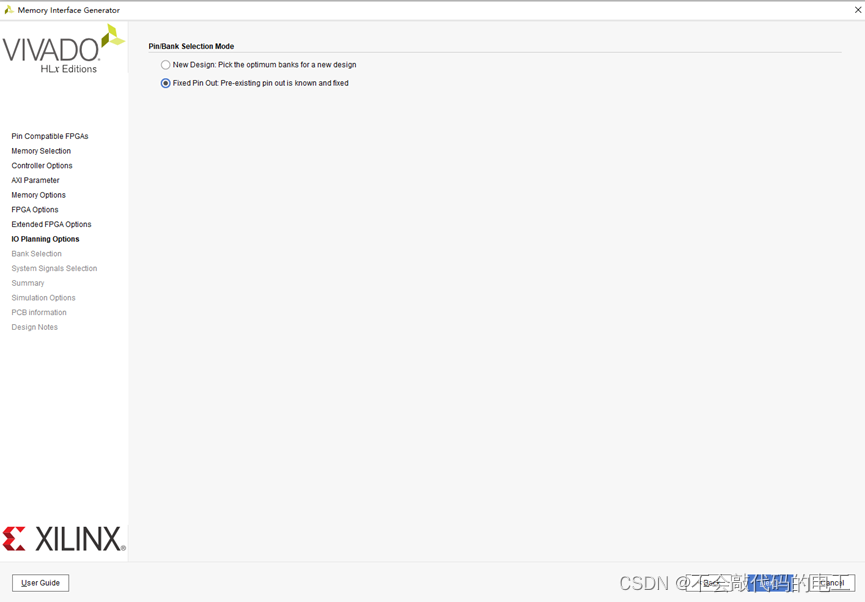

(10)选择Fixed Pin Out

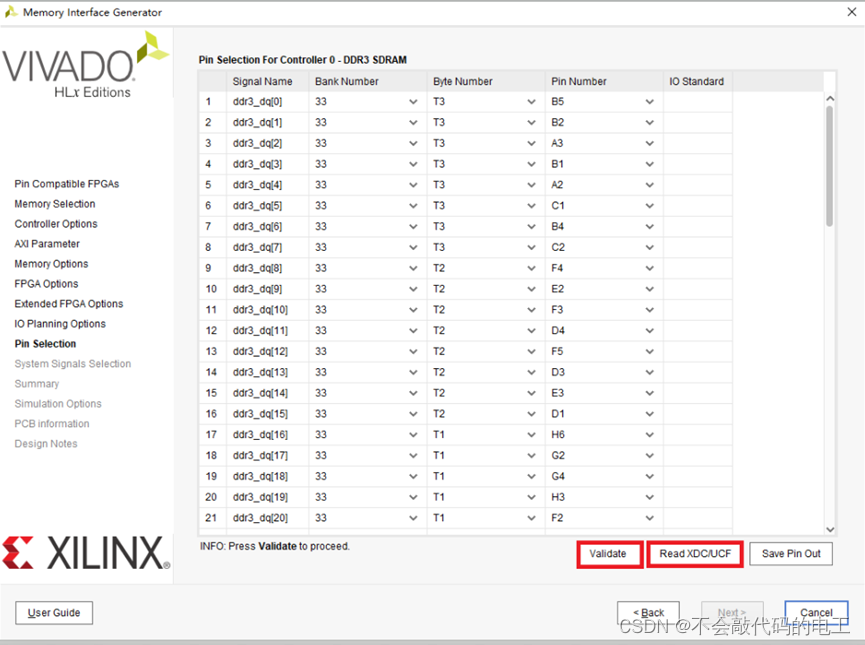

(11)配置DDR3 SDRAM IO管脚分配。