- 1国产信创服务器软硬件兼容情况2 --- x86架构

- 2存储计划:自动kill掉死锁进程id_kill -segv id

- 3基于稀疏表示的人脸识别

- 496、基于STM32单片机倒车雷达超声波测距报警系统设计_stm32超声波雷达

- 5Redis连接报错“NOAUTH Authentication required”解决方案_(error) noauth authentication required.

- 6python正则表达式爬取网页数据_常用正则表达式爬取网页信息及HTML分析总结

- 7基于vue3 + TS项目中安装ESLint工具_eslint-plugin-vue 配置

- 8Streamlit 讲解专栏(十二):数据可视化-图表绘制详解(下)_streamlit 支持动态图表吗

- 92023HW红队作战工具

- 10透视数字人克隆直播系统:科技革新下的全新互动体验

ARM Cortex-A 系列处理器天梯图_arm a53是a7的多少倍

赞

踩

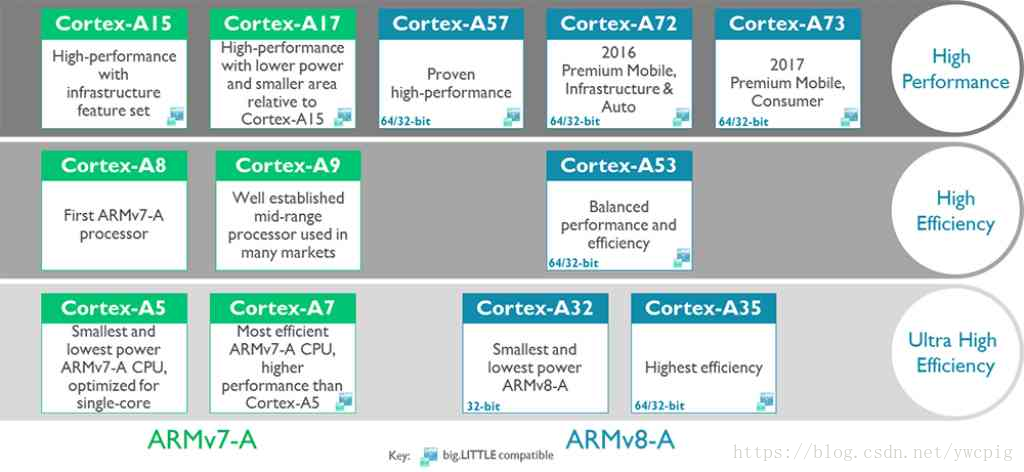

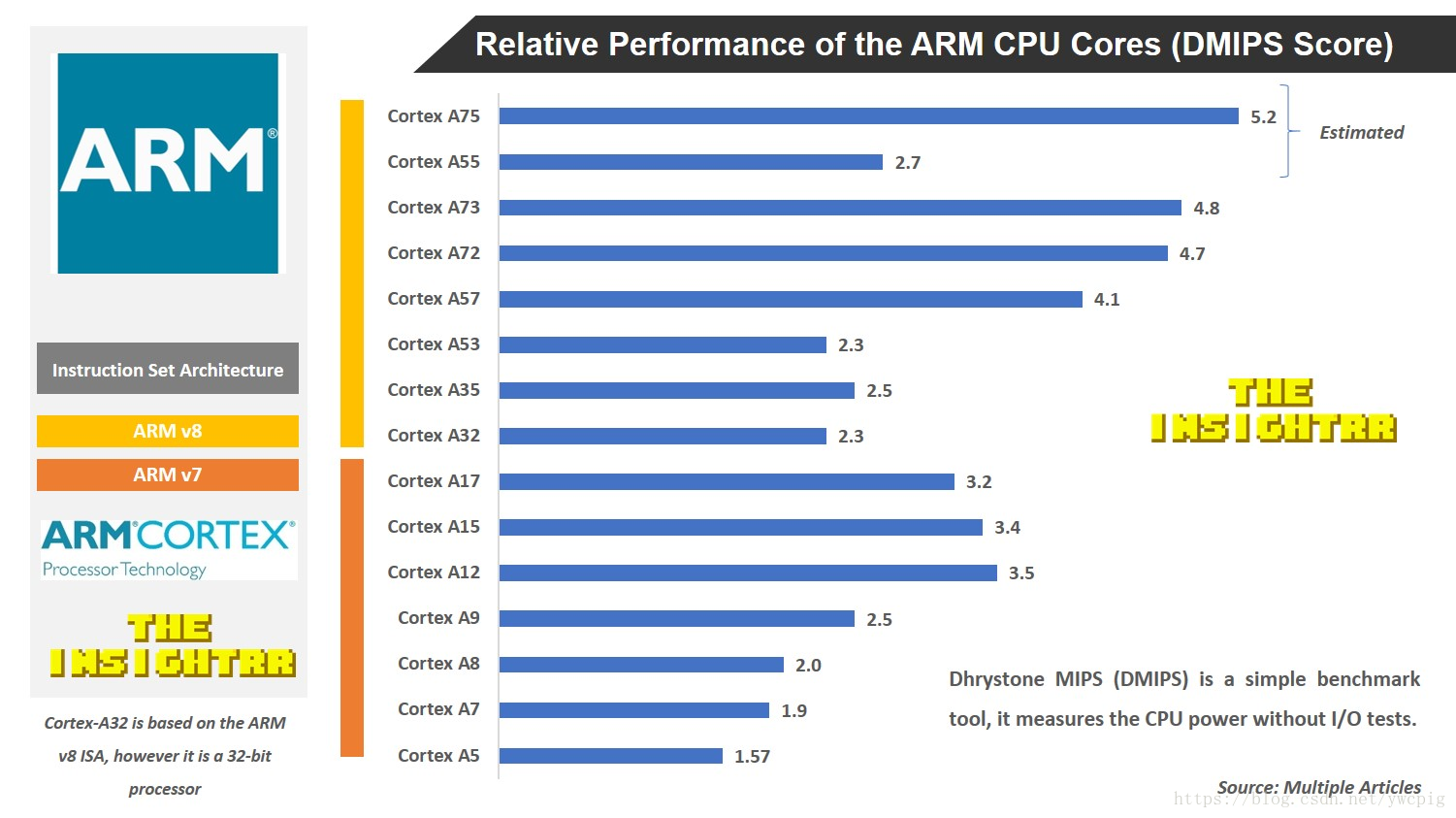

ARM Cortex-A Series Processors

ARM Cortex A53 Versus CortexA15

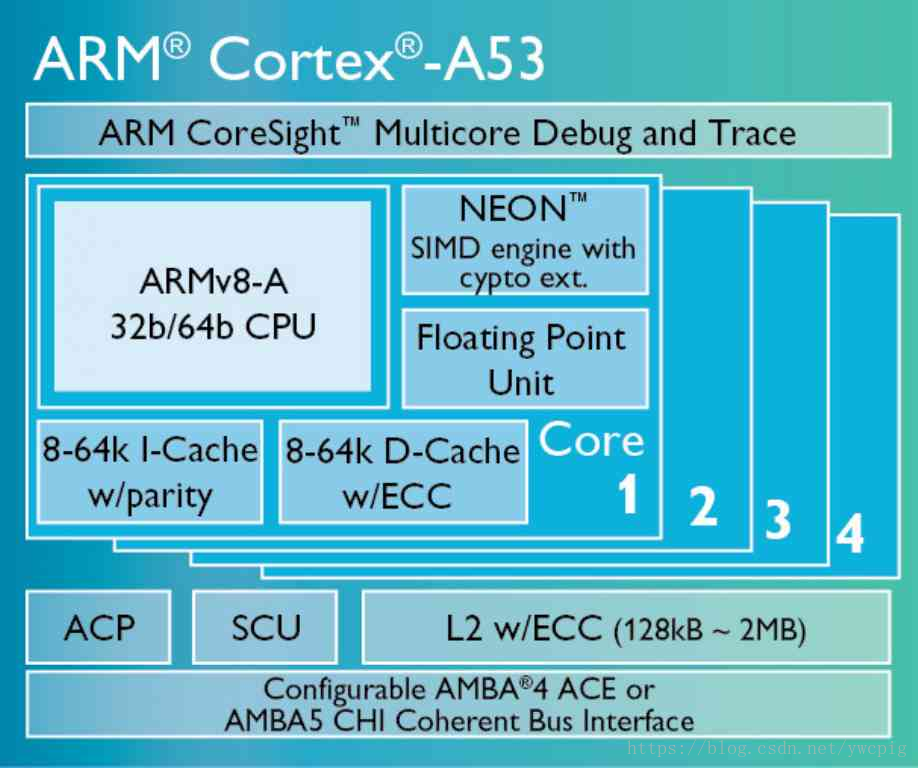

The Cortex A53 uses the ARMv8-A architecture to support 32-bit ARMv7 code and 64-bit AArch64 execution state. The Cortex-A53 processor architecture was released in 2012 designed for reduced power consumption and improved energy efficiency. It offers better performance than the Cortex-A7 processor and can be used as a stand-alone major application processor, or with the Cortex-A57 processor to form a big.LITTLE configuration. The Cortex-A53 offers higher performance than the Cortex-A9 at the same frequency.

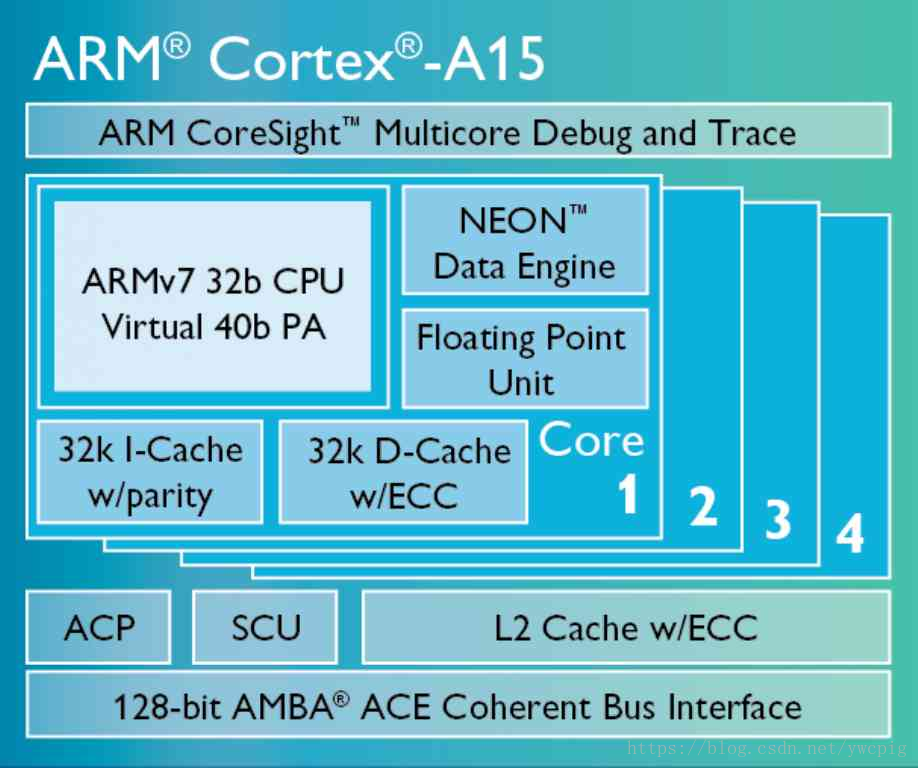

The Cortex-A15 was first released in 2010 and is based on the 32-bit ARMv7-A architecture. The Cortex-A15 has 32 KB of Instruction and Data Cache respectively. The Cortex-A15 has a pipeline depth of 15 whereas the Cortex-A53 has only 8, making the A15 faster. The ARM Cortex A15 was the next generation processor that ended up in a huge number of devices in 2013. The 249$ Chromebook and the Nexus 10 were both powered by Cortex A15-based SoCs.

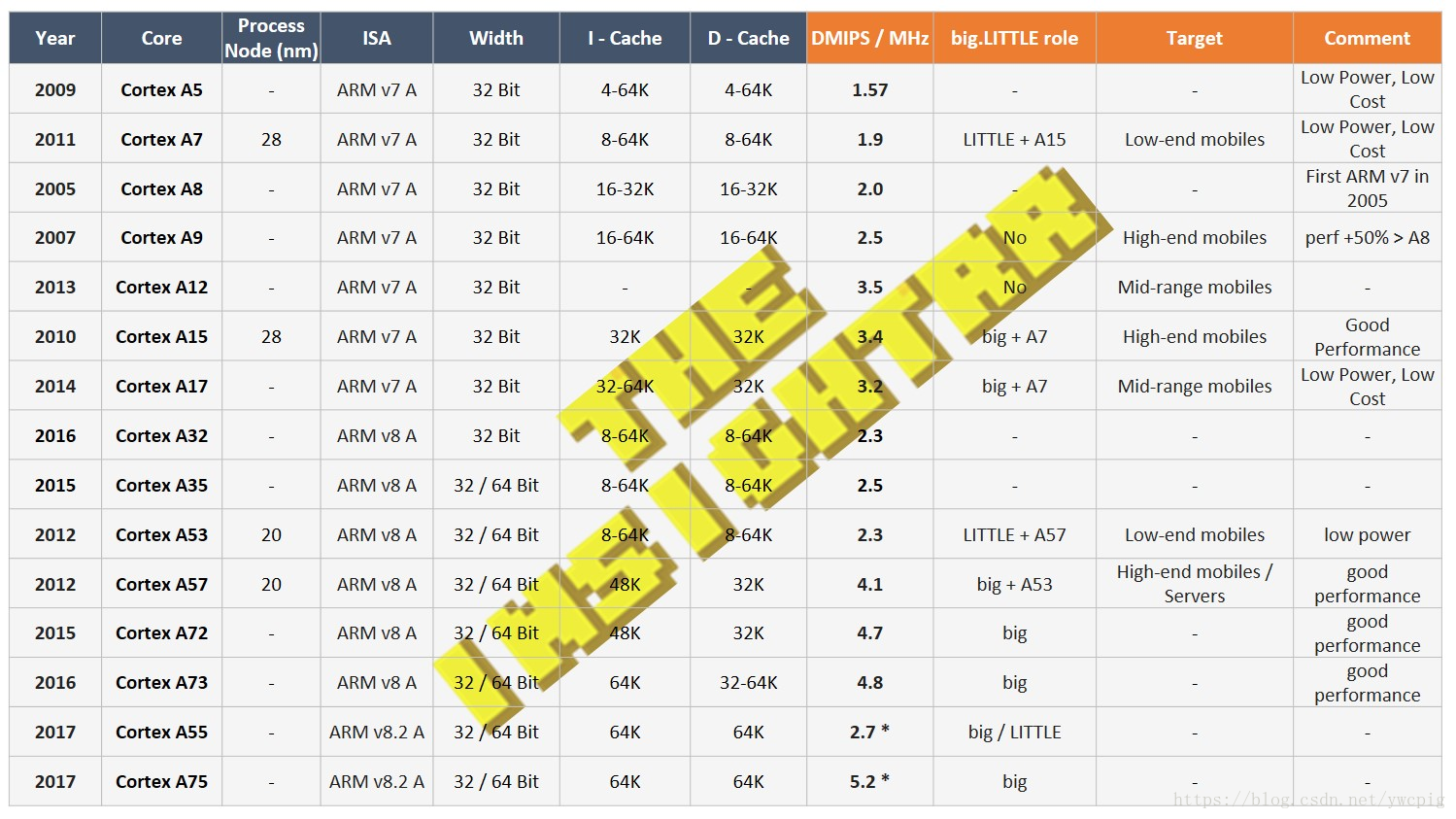

ARM Cortex A53 Versus Cortex A15 Benchmark

Dhrystone MIPS (Million Instructions Per Second)

The speed of a given CPU depends on many factors, such as the type of instructions being executed, the execution order etc. The MIPS (million instructions per second) value can be useful when comparing performance between processors made with similar architecture, However, MIPS doesn’t make sense when processors are based on different architecture. For this reason, DMIPS / MHz (Dhrystone MIPS) is considered whilst estimating the performance of CPUs, wherein DMIPS result is divided by CPU frequency to enable easy comparison of CPUs running at different clock rates.

DMIPS is a sort of a simple benchmark without I/O tests. The Dhrystone benchmark provides a measure of integer performance (no floating point instructions). The DMIPS/Mhz (Dhrystone MIPS/Megahertz) values are sourced from multiple websites. The DMIPS value for Cortex-A75 and Cortex-A55 are estimated using the performance increase as claimed by ARM. As claimed, “Cortex-A55 delivers significantly higher performance than the Cortex-A53 across the board, including integer (+18%)” and “Cortex-A75 processor provides a significant boost in single-thread performance using a fully out-of-order, variable-length, and symmetrical three-way superscalar pipeline. With over 20% more integer core performance”.