热门标签

热门文章

- 1TCN(Temporal Convolutional Network,时间卷积网络)

- 2分享10篇优秀论文,涉及图神经网络、大模型优化、表格分析_aaai2024论文在哪里看

- 3name ‘_C‘ is not defined(pytorch1.9.0在jupyter notebook上报错)_nameerror: name '_c' is not defined

- 4【深度强化学习】(4) Actor-Critic 模型解析,附Pytorch完整代码_actor critic

- 5ace2005 数据集预处理方法,oneie与JMEE方式_ace数据集

- 6【工具】1664- Codeium:强大且免费的AI智能编程助手

- 7景联文科技:2023人工智能数据标注行业现状分析?_数据标注接单平台2023

- 8数字人添加背景(heygen+剪映)_heygen数字人

- 9必读!信息抽取(Information Extraction)【关系抽取】_信息抽取和关系抽取一样吗

- 10codegeex和通义灵码辅助编程——以及通义灵码无法登陆的bug解决_codegeex 通义灵码

当前位置: article > 正文

DDS原理与FPGA实现_fpga dds实现 csdn

作者:Gausst松鼠会 | 2024-04-03 14:21:35

赞

踩

fpga dds实现 csdn

DDS信号发生器原理

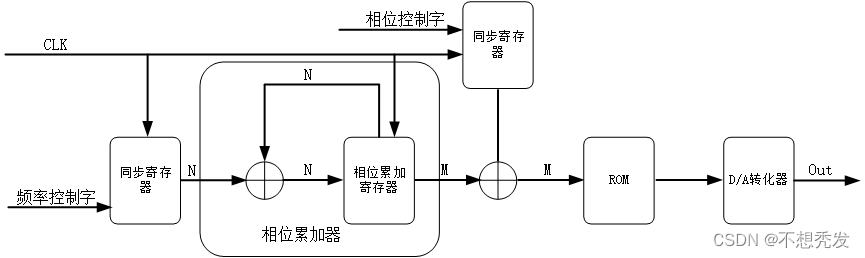

rom读取地址=频率控制字+相位累加器+相位控制字。DDS数字电路原理如图:

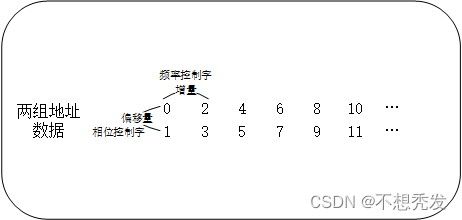

频率控制字改变rom地址增量,相位控制字改变rom地址偏移量。两者关系如图:

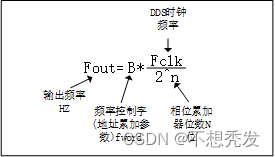

信号发生器输出信号频率与DDS时钟频率关系如下。

注

相位控制字寄存器位宽与rom位宽保持一致。

这里相位累加器位数为 N 位(N 的取值范围实际应用中一般为 24~32),相当于把正弦信号在相位上的精度定义为 N 位,所以其分辨率为1/2^n。

N越大信号输出频率精度越高,输出频率下限值越低。

相位控制字改变信号初相位置。

代码示例

module dds_test( input clk , input rst_n , input [31:0] f_word , input [11:0] p_word , output [15:0] data_out //rom输出位宽 ); reg [31:0] r_f_word ; //频率控制字寄存器 reg [11:0] r_p_word ; //相位控制字寄存器 位宽与rom位宽保持一致 reg [31:0] acc ; //相位累加寄存器 reg [7:0] address_rom ; //rom地址寄存器 假设rom地址位宽为8位 //同步寄存器 always @(posedge clk or negedge rst_n) if(!rst_n) r_f_word <= 32'b0 ; else r_f_word <= f_word ; always @(posedge clk or negedge rst_n) if(!rst_n) r_p_word <= 12'b0 ; else r_p_word <= p_word ; always @(posedge clk or negedge rst_n) if(!rst_n) acc <= 32'b0; else acc <= acc + r_f_word ; always @(posedge clk or negedge rst_n) if(!rst_n) address_rom <= 12'b0; else address_rom <= acc[31:24] + r_p_word; //rom列化 dist_mem_gen_0 dist_mem_gen_0_inst ( .a(address_rom), // input wire [7 : 0] a .spo(data_out) // output wire [15 : 0] spo ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/355864?site

推荐阅读

相关标签