热门标签

热门文章

- 1给自己的网页添加MarkDown编辑器_dw如何添加类似markdown的编辑器

- 22024金三银四必备:Java后端开发面经整理【35个技术栈合集】

- 3XSS漏洞学习笔记_span标签xss

- 4Vue + Axios - HTTP POST 请求示例 (外网地址)_vue发送post请求

- 5Datawhale用免费GPU线上跑AI项目实践课程任务一学习笔记。部署ChatGLM3-6B模型

- 6JWT详解、JJWT使用、token 令牌

- 7vue项目生成二维码_vue2 生成二维码

- 8Android控件之高级控件——ListView、cardView、屏幕适配_cardview listview

- 9Meta翻译大模型可模仿语气语速!AI再也不“莫得感情”了|GitHub 9k标星_语气模拟

- 10常见的系统架构设计介绍_系统架构设计包括哪些内容

当前位置: article > 正文

FPGA控制AD7606_AD7606解读_csdn ad7606

作者:Gausst松鼠会 | 2024-05-07 23:34:33

赞

踩

csdn ad7606

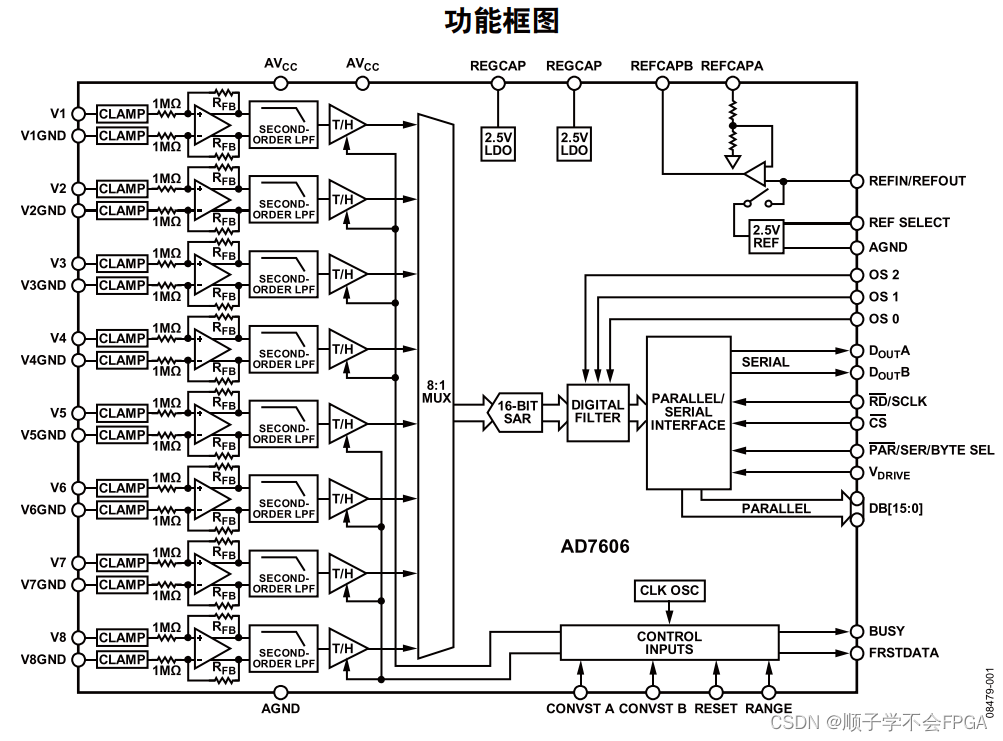

一、AD7606解读

AD7606特点:

- 8通道同步采样

- 模拟通道数为8

- 分辨率:16bit,即最小采样的电压为5V/(2^16) = 0,00007V,即数字量的1就代表模拟量的0,00007V,2代表0,00014V

- 有效位数ENOB:真正的有效分辨率,实际可以达到的分辨率,一般比手册标注的要低3-4bit,即12-13bit的分辨率。

- 数字量输出形式:二进制补码

ADC工作原理:

6. 采样:对模拟值进行采样

7. 保持:将开关保持一段时间以将电容充电到采集电压值

8. 量化 编码:将电压值转化为数字量,积分型、SDR等

采样是8通道同步采样的,但采样值是一个一个通道传递出来的。

CLK OSC:时钟振荡器,反相器级联产生时钟信号

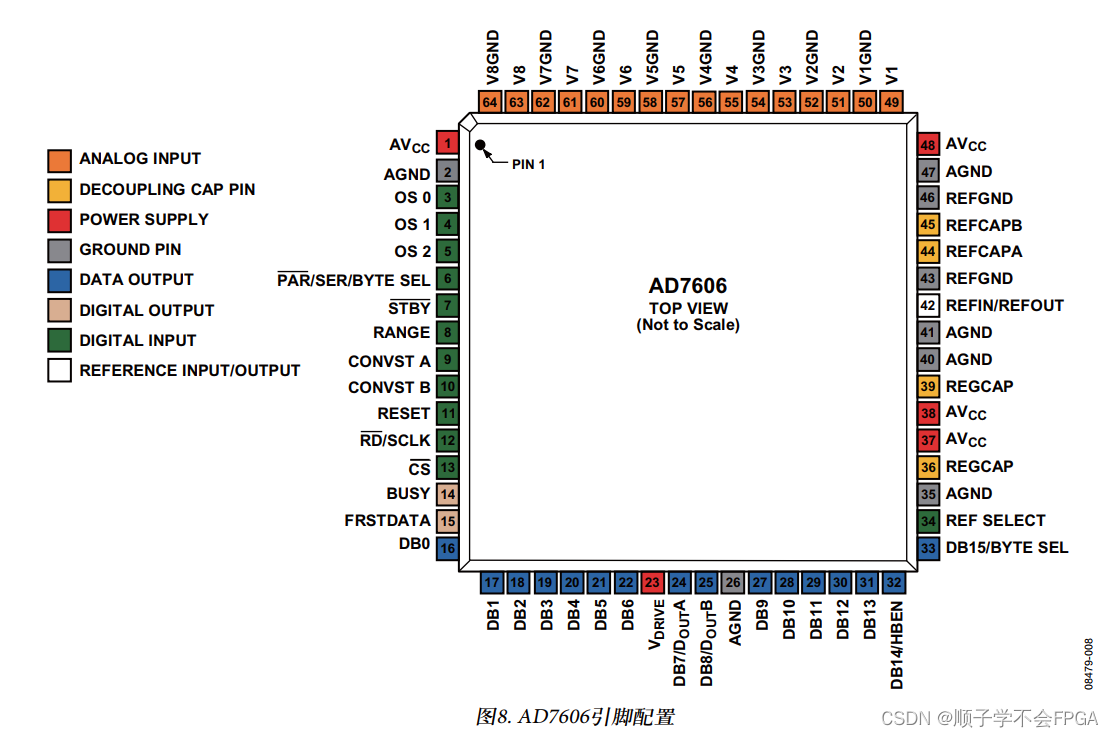

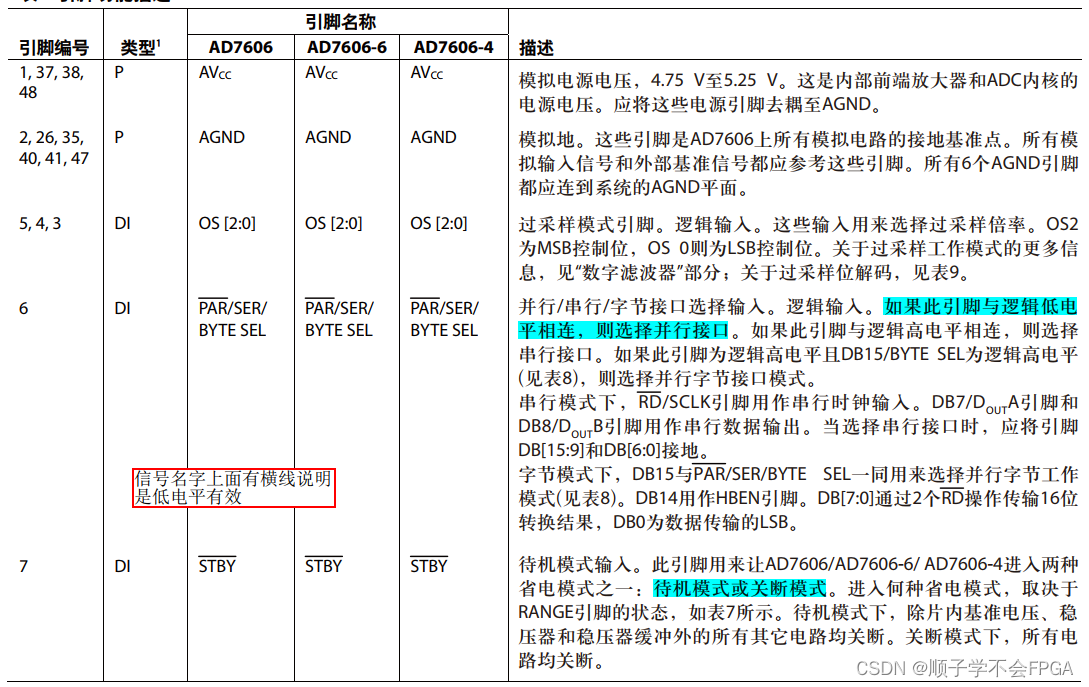

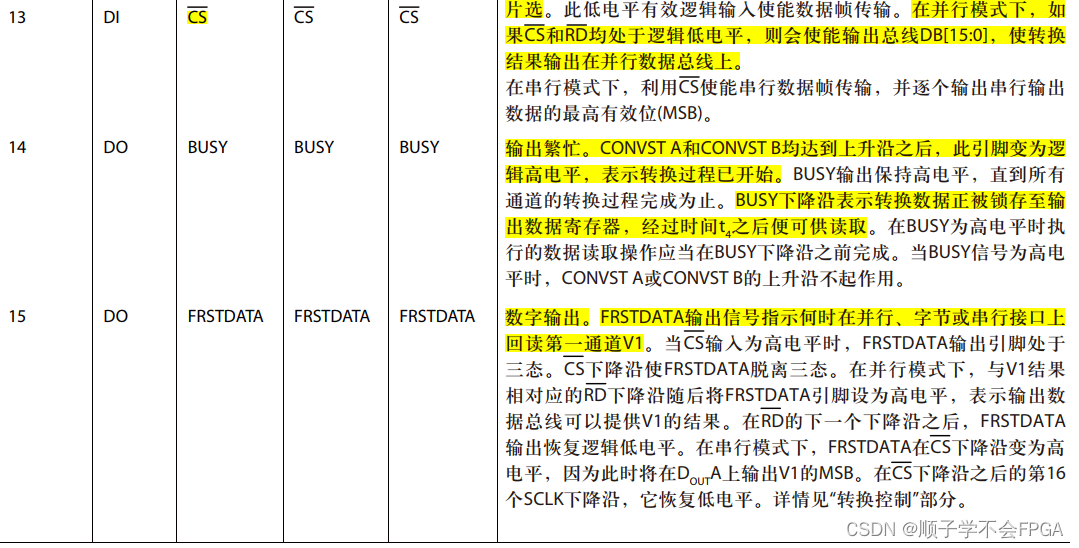

二、引脚说明

重要信号说明:

OS:过采样,采样多个点求平均值

PAR/SERBYTE SEL:并行、串行、字节选择,我们选择并行,设置为0.

STBY:待机模式控制,低电平进入待机模式

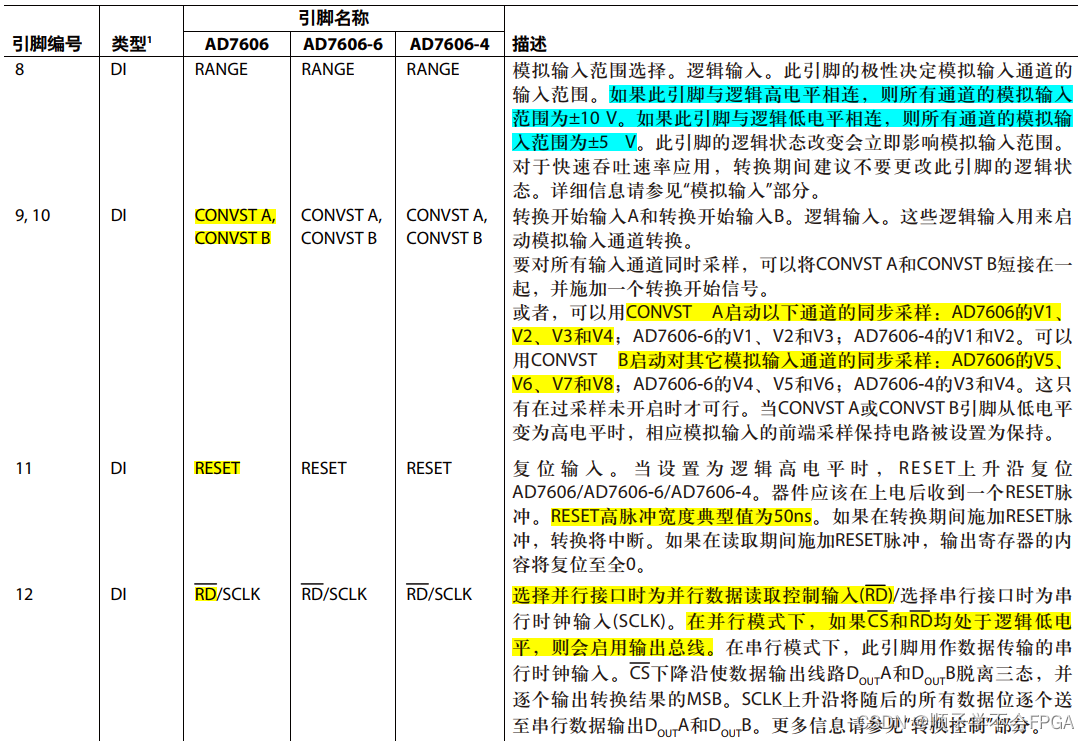

CONVST A/B:驱动ADC芯片模拟信号转换为数字信号的引脚,A负责控制低四个通道的转换,B负责高四个通道

RESET:复位,高有效,持续50ns以上

RD/SCLK:读数据控制信号,在并行模式下为RD

CS:片选信号

BUSY:芯片繁忙指示信号

FIRSTDATA:第一通道数据指示信号,表示当前读出的数据为第一通道数据

DB0-DB15:读数据通道

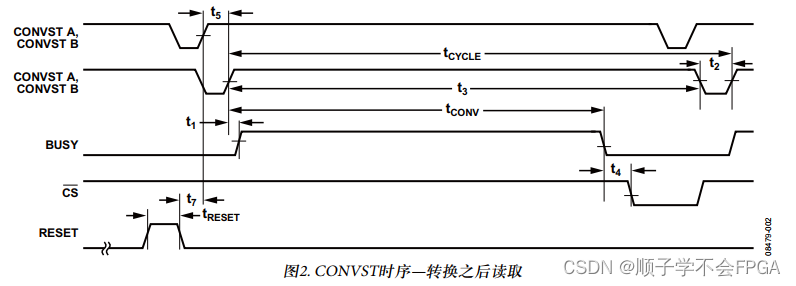

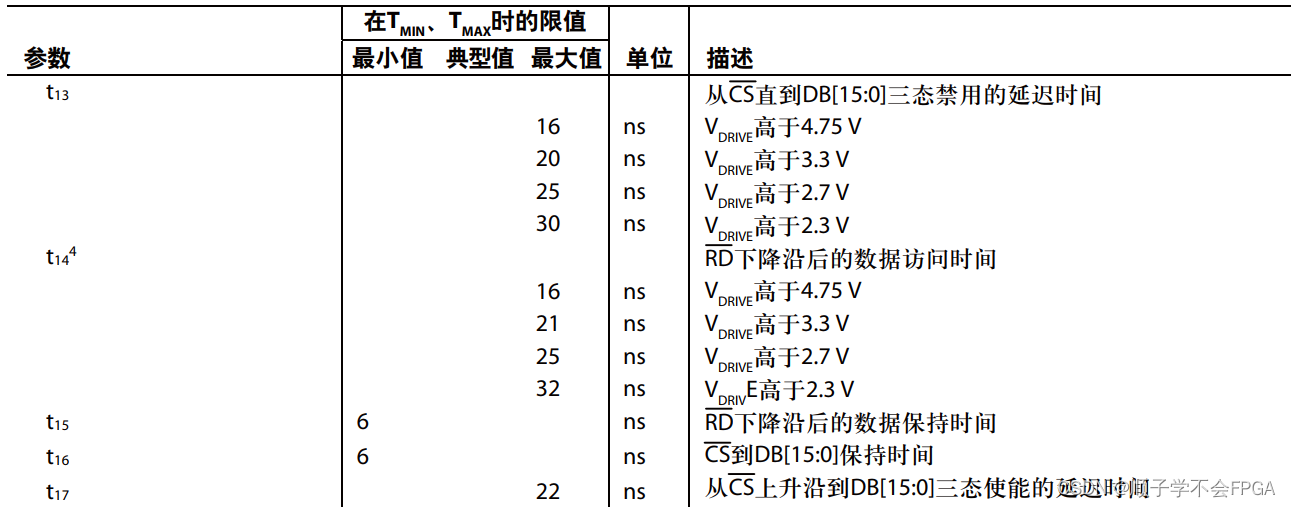

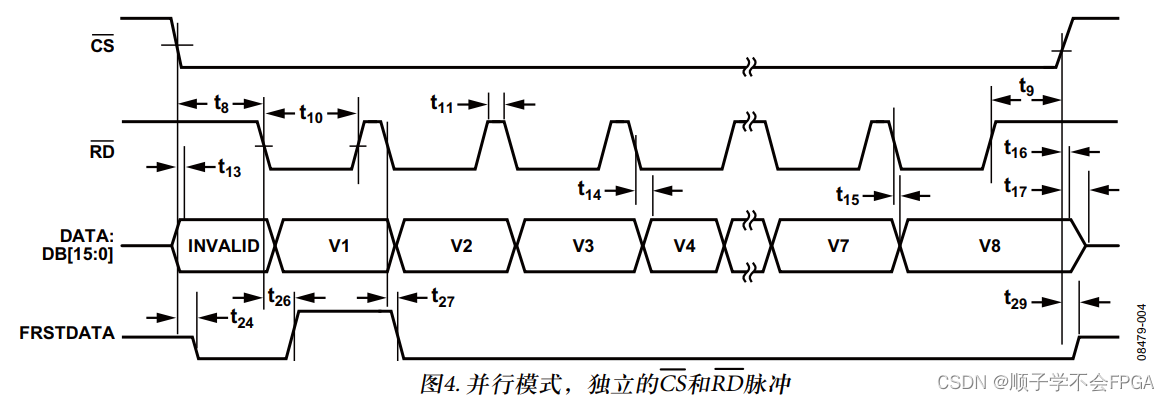

三、时序图

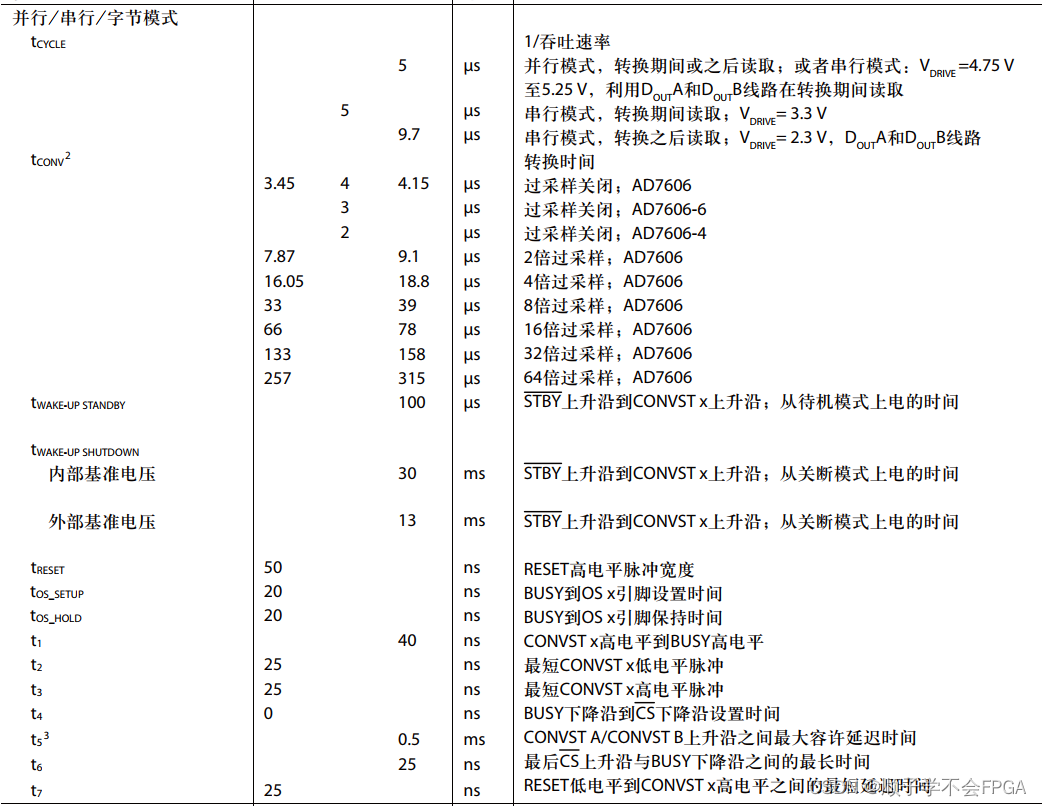

转换过程时序:

t5:CONVSTA/B上升沿之间最大0.5ms

t1:CONVSTA/B上升沿启动后BUSY需要最多40ns才拉高,即用户开启转换后需要等40ns再去读忙信号

t2:最短CONVSTx低电平脉冲25ns

t3:最短CONVSTx高电平脉冲25ns

t4:BUSY下降沿到CS信号下降沿设置时间最小值为0

t7:RESET低电平到CONVSTx高高电平之间最短延迟时间25ns

tRESET:复位高电平脉冲宽度最小为50ns

tCYCLE:1/吞吐速率,并行状态下最大5us

tCONV:转换时间

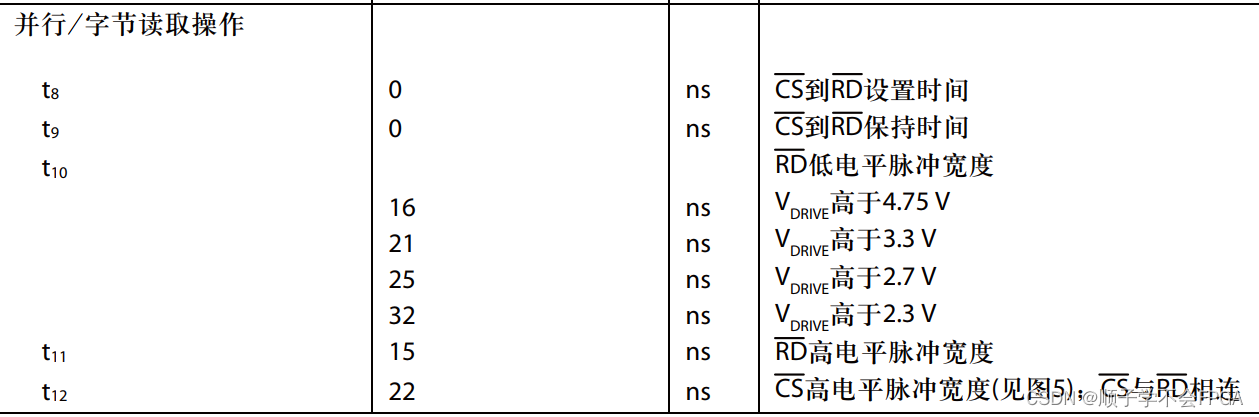

读数据过程

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/551777

推荐阅读

相关标签