热门标签

当前位置: article > 正文

【数字IC/FPGA】Verilog中的force和release_verilog force release

作者:小丑西瓜9 | 2024-05-04 09:37:48

赞

踩

verilog force release

在Verilog中,将force用于variable会覆盖掉过程赋值,或者assign引导的连续(procedural assign)赋值,直到release。

下面通过一个简单的例子展示其用法:

加法器代码

module adder

(

input logic [31:0] a,

input logic [31:0] b,

output logic [31:0] sum

);

//sum

assign sum = a + b;

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

测试平台代码(主要用于产生激励)

module test; logic [31:0] a; logic [31:0] b; logic [31:0] sum; initial begin forever begin a = $urandom % 128; b = $urandom % 128; #10; end end // initial begin #200 force u_adder.a = 32'd33; force u_adder.b = 32'd66; #200 release u_adder.a; release u_adder.b; end initial begin $fsdbDumpfile("adder.fsdb"); $fsdbDumpvars(0); $fsdbDumpMDA(); end initial begin #1000 $finish; end //inst adder u_adder ( .a (a ), .b (b ), .sum(sum) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

如上所示,正常情况下,u_adder模块的a和b端口由testbench中的a和b信号驱动,然而,在时间为200ns处,u_adder模块的输入u_adder.a和u_adder.b被强制固定为33和66,如下代码所示。

#200

force u_adder.a = 32'd33;

force u_adder.b = 32'd66;

- 1

- 2

- 3

又经过200ns后,release语句释放了u_adder.a和u_adder.b的强制赋值,如下代码所示:

#200

release u_adder.a;

release u_adder.b;

- 1

- 2

- 3

编写makefile文件,对上述代码进行仿真,其中,makefile文件的内容如下:

all: listfile com sim verdi clean listfile: find -name "*.sv" > filelist.f com: vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,--no-as-needed -sverilog -debug_access -timescale=1ns/10ps \ -f filelist.f -l com.log -kdb -lca sim: ./simv -l sim.log +fsdb+force verdi: verdi -sv -f filelist.f -ssf *.fsdb -nologo & clean: rm -rf csrc *.log *.key *simv* *.vpd *DVE* rm -rf verdiLog *.fsdb *.bak *.conf *.rc *.f

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

这里,在运行simv文件时,需要加上+fsdb+force选项,即:

./simv -l sim.log +fsdb+force

- 1

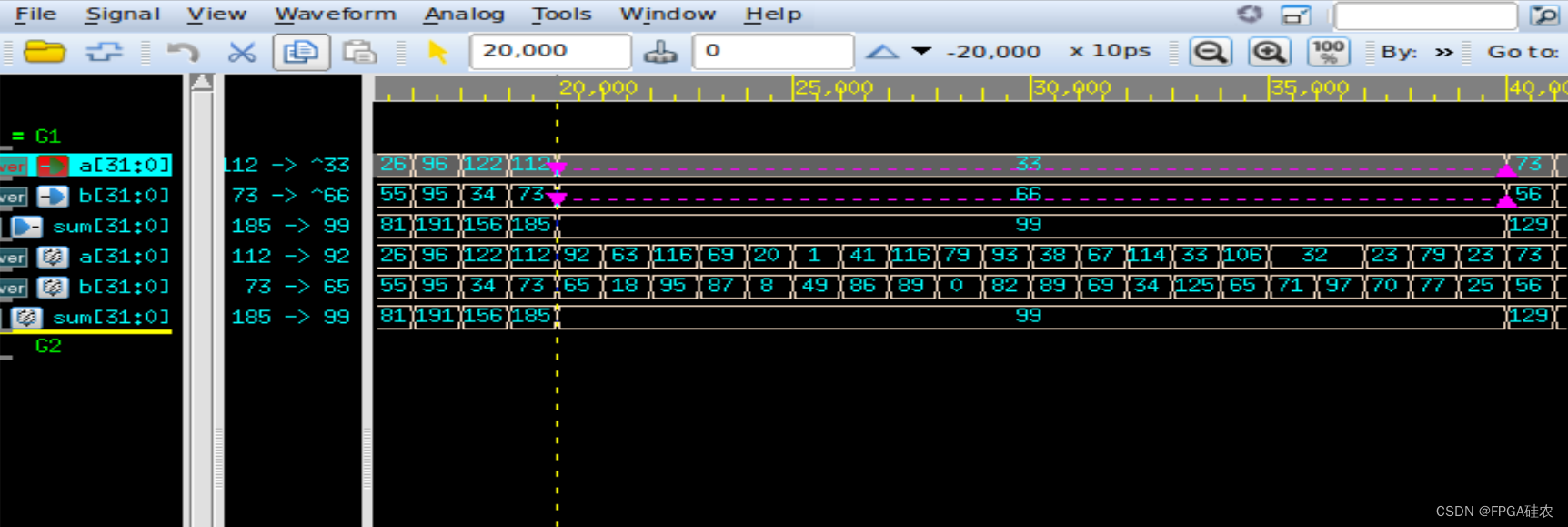

运行verdi查看波形,有下图:

可以看到,第200-400ns,加法器实际的输入a和b被固定为33和66,其值不再与testbench中的a, b绑定。另外,图中的紫色三角形分别表示该信号被force和release的时刻,被force强制指定的值,在显示的时候,前面会有一个^符号,例如上图中的^33和^66。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/小丑西瓜9/article/detail/533837

推荐阅读

相关标签