- 1《python每天一小段》--(9)使用Paramiko库,批量操作linux服务器_怎么在jupyter notebook中安装paramiko

- 2神经网络与深度学习课程作业-4-循环神经网络与NLP_关于循环神经网络习题

- 3如何将D3.js的强交互延续到Python中?

- 4第六章树和二叉树作业1—二叉树_已知一棵二叉树的树形如下图所示,若其后序遍历序列为 f, d, b, e, c, a,则其先(前

- 5自然语言处理之文本情感分析_自然语言处理和情感分析

- 6【看表情包学Linux】(9) 缓冲区的概念 | Git 三板斧 | 实现简易进度条_git缓冲区大小是什么

- 7机器人系统ros2-开发实践03-监听节点的参数变化(C++)

- 8解锁Apache Shiro:新手友好的安全框架指南(一)——整体架构与身份认证_apache shiro的配置包括安全管理器(3)

- 9自动化机器学习流水线:基于Spring Boot与AI机器学习技术的融合探索_springboot集成ai

- 10srilm使用

Verilog设计实例(7)基于Verilog的数字电子钟设计_基于verilog的数字时钟设计

赞

踩

写在前面

前段时间,有几个小伙伴向我请教数字电子钟设计的问题,这个问题我在之前的BCD计数器以及数码管显示问题中已经分开谈过了,既然大家还有需求,不妨在这里集中总结一下!

- 个人微信公众号: FPGA LAB

- 个人博客首页

正文

设计要求

基于模块化的设计思想, 采用 Verilog HDL 语言设计一个能进行时、分、秒计时的二十四小时制的数字电子钟, 并具有整点报时功能。 采用数码管进行时间显示,要求显示格式为:小时-分钟-秒钟。

在 EDA 软件中完成数字电子钟的源代码设计, 并进行仿真, 仿真结果要能够体现出时、分、秒各自的跳变过程, 并且能够给出整点报时控制信号的变化过程。

1、独立完成设计任务;

2、详细阐述设计方案,绘制系统设计框图;

3、详细阐述系统调试方案,编写测试文件并进行仿真;

4、撰写设计报告。详细阐述设计思想、指标论证、方案确定、结果分析等内容,并对所完成的设计做出总结和评价,对设计过程中遇到的问题及解决方法进行阐述。

我只关注前面的部分,就是设计一个具有时、分以及秒计时的二十四小时计时器,还具有整点报时,并用数码管显示!

设计思想

首先是时、分以及秒的计数问题,对于分和秒的情况,肯定是用模60计数器,但是你能直接计数到59然后清零吗?包括时计数器,一定是模24计数器,但是你能直接计数到23清零吗?

如果没有数码管显示的需求肯定没问题,我用十进制显示,仿真完美!

但是需要数码管显示的话,我们需要6个数码管,时、分以及秒各需要两个!拿小时计数器来说,由于小时就有两个数字,十分位和个位,使用两个数码管显示小时,第一个数码管显示十分位,第二个数码管显示个位!明显是要将十分位和个位分开显示,需要使用8421BCD码计数器来处理。

如果使用十进制的话,10就相当于0xa,如何显示呢?显示0a,这显示是不直观的,你家的时钟用a,b,c等等显示时间计数,你会不会打死设计师呢!

因此,我们使用8421BCD码来进行计数,这一步完成了就解决了80%的问题!

其次,便是数码管显示的问题,数码管显示时、分以及秒需要6个数码管,我们采用动态扫描的方式来显示,也就是控制片选轮流点亮数码管,只要你轮流的速度足够快,肉眼就会认为所有数码管一直亮!

说了那么多,其实就总结为如下两个主要模块!

- 设计计时模块,用到模60计数器,模24计数器;

- 设计数码管显示模块

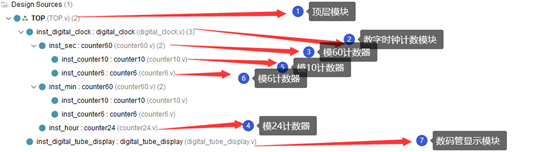

我们严格遵守模块化的思想,设计文件结构如下:

仿真文件结构:

设计文件

设计思想已经谈过了,更多的细节请看参考资料,这里给出部分设计文件,如果需要全部设计文件的,可以关注我的微信公众号:FPGA LAB,后台回复:数字时钟,我会发给你资源设计文件链接!

模60计数器

由于分和秒计数都是60进制,因此,模60计数器模块是针对分秒计数功能的!

模60计数器的设计采用的是8421BCD码计数方式,由模10计数器以及模6计数器组成:

//模60计数器的Verilog HDL设计 module counter60(clk, rst_n, en, dout, co); input clk, rst_n, en; output[7:0] dout; output co; wire co10_1, co10, co6; wire[3:0] dout10, dout6; counter10 inst_counter10(.clk(clk), .rst_n(rst_n), .en(en), .dout(dout10), .co(co10_1)); //模10计数器的进位为co10_1 and u3(co10,en,co10_1); //co10_1与en的与为co10 counter6 inst_counter6(.clk(clk), .rst_n(rst_n), .en(co10), .dout(dout6), .co(co6)); //co10_1与en的与为co10,作为模6计数器的使能信号 and u4(co, co10, co6); //模6计数器的进位和模6的使能信号co10的与作为模60计数器的进位 assign dout = {dout6,dout10}; //模60计数器的输出,高位为模6计数器的输出,低位为模10计数器的输出,读法是8421BCD码读法 endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

可见,模60计数器例化了模10以及模6计数器,下面给出模10以及模6计数器的设计:

模10计数器

//模10计数器模块 module counter10(clk, rst_n, en, dout, co); input clk, rst_n, en; output[3:0] dout; reg [3:0] dout; output co; always@(posedge clk or negedge rst_n) begin if(!rst_n) dout <= 4'b0000; //系统复位,计数器清零 else if(en) if(dout == 4'b1001) //计数值达到9时,计数器清零 dout <= 4'b0000; else dout <= dout + 1'b1; //否则,计数器加1 else dout <= dout; end assign co = dout[0]&dout[3]; //当计数达到5(4'b1001)时,进位为1,计数值为其他,都没有进位 endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

模6计数器

//模6计数器模块 module counter6(clk, rst_n, en, dout, co); input clk, rst_n, en; output[3:0] dout; reg [3:0] dout; output co; always@(posedge clk or negedge rst_n) begin if(!rst_n) dout <= 4'b0000; //系统复位,计数器清零 else if(en) if(dout == 4'b0101) //计数值达到5时,计数器清零 dout <= 4'b0000; else dout <= dout + 1'b1; //否则,计数器加1 else dout <= dout; end assign co = dout[0]&dout[2]; //当计数达到5(4'b1001)时,进位为1,计数值为其他,都没有进位 endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

如果你觉得这样太繁琐,可以合起来写呀!

再给出模24计数器设计:

//8421BCD码计数器,模24 module counter24(clk, rst_n, en, dout); input clk, rst_n, en; output[7:0] dout; reg[7:0] dout; always@(posedge clk or negedge rst_n) //异步复位 begin if(!rst_n) //复位信号有效时,输出清零 dout <= 8'b00000000; else if(en == 1'b0) //计数使能无效时,输出不变 dout <= dout; else if( (dout[7:4] == 4'b0010)&&(dout[3:0] == 4'b0011) ) //计数达到23时,输出清零 dout <= 8'b00000000; else if(dout[3:0] == 4'b1001) //低位达到9时,低位清零,高位加1 begin dout[3:0] <= 4'b0000; dout[7:4] <= dout[7:4] + 1'b1; end else //上述情况都没有发生,则高位不变,低位加1 begin dout[7:4] <= dout[7:4]; dout[3:0] <= dout[3:0] + 1'b1; end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

将三面的模块例化进数字时钟模块内,构成24小时计时器!

//数字时钟计数器 module digital_clock( input clk, input rst_n, input en, output [7:0] hour, output [7:0] min, output [7:0] sec, output tweet ); wire co_sec1,co_sec,co_min,co_min1; counter60 inst_sec(.clk(clk), .rst_n(rst_n), .en(en), .dout(sec), .co(co_sec1)); and inst_and_sec(co_sec,en,co_sec1); counter60 inst_min(.clk(clk), .rst_n(rst_n), .en(co_sec), .dout(min), .co(co_min1)); and inst_and_min(co_min,co_sec,co_min1); assign tweet = (min == 0)&&(sec == 0) ? 1 : 0; // report time signal counter24 inst_hour(.clk(clk), .rst_n(rst_n), .en(co_min), .dout(hour)); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

代码部分就展示到这里吧,全部贴出来占用太多空间,需要全部代码的可以在公众号FPGA LAB 后台回复:数字时钟!

仿真文件

仿真文件再简单不过了,只需要给出使能以及时钟即可!

module digital_clock_tb( ); reg clk; reg rst_n; reg en; wire [7:0] hour; wire [7:0] min; wire [7:0] sec; wire tweet; initial begin clk = 0; forever begin #5 clk = ~clk; end end initial begin rst_n = 0; en = 0; # 50 @(negedge clk) rst_n = 1; @(negedge clk) en = 1; // #10000000 $finish; end digital_clock inst_digital_clock( .clk(clk), .rst_n(rst_n), .en(en), .hour(hour), .min(min), .sec(sec), .tweet(tweet) ); endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

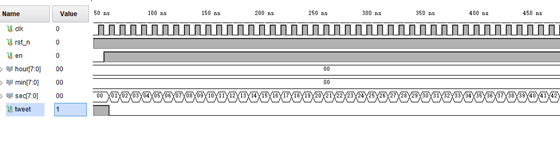

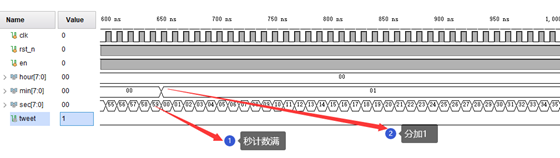

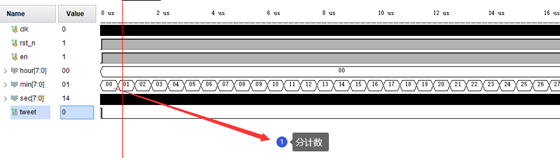

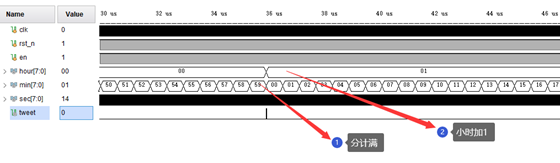

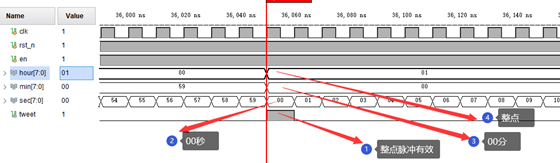

仿真波形

就到这里吧!

参考资料

交个朋友

-

个人微信公众号:FPGA LAB

-

知乎:李锐博恩