- 1深入浅出RabbitMQ:顺序消费、死信队列和延时队列_rabbitmq消费顺序性

- 2以太坊搭建联盟链_76a.one

- 3单相全桥逆变原理及仿真实验

- 4Android Studio Gradle

- 5微软发布新的Copilot+ PCs 是微软推出的一系列高性能、智能化的 Windows 个人电脑。

- 6leetcode 27. 移除元素_nums.erase

- 7华为OD机试Java - 螺旋数字矩阵

- 8西门子SICAR汽车行业标准程序及图纸详解,源码提供,适用于博途编写,含安全程序与安装要求

- 9Web系统常见安全漏洞介绍及解决方案-CSRF攻击_csrf通常和什么联合使用

- 10区块链入门教程(1)--概述_区块链开发入门

FPGA基本概念及资源整理——FPGA学习笔记<0>_野火fpga资料

赞

踩

目录

九.xilinx Zynq UltraScale+ MPSoC

零.前言

作者的“FPGA学习笔记”系列将采用野火 XILINX-Artix7-FPGA 升腾开发板作为学习平台进行学习,总结学习过程中的收获。

学习实践汇总

一.FPGA

1.FPGA——可编程逻辑器件,大家都知道。大家可能之前还做过电子线路实验,用过Quartus II,但是当看到各种各样的型号比如Xilinx Artix-7 XC7A35T、Altera Cyclone IV EP4CE10时完全不知道这是什么,推荐看一下:FPGA最全科普总结

大家还会看到Soc这个词,实际上就像是以前学的mcu:MCU, SOC 区别

2.关键名词:

可编程逻辑器件(PLD,Programmable Logic Device)

可编程整列逻辑(PAL,Progarmmable Array Logic)

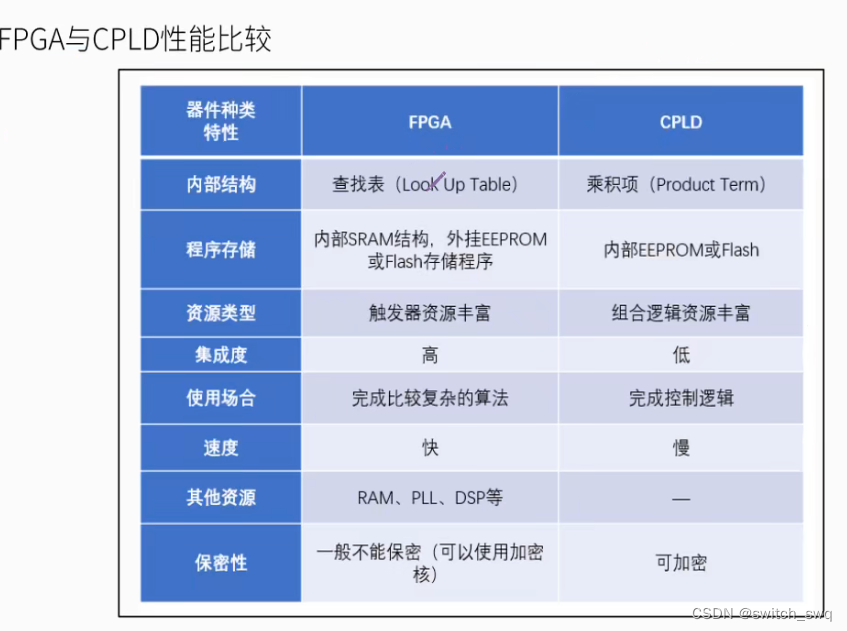

CPLD(Complex Progarmmable Logic Device)

FPGA(Field Programmable Gate Array)

FPGA配置模式:并行主模式为一片FPGA加一片EPROM的方式;主从模式可以支持一片PROM编程多块FPGA;串行模式可以采用串行PROM编程FPGA;外设模式可以将FPGA作为微处理器的外设,由微处理器对其进行编程

详细硬件介绍:参考图书或

二.FPGA+AI

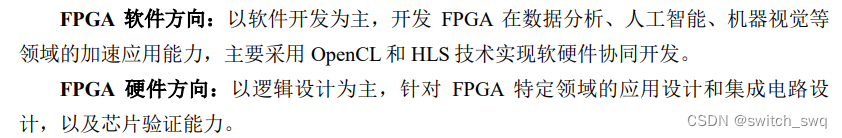

用FPGA来干什么?方向FPGA+AI:Xilinx助力FPGA+AI时代

用FPGA来干什么?方向FPGA+AI:Xilinx助力FPGA+AI时代

FPGA在AI领域的优势:FPGA图像处理的前景如何?

三.HDL

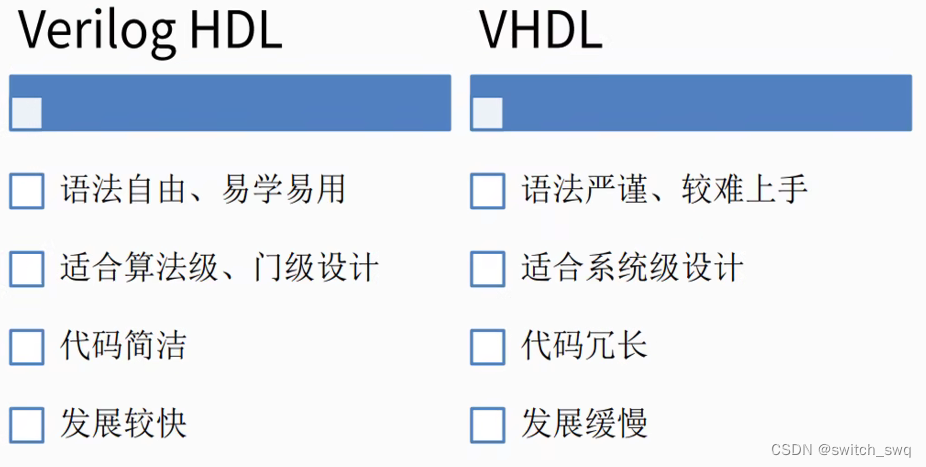

1.FPGA使用硬件描述语言,可参考:《Verilog》·第2章·硬件描述语言基础

可能会用到的知识:基于Verilog的图像处理实现

2.VHDL(VHSIC[Very-High-Speed Integrated Circuit] hardware Description Language)

2.VHDL(VHSIC[Very-High-Speed Integrated Circuit] hardware Description Language)

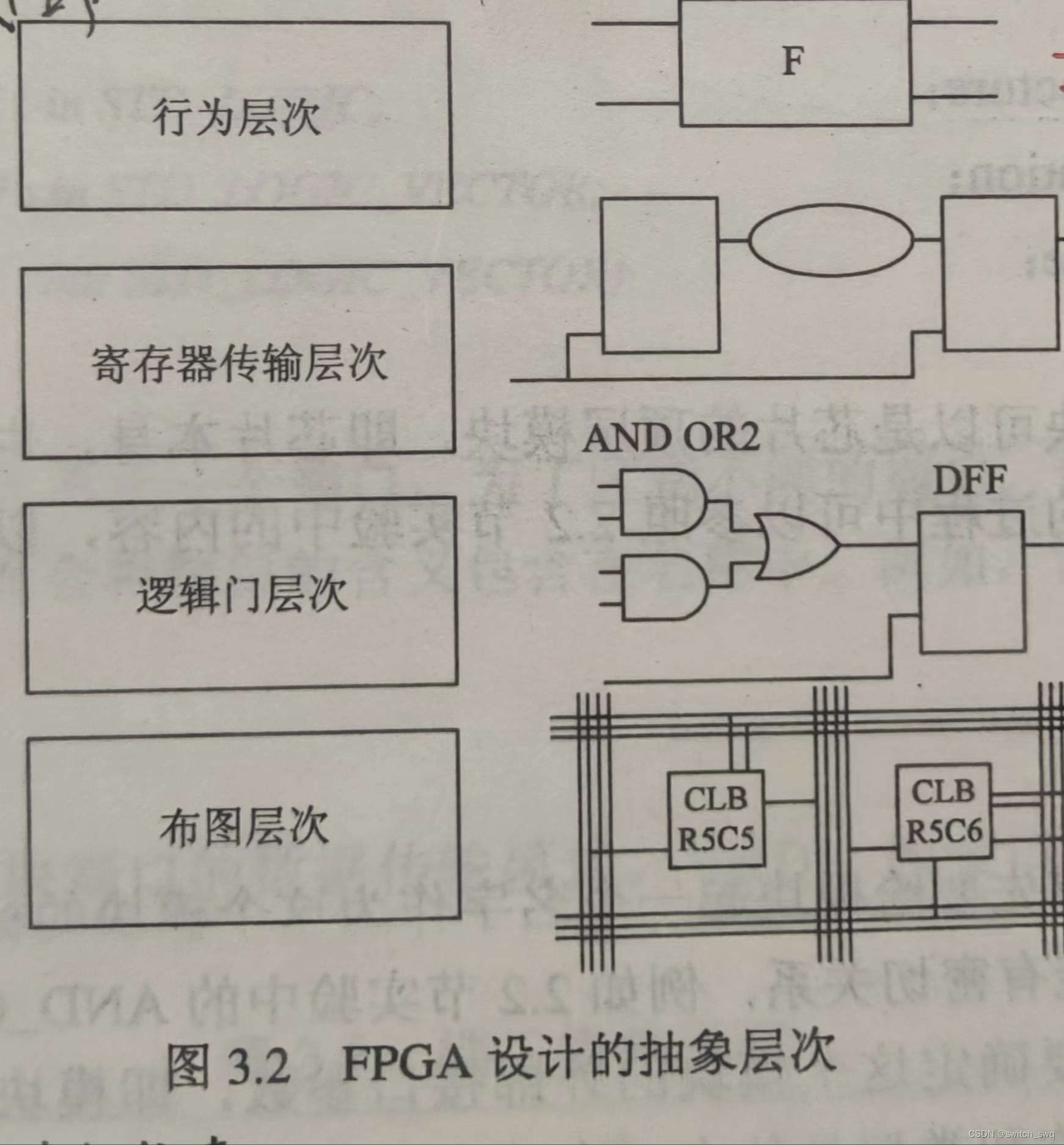

VHDL支持多层次抽象描述:行为层次(Behavioral)关注模块功能描述和仿真验证;寄存器传输层次(RTL,Register Transfer Level)关注模块的可综合电路的实现;逻辑门层次(Logic)考虑如何用门级电路实现给定功能;布图层次(Lay Out)考虑如何将电路适配到FPGA的资源中。

VHDL基本设计单元:实体(Entity)、构造体(Architecture)、配置(Configuration);包集合(Package);库(Library)

3.Verilog HDL

四.XILINX

xilinx公司的产品系列:FPGA 和 3D IC (xilinx.com)

文档搜索库:Homepage • AMD Adaptive Computing Documentation Portal (xilinx.com)

Artix-7官方文档:搜索结果 • AMD 自适应计算文档门户 (xilinx.com)

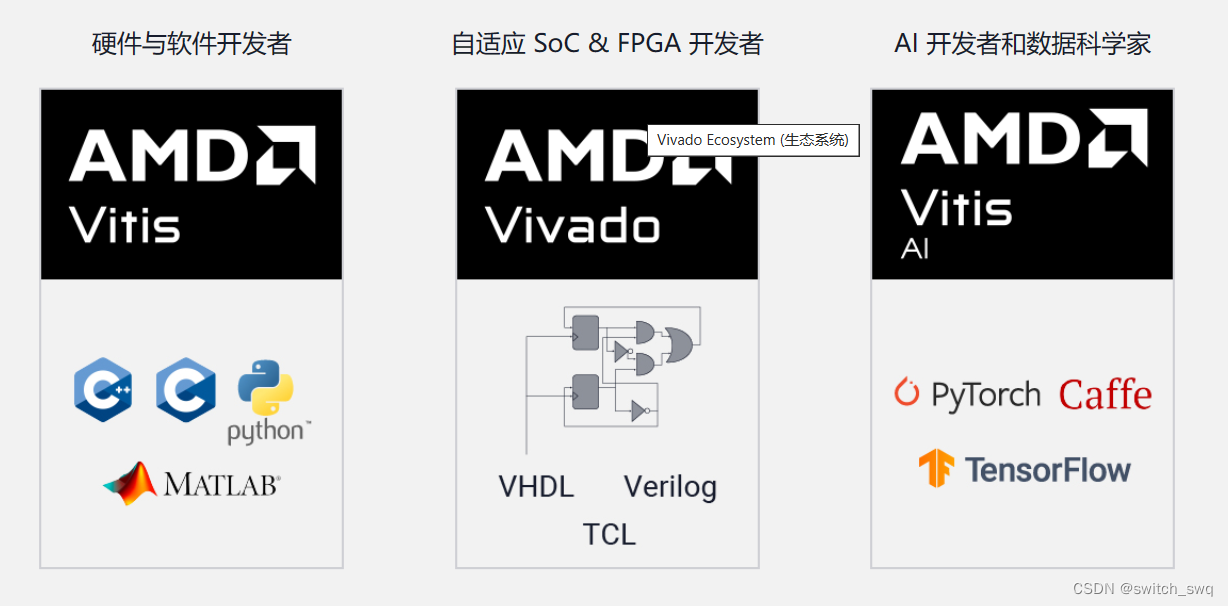

设计软件平台:

xilinx开发工具有哪些:Vitis AI 系列视频 QA&目录(待续)

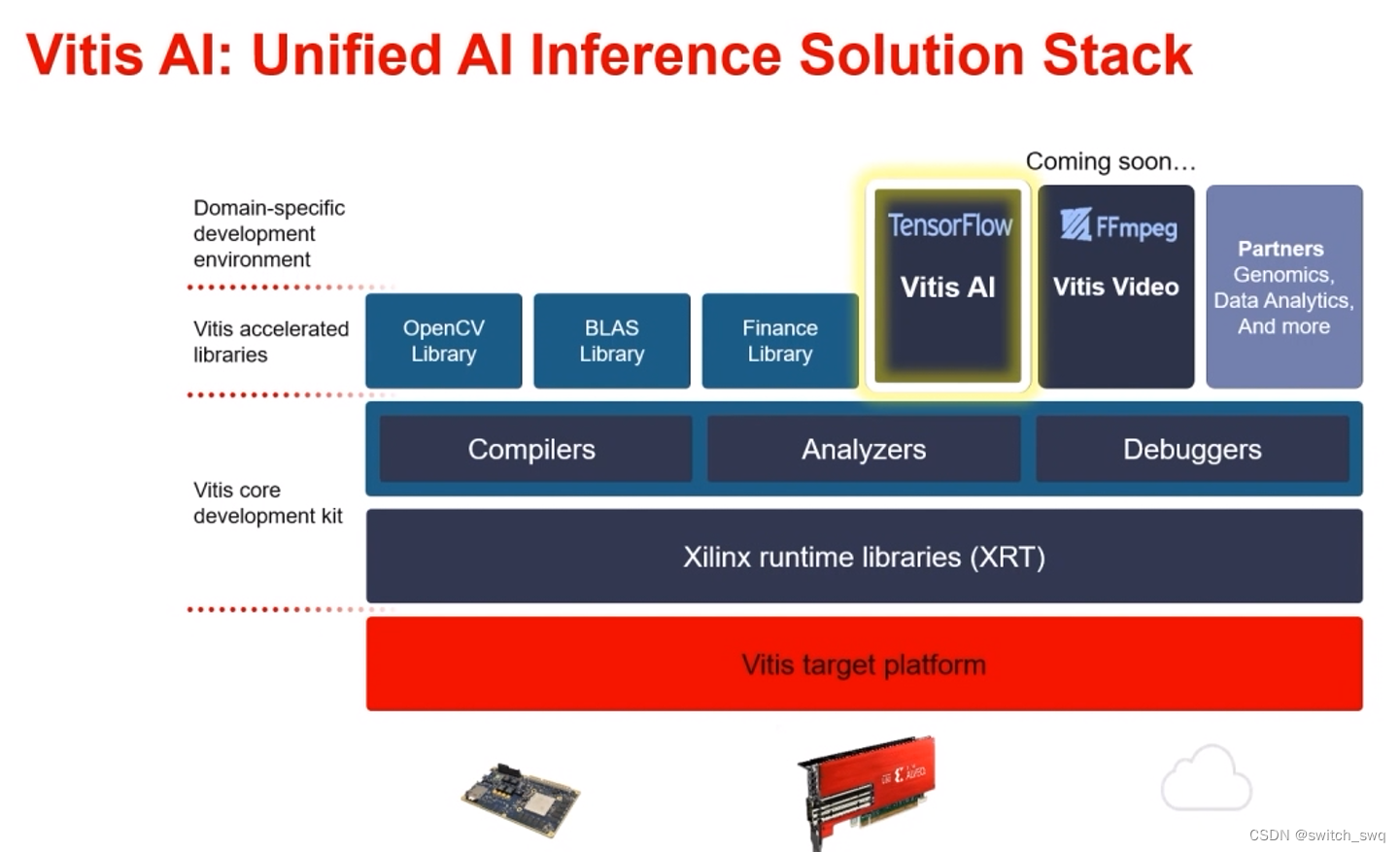

Vitis-AI:Vitis AI (xilinx.com)

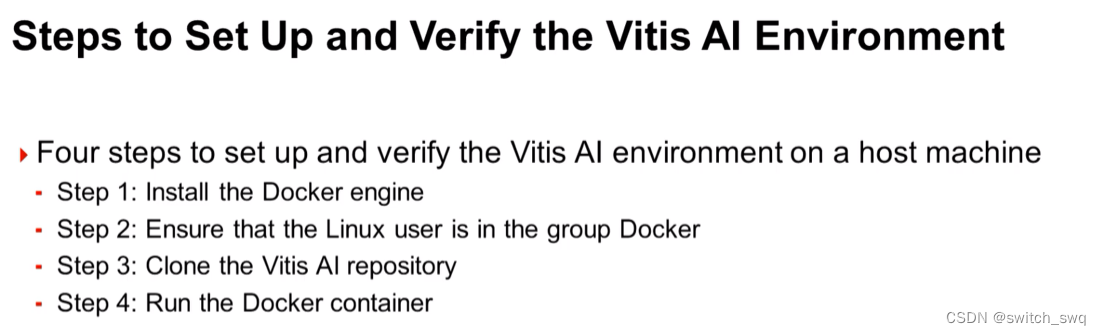

Vitis-AI官方支持:Vitis AI 快速上手 (xilinx.com)

视频:Vitis AI 全流程讲解 (xilinx.com)

Vitis下载:下载 (xilinx.com)

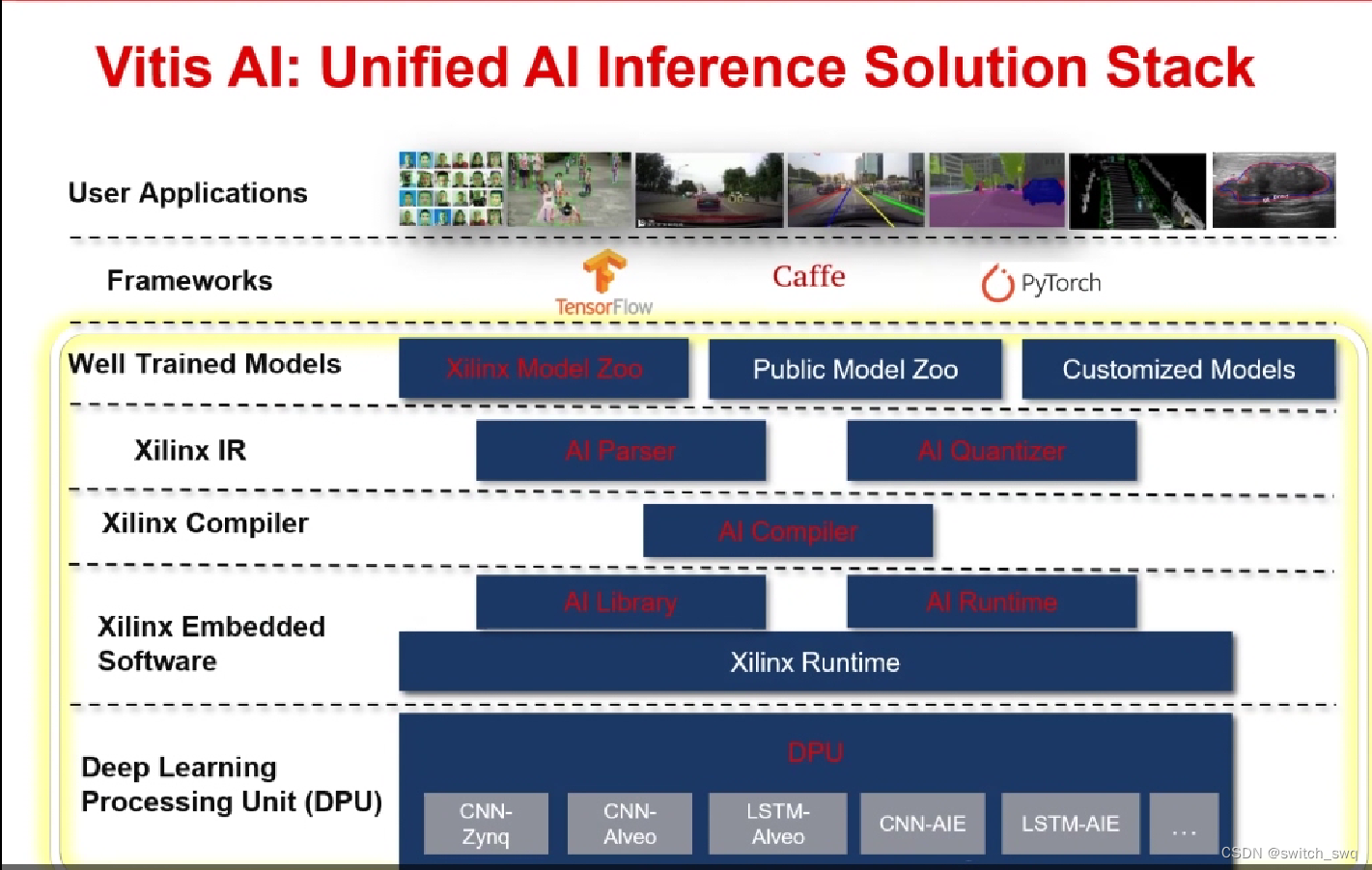

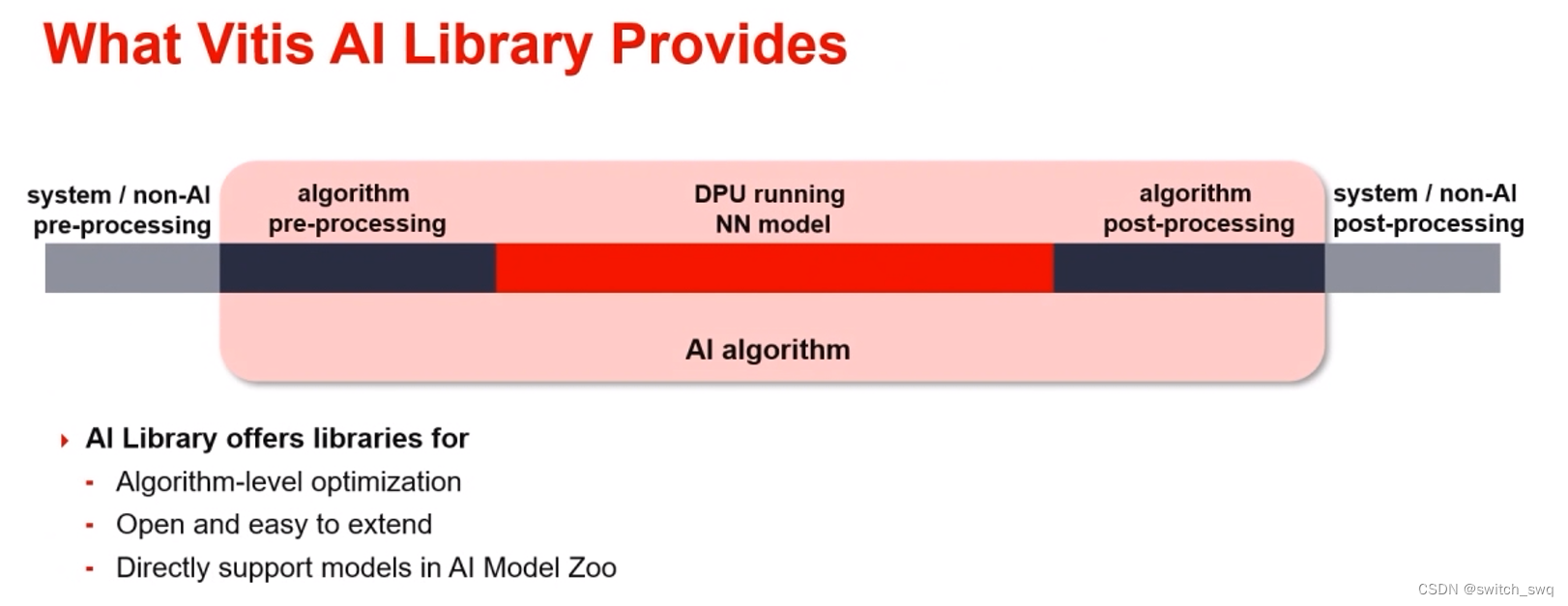

注:Vitis是为无FPGA设计经验的人设计的软件开发平台;Vitis-AI是面向算法开发者进行深度学习开发的高级加速库和设计工具;频繁出现的DPU:科普 | 什么是DPU?

Model Zoo:使用公共数据集训练良好的Caffe、pytorch、TensorFlow框架模型

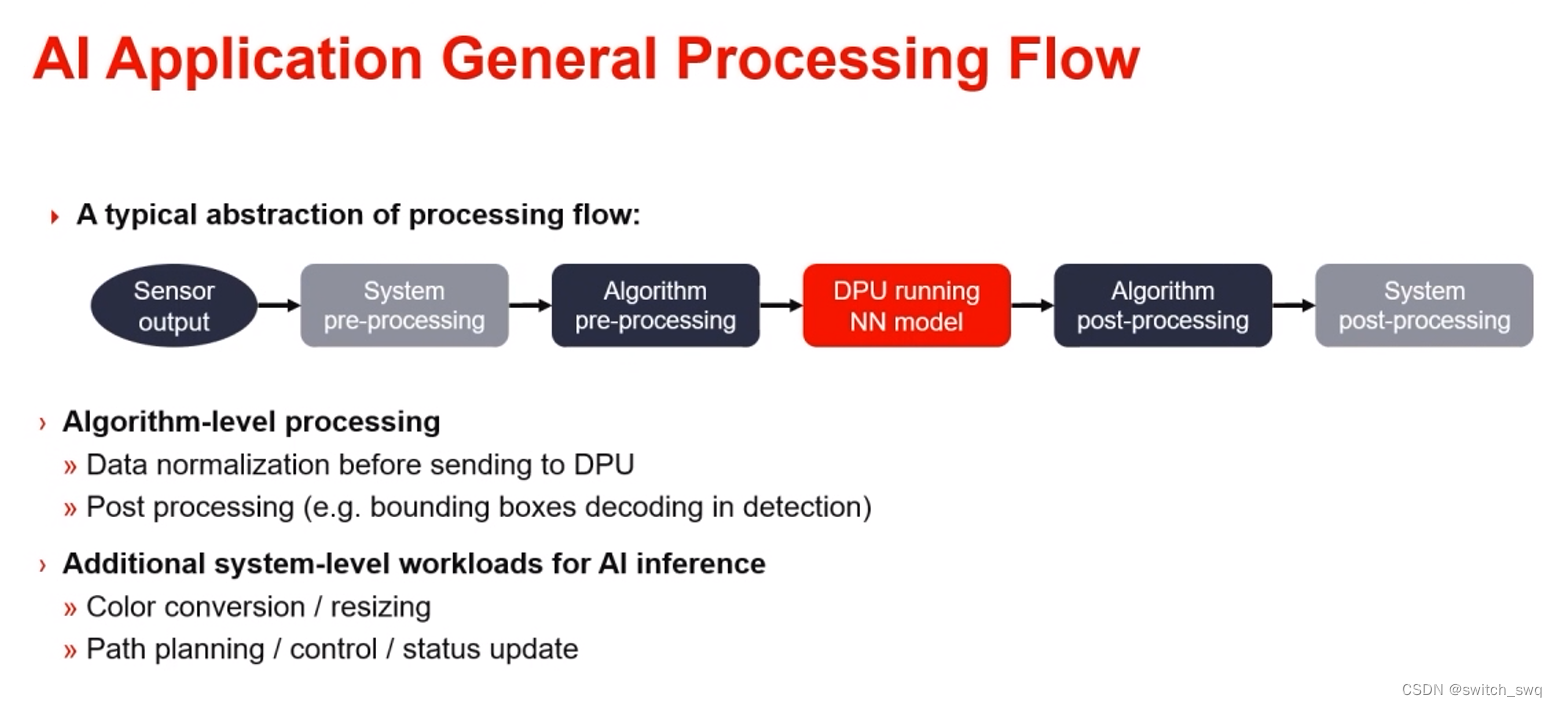

处理流程:

相关问题对话ChatGPT:https://chat.openai.com/share/2206fea6-39c7-4ec7-9567-d5d14513250f

xilinx社区:电子创新网赛灵思社区 | 电子创新网 (eetrend.com)

xilinx技术支持社区:主页 (xilinx.com)

五.学习资源

1.竞赛平台提供

FPGA创新大赛:培训视频_全国大学生fpga创新设计竞赛官网

龙芯杯:LoongsonEdu/nscscc-wiki (gitee.com)

英特尔杯:英特尔杯在线培训中心

2.野火资源

3.图书资源

《XILINX FPGA设计基础》《XILINX FPGA权威设计指南》《野火FPGAVerilog开发实战指南》

4.b站资源

推荐up主视频:

第0期 - 介绍与规划 -基于FPGA的数字信号处理系统开发笔记

ALINX Zynq MPSoC XILINX FPGA视频教程——Vitis HLS开发

5.正点原子资料

MPSoC开发板 — 正点原子资料下载中心 1.0.0 文档

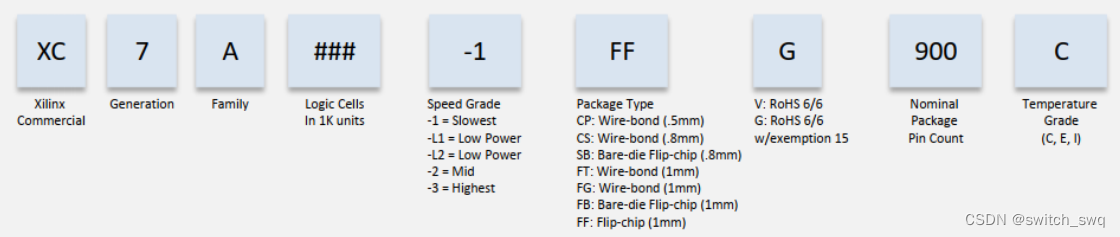

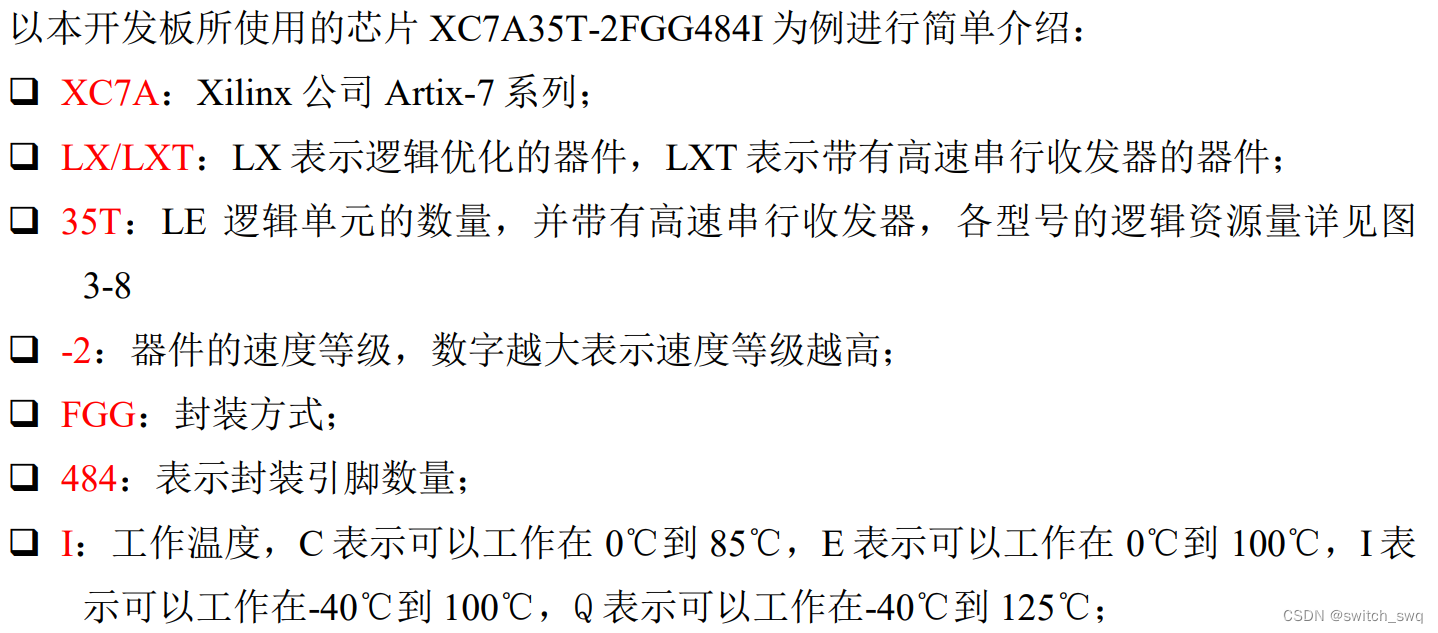

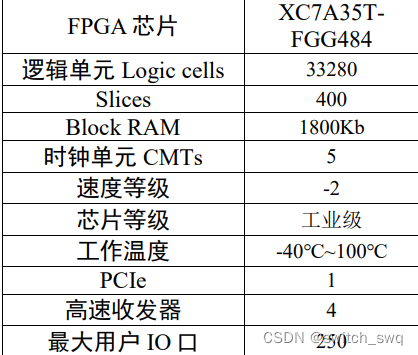

六.硬件命名规则

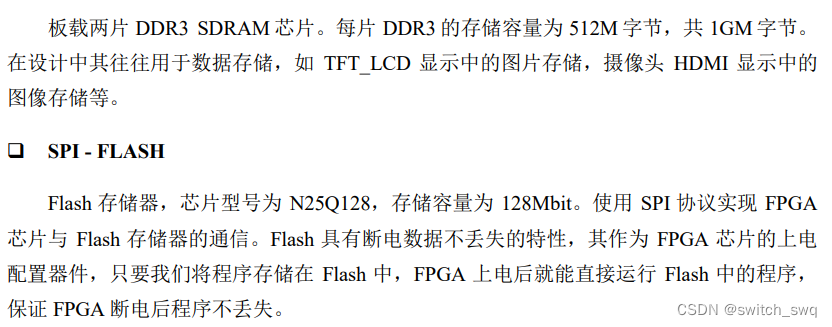

芯片资源

芯片资源

七.vivado使用介绍

参考《xilinx fpga权威设计指南》

1.首先书目介绍了新一代UltraScale结构,介绍了其CLB,包含LUT、触发器、查找表什么的,以此构成多路复用器、进位逻辑、存储等基本结构。(粗略浅看未看完)

2.vivado以前的版本是个IDE,现在出现了GUI,前后者的关系类似Windows的shell和图形界面的关系。而在之前所使用的是 XDC 语言,由标准约束语言 Tcl 演变而来,二者相似。vivado工程目录下的 .Journal 文件和 .Log 文件则可以记录Tcl命令和执行反馈,据此可在工程调试中导出.Journal文件制成Tcl命令脚本,实现快速自动化处理。XDC时钟约束 | 电子创新网赛灵思社区

3.接下来介绍vivado集成开发界面:

打开主界面三栏:快速开始(包含打开/创建工程、打开示例工程)、Task(IP核操作、硬件管理器【要连接板子,下载步骤时也要打开】、Tcl商店)、资料中心(文档、视频、注释向导)

任意打开一个工程,主界面左侧FlowNavigator(流程向导),包含:工程管理器(添加原文件、IP目录)、IP 集成器(设计用户IP核)、仿真、RTL分析(RTL ANALYSIS【RTL 闪退解决】,生成网表图、硬件引脚连接,生成.XDC文件)、综合(SYNTHESIS)、实现(IMPLEMENTATION)、编程和调试(生成比特流、打开硬件管理器)

可参考:Vivado的RTL分析(RTL analysis)、综合(synthesis)和实现(implementation)的区别?

源窗口Source,用于管理工程源文件,Hierarchy(层次)将工程按层次分组展示,Compile order可设置工程文件编译顺序,文件右键点击set as top可设置为顶层文件。

4.然后是高层次综合工具Vidado HLS

原理即将高级语言如c/c++转换成RTL级实现,还支持OpenCV函数

八.FPGA Arm-Cortex-M1软核配置

打开vivado IP manager,搜索 arm 显示可使用的 arm 核——Arm-Cortex-M1,若未安装可点击链接下载。Arm 官网下载 IP 核需要提前一周注册,提供免费使用的 IP 核有 M1 和 M3。

九.xilinx Zynq UltraScale+ MPSoC

Xilinx/PYNQ: Python Productivity for ZYNQ (github.com)

PYNQ - Python productivity for Zynq - Home

Zynq UltraScale+ MPSoC 是赛灵思推出的首款真正全可编程(All Programmable)异构多核处理 SoC 芯片。包含 PS(Processing System,处理器系统)和 PL(Programmable Logic,可编程逻辑)两部分。Zynq UltraScale+ MPSoC 整合了一个双核或四核 Cortex-A53 处理器、双核 Arm Cortex-R5F 实时处理器和一个传统的现场可编程门阵列(FPGA)逻辑部件,该器件的可编程逻辑部分基于 Xilinx 16nm FinFET+工艺的 UltraScale+系列 FPGA。这款芯片采用台积电公司 (TSMC) 新一代 16nm FinFET 工艺制程,它包含一个可扩展的 32 位或 64 位多处理器 CPU、用于实时处理图形和视频的专用硬化引擎、先进的高速外设,以及可编程逻辑,可用于汽车驾驶员辅助与安全、无线和有线通信、数据中心以及连接与控制等多种应用领域。

Zynq UltraScale+ MPSoC 系列产品分三种类型,分别是 CG 型器件、EG 型器件和 EV 型器件。其中 CG 型器件集成了由双核 Arm Cortex-A53 和双核 Arm Cortex-R5F 组成的 64 位处理系统;EG 型器件集成 了四核 Arm Cortex-A53 和双核 Arm Cortex-R5F,除此之外 EG 型器件还集成了 Arm Mali-400 MP2 (GPU)用来专门进行图像处理操作;而 EV 型器件在 EG 型器件的基础上再次增加了 H.264/H.265 视频编解码器(VCU)用来专门进行视频处理操作,它可以支持 60 帧每秒(fps)的速率同时进 行 4Kx2K 的编码和解码(约 6 亿像素/秒)或 15 帧每秒 8Kx4K 的编码解码。