热门标签

热门文章

- 1Oracle优化之B树索引_oracle b*索引与b+

- 2ECCV 2020 | 腾讯 AI Lab 16篇入选论文解读

- 3Windows安装mysql详细步骤(通俗易懂,简单上手)

- 4从github上克隆项目到本地或服务器命令_从githup上下载软件到服务器

- 5Unity实现轮播(简单方法)使用DoTween插件_unity触摸轮播

- 6RabbitMq应答模式、配置简介、常见阻塞场景_acknowledge-mode

- 7chatgpt赋能python:Python怎么模拟键盘输入:一份完整的教程

- 8Ubuntu16.04离线安装nginx遇到的坑_ubuntu离线安装libpcre3

- 9大数据之Hadoop3.x 运行环境搭建(免费下载Hadoop全套安装包、大数据简历模板和大数据面试真题)_hadoop环境搭建

- 10隐私计算技术实现数据要素安全可信流通_隐私计算在数据要素流通场景的应用

当前位置: article > 正文

USB PHY for FPGA & layout_usb3320 小梅哥

作者:Monodyee | 2024-05-23 18:35:51

赞

踩

usb3320 小梅哥

https://blog.csdn.net/qq_41904778/article/details/123967670

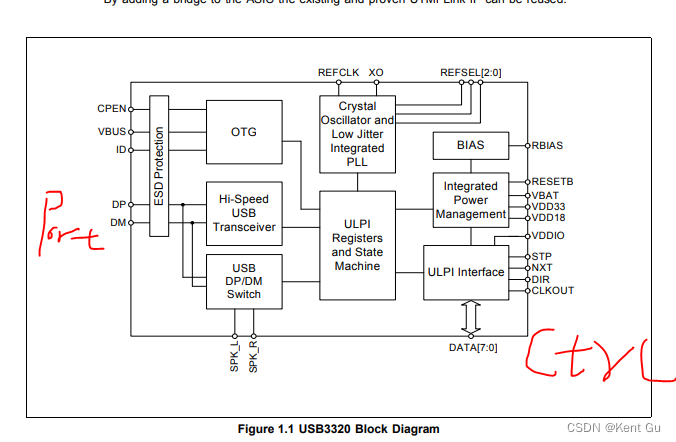

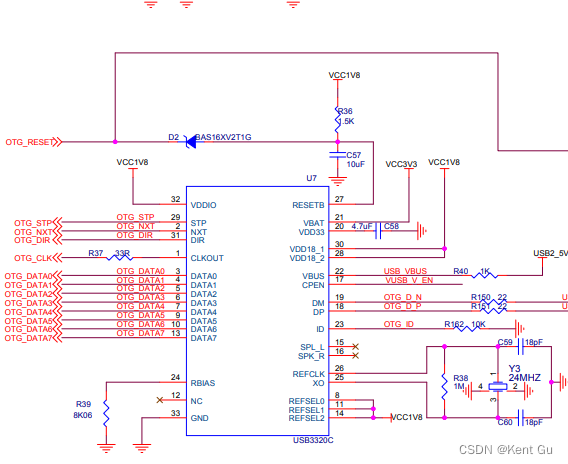

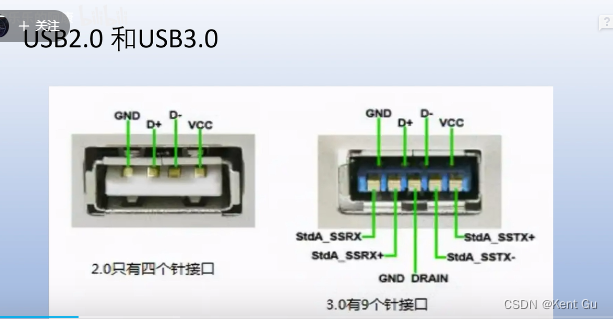

- ZYNQ7000内部没有USB PYH,我们通过USB 3320 PHY 芯片来连接FPGA 和外部的USB端口(DP+ & DP-)。

- USB 3320 PHY跟FPGA内部是t通过ULPI接口试下的,然后把数据转化为DP+、DP-模拟信号

- STM32内部带有了USB外设(PHY)

- 如网络芯片(PHY)就是把控制的RMI(其中的一种)转化为Tx_P/N, Rx_P/N.

5. USB PCB layout

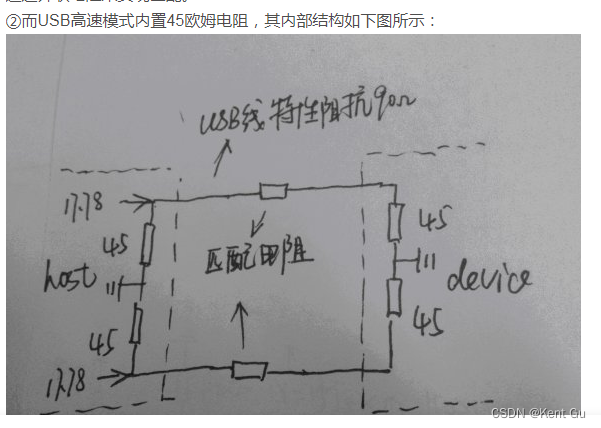

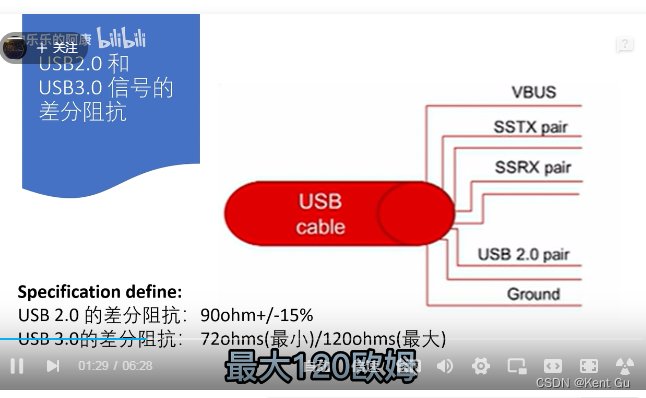

USB2.0 DP/DP-USB特征阻抗90Ω

总结:低速和全速时最好进行阻抗匹配 源端串联或终端并联90ohm ,高速时不需要。

匹配方式有:串联匹配、并联匹配、戴维南匹配等

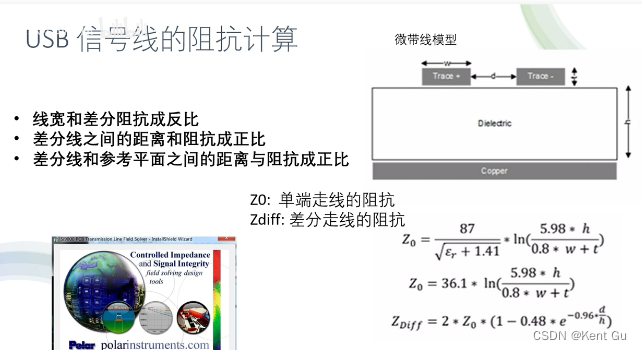

USB全速驱动器的输出阻抗一般比较小,若输出阻抗<特性阻抗则可以通过串联电阻来实现匹配,E330使用iMX258处理器,其全速Host的输出阻抗Rs厂家预计为10ohm,而USB线的差分特性阻抗为90ohm,所以要实现驱动器和USB线的阻抗匹配必须在USB D+和D-上串联电阻,串联电阻的要求为Rs 10Ω+R串=USB线特性阻抗90Ω;当阻抗>特性阻抗时则要通过并联电阻来实现匹配

高速匹配阻抗=0

在低速和全速模式下是电压驱动的,驱动电压为3.3V,但在高速模式下是电流驱动的,驱动电流为17.78mA

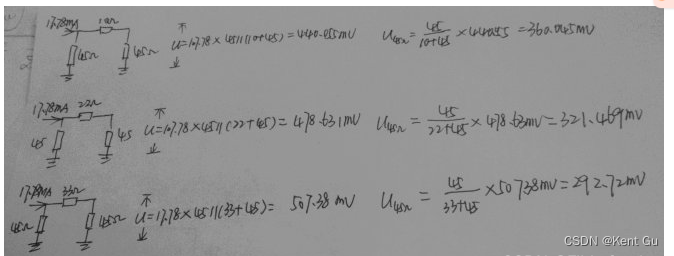

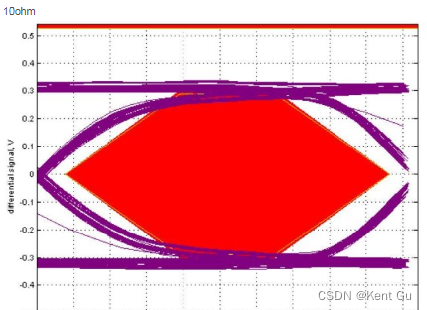

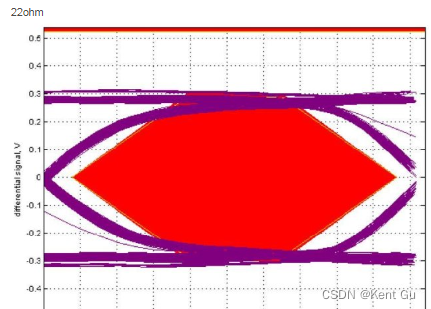

Host和device的D+和D-都有45ohm的电阻端接到地,所以每根线的并联电阻为22.5ohm,17.78x22.5=400mV,所以高速模式下的差分幅度为800mV (这时匹配电阻为0),但是匹配电阻选择10ohm,22ohm和33ohm时我们可以计算出单端信号的幅度如下图:

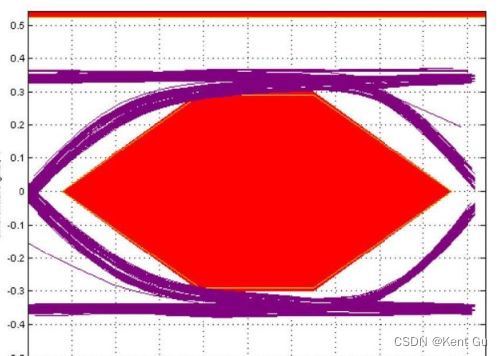

高速模式下加入匹配电阻会使信号幅度下降,使信号质量变差,加入匹配电阻后的眼图分别如下(紫色线与红色区域交叉越多,说明分界越明显,数据越容易出错

)

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Monodyee/article/detail/614006

推荐阅读

相关标签