热门标签

热门文章

- 1Android如何防止apk程序被反编译_apk防反编译

- 2大模型时代下的决策范式转变_大模型的统计分析和辅助决策

- 3union all和union的区别以及怎么使用_union all和union的区别用法

- 4oracle的SQL语句中的(+)是干什么用的?

- 5Qt 3D:线框 QML 示例_qml qt3d 画线

- 6SpringBoot升级3.2报错Invalid value type for attribute ‘factoryBeanObjectType‘: java.lang.String_invalid value type for attribute 'factorybeanobjec

- 7七年级上册英语第三单元单词课文翻译_answer是七年级上册第几单元学的

- 8网络编程1 - socket基本函数_socket函数pf

- 9大学生如何选择人生第一份工作

- 10安装g++,在centos上执行yum -y install gcc gcc-c++ libstdc++-devel

当前位置: article > 正文

FPGA - 时钟Buffer的探究_模拟ic中buffer

作者:Gausst松鼠会 | 2024-05-27 01:16:44

赞

踩

模拟ic中buffer

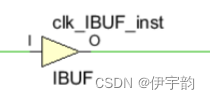

1、IBUF : FPGA上所有的输入信号必须进过IBUF,vivado会自动给所有输入信号分配IBUF

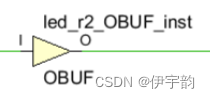

OBUF:FPGA上所有的输入信号必须进过IBUF,vivado会自动给所有输入信号分配OBUF

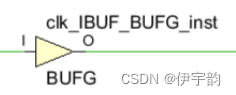

BUFG:专用时钟的资源,目的是减少时钟抖动、增强时钟的驱动能力,vivado不会给信号自动分配BUFG

在vivado如何调用呢?

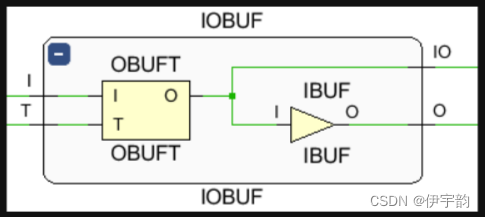

如下图

IBUFG: IBUFG = IBUF + BUFG;

BUFH:即为水平时钟缓冲器,它相当于一个功能受限的BUFG很少使用。优点就是功耗低

BUFGCE:CE为时钟使能信号,相当于在BUFG上面添加了使能在CE有效的时候,才输出时钟BUFHCE:CE为时钟使能信号,相当于在BUFH上面添加了使能在CE有效的时候,才输出时钟

2、一般外部晶振的时钟走专用时钟管脚,进入FPGA, FPGA内部将这个时钟送入PLL,可以分频得到更多不同频率的时钟

3、一些外设提供给FPGA的时钟,比如摄像头提供给FPGA的像素时钟pix_clk,在设计时候,很大可能走的不是专用时钟管脚。如果走的不是专用时钟管脚,建议这个时钟过一个BUFG。

4,当时钟级联时,前一时钟已经经过了一个BUFG,那么后一时钟就选择 NO Buffer。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Gausst松鼠会/article/detail/629213

推荐阅读

相关标签