FPGA DDR3调试

Spartan6 FPGA芯片中集成了MCB硬核,它可以支持到DDR3。在Xilinx的开发工具Xilinx ISE中提供了MIG IP核,设计者可以用它来直接生成 DDR3 控制器设计模块,并通过 MIG 的 GUI 图形界面完成相关配置。

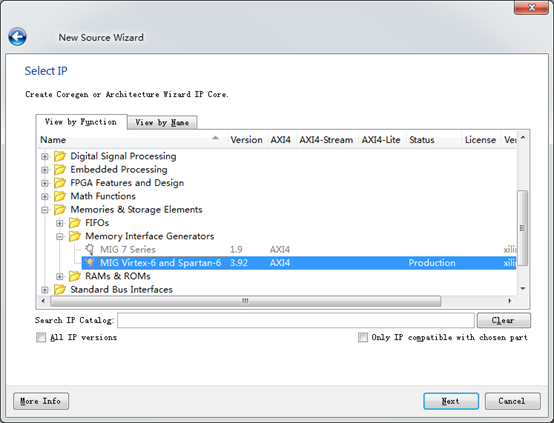

首先,建立ISE工程,并添加MIG IP核,

接下来进行MIG IP核配置,这里列出主要的部分,

这里选择DDR的类型,并选择使用Spartan6的哪一个bank,一般选择左边的bank,

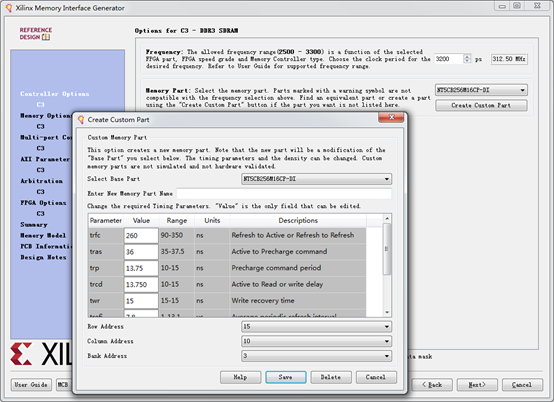

这里设置DDR3的时钟频率以及DDR3的设备型号,Xilinx列举了部分DDR3型号,如果没有,则需要点击“create custom part”自定义型号,这里注意在自定义型号的时候最好选择一个模板与自己的DDR3型号数据位宽一样的,因为自定义选项中无法修改数据位宽(当然也可以在生成的代码中修改位宽)ÿ