- 1练手好福利!20个Python实战项目含源代码!_python小项目源码

- 2AI 人工智能写情诗、藏头诗模型训练与AIGC体验设计_藏头诗ai

- 3【打印功能】js简单实现表格样式的数据打印,按样式打印出来_如何根据用户自定义标签格式例如用excl,并通过js打印

- 4kafka(二)分区、副本与副本间的数据同步_kafka分区副本数据同步

- 5PyTorch深度学习项目实战100例数据集_pytorch cookbook: 100+ solutions across rnns, cnns

- 6让AI听话的一种办法(Stable Diffusion进阶篇:SVD 3)_comfyui-videohelpersuite

- 7Hello Blog! Hexo+Github零成本搭建自己的个人博客网站_h-blog

- 8《系统集成项目管理工程师》必背100题_系统集成项目管理工程师100道题哪里找

- 9基于Milvus向量数据库实现检索增强生成(RAG)_milvus实现rag

- 102024华为OD机考机试 真题目录(C卷 + D卷 + B卷 + A卷) + 考点说明_华为od c d

不出来信号 quartus_FPGA毕设系列 | 任意信号发生器

赞

踩

信号发生器在电子实验中作为信号源,通常用得多的是正弦波、三角波、方波以及用作触发信号的脉冲波。在这里给大家分享下如何通过FPGA实现任意信号发生器,希望对相关课题的小伙伴有所帮助。

一、设计任务

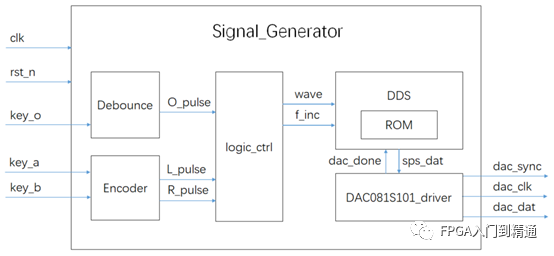

通过FPGA驱动旋转编码器得到操作信息,通过逻辑控制波形和频率寄存器,设计DDS模块根据波形和频率寄存器控制波形数据的输出,波形数据通过串行DAC驱动模块传送到底板的DAC芯片进行转换,得到波形信号输出。

二、设计准备

硬件:小脚丫FPGA核心板、DAC芯片(DAC081S101)、旋转编码器

软件:Quartus Prime/Lattice Diamond

三、设计结构

四、设计原理

1.DAC模块

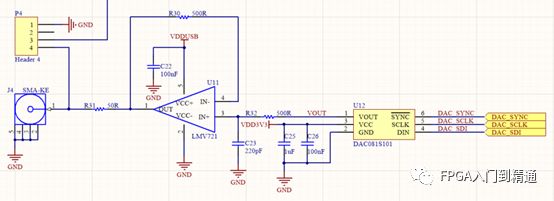

串行DAC(以DAC081S101为例)与数字电路接口为三根线(sync,clk,din),兼容三线SPI总线,sync为帧同步管脚,clk为芯片时钟管脚,din为芯片数据管脚,当DAC帧同步信号拉低后每个clk周期从din发送1bit的数据,但是根据DAC081S101的时序,需要16个clk完成一次DA转换,所以clk频率至少等于采样率的16倍。

DAC模块电路,其电路图如下:FPGA直接连接DAC081S101芯片的控制端,ADC有6个管脚,2脚VCC为VCC和Vref功能复用,即VCC =Vref。DAC后端是运放电路LMV721,运放模块为电压跟随电路,再往后端射频端子输出。

五、设计驱动

1. DAC模块驱动

根据DAC081S101的芯片手册以及通信时序,我们用Verilog设计一个计数器,当计数器值不同时完成不同操作,实现一次DAC转换,程序实现如下:

reg[7:0] cnt; always@(posedge clk ornegedge rst_n) if(!rst_n) cnt <=1'b0; elseif(cnt >=8'd34) cnt <=1'b0; else cnt <= cnt +1'b1; reg[7:0] data; always@(posedge clk ornegedge rst_n) if(!rst_n)begin dac_sync <= HIGH; dac_clk <= LOW; dac_dat <= LOW; endelsecase(cnt) 8'd0:begin dac_sync <= HIGH; dac_clk <= LOW; data <= dac_data;end 8'd1,8'd3,8'd5,8'd7,8'd9,8'd11,8'd13,8'd15, 8'd17,8'd19,8'd21,8'd23,8'd25,8'd27,8'd29,8'd31, 8'd33:begin dac_sync <= LOW; dac_clk <= LOW;end 8'd2:begin dac_sync <= LOW; dac_clk <= HIGH; dac_dat <= LOW;end//15 8'd4:begin dac_sync <= LOW; dac_clk <= HIGH; dac_dat <= LOW;end//14 8'd6:begin dac_sync <= LOW; dac_clk <= HIGH; dac_dat |