- 1植物大战僵尸杂交版2.088修改器+防闪退+高清补帧工具_植物大战僵尸2.088

- 2在 C# 中使用 MySQL 数据库进行连接和数据操作,连接 MySQL 数据库并进行添加、删除、替换、查找以及筛选。_怎么替换数据库的链接内容

- 3南开大学软件学院2023大三上期末考试各科回忆卷_南开大学软件学院研究生软件工程期末

- 4蓝桥杯【第14届国赛】Python B组_十四届蓝桥杯国赛pythonb组 偶串

- 5Linux安装Mysql(超详细,亲测)

- 6SparkSQL的3种Join实现_sparksql的三种join实现

- 7java安全——jsp一句话木马_java js一句话

- 8最全史上MySQL安装配置教程最细,一步一图解_mysql -uroot -p,华为远程视频面试经历_mysql安装教程

- 9字符串操作(strlen/strcpy/strcat/strcmp/strncpy/strncat/strncmp/strstr/strtok/strerror)_strtok,strcat

- 10安装Ubuntu18.04_ubuntu设置subnet

Quartus+Modelsim联合仿真_quartusii使用modelsim仿真联合的多个v文件

赞

踩

软件版本:Quartus II 18.1 Standard Edition + ModelSim SE-64 10.1

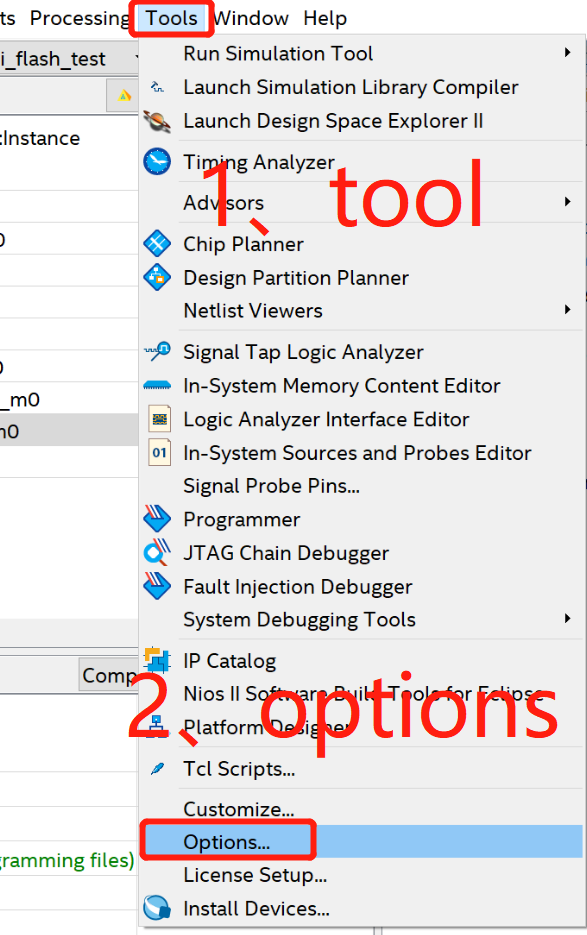

1、设置Quartus中各仿真软件exe的安装路径

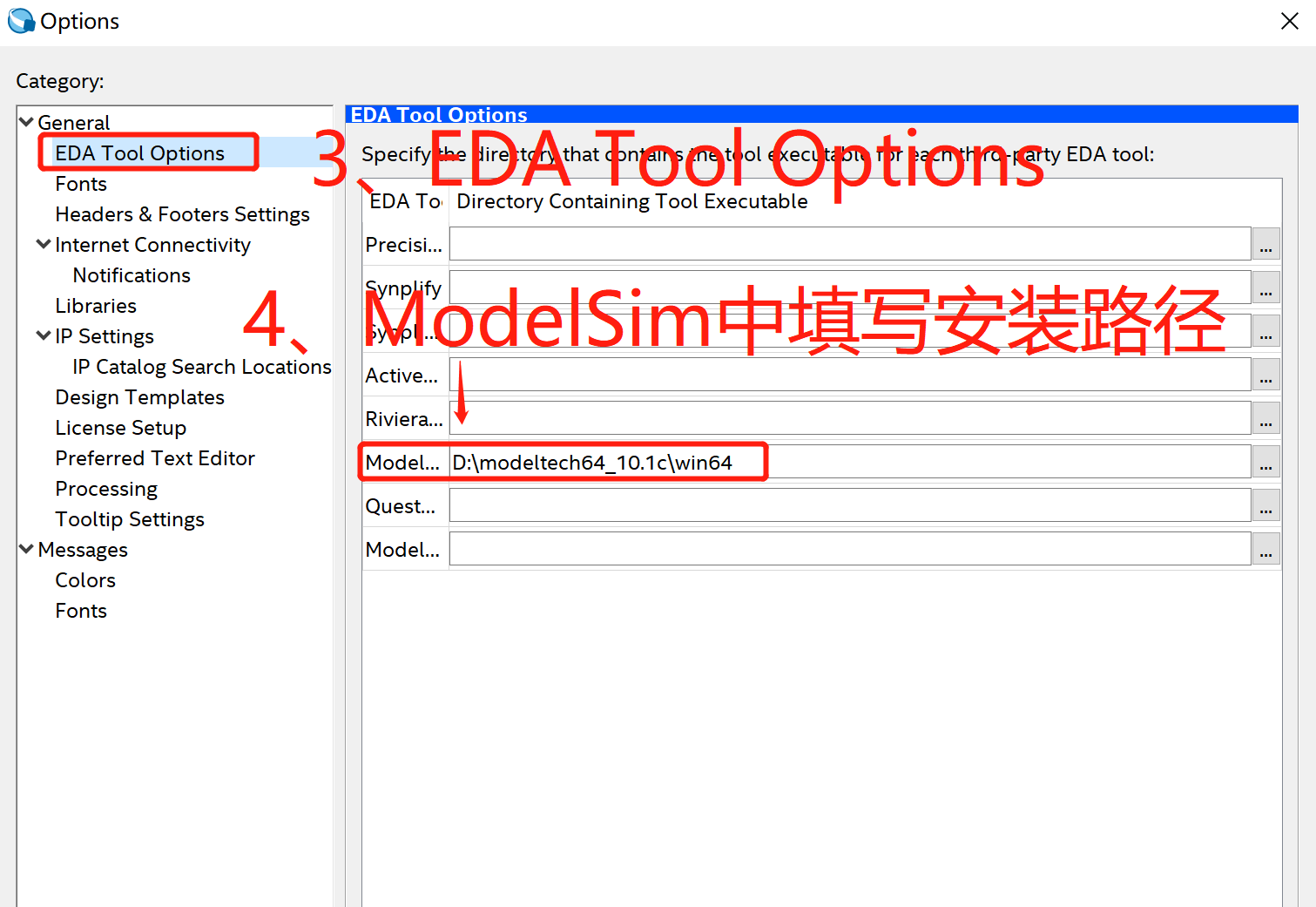

选择tool—》options—》General—》EDA Tool Options,在ModelSim一栏填写Modelsim的可执行程序的路径,典型路径为:安装路径\win64,例如:

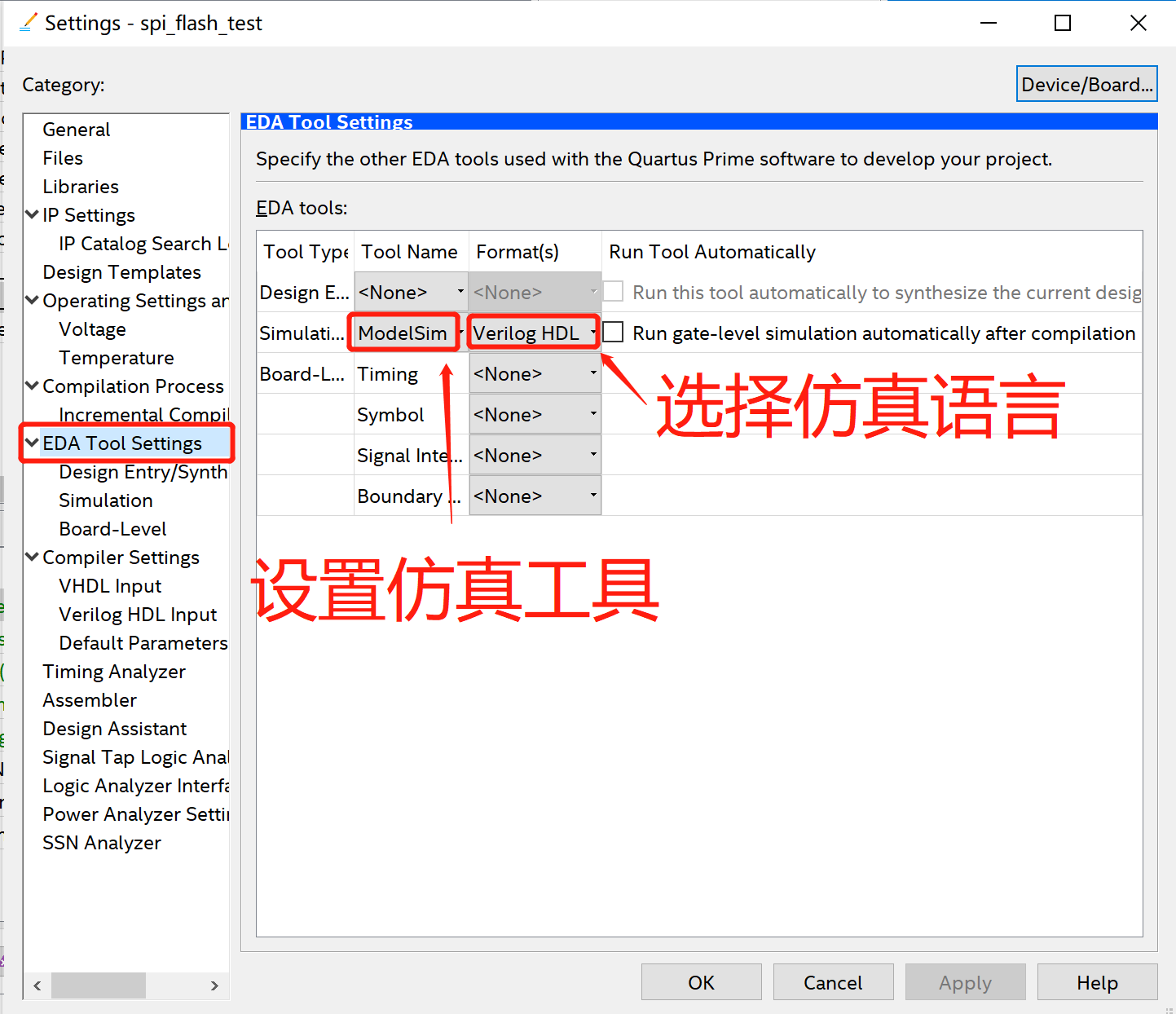

2、设置工程将要使用的仿真工具与编程语言(必须要在Start Testbench Template Writer前设置完成,否则不能自动生成.vt测试文件 )

点击Assigments —》Settings—》EDA Tool Settings-Simulation,填写仿真工具Modelsim与仿真语言。

3、创建测试文件

有两种方式,分别是Quartus II自动生成测试文件(.vt)与自己手动创建测试文件(.vt或者.v)文件;

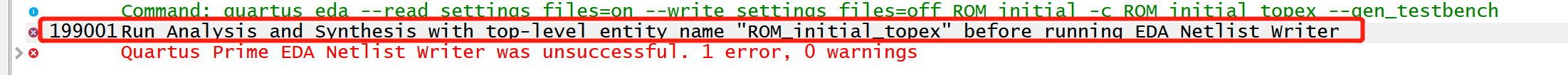

方式一:Quartus II自动生成测试文件(.VT文件,注意要先analysis&synthesis源文件后才能创建测试文件):

在自动生成测试文件之前,要先" Analysis and Synthesis (分析与综合) "源文件后才能创建测试文件;不能是” Analysis and Elaboration(分析与阐释) “,否则会报错提示进行" Analysis and Synthesis (分析与综合) ":

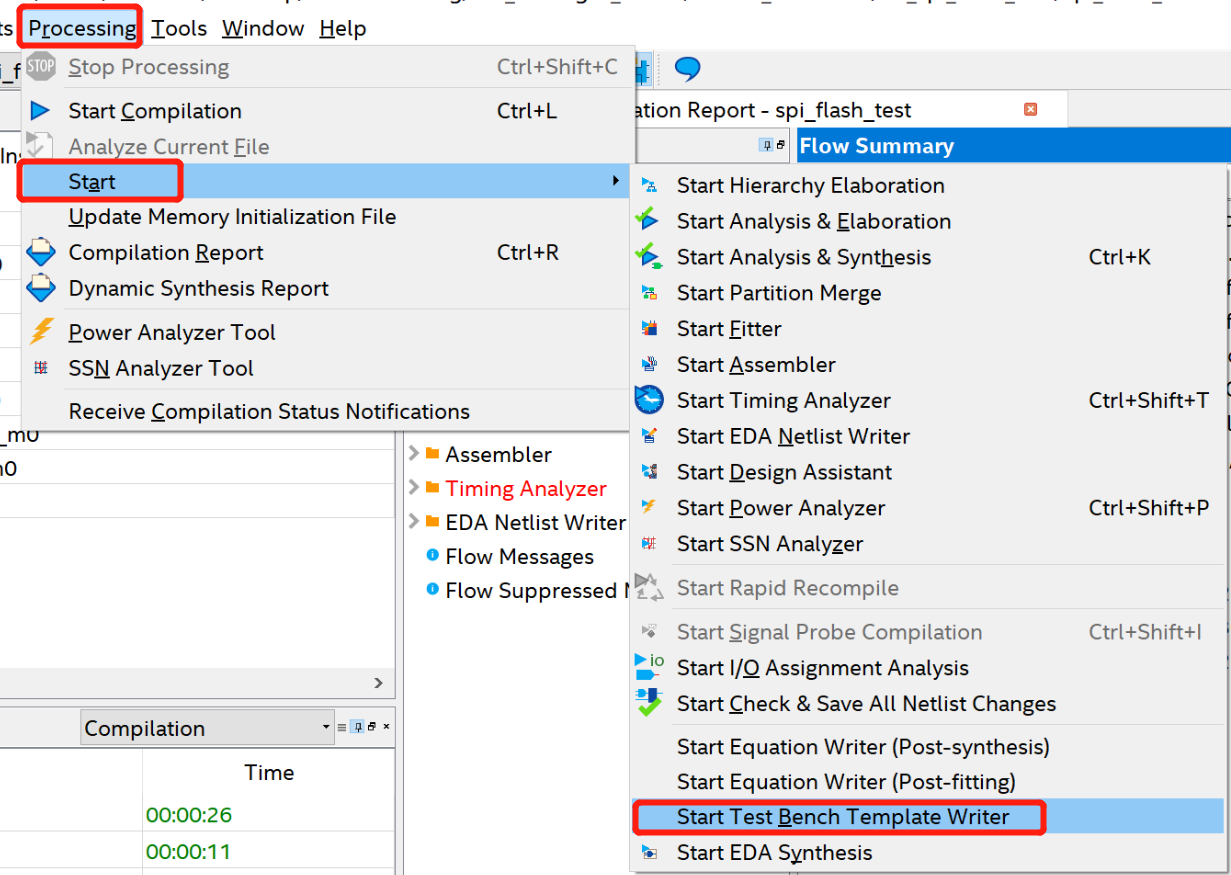

点击Processing—》Start—》Start Testbench Template Writer,自动生成vt文件

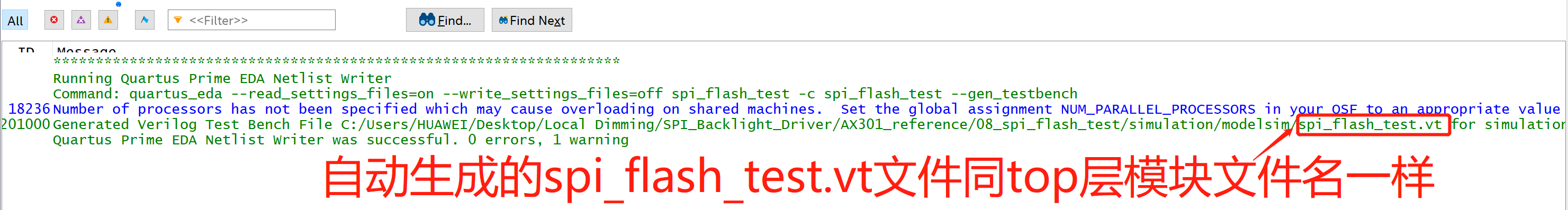

自动生成的测试文件名同top文件名相同,典型路径为:[project_diretory]/simulation/modelsim/xxx.vt;

方式二:自己手动创建测试文件(.vt或者.v)文件;

在工程文件夹下创建一个sim文件夹,然后创建一个txt文本文件,接着修改文件文件名并修改后缀名为.v或者.vt即可

建议使用.v的测试文件,用notepad++打开后有多种颜色显示,notepad++不支持.vt测试文件的多种颜色显示。

4、编辑测试文件,生成激励

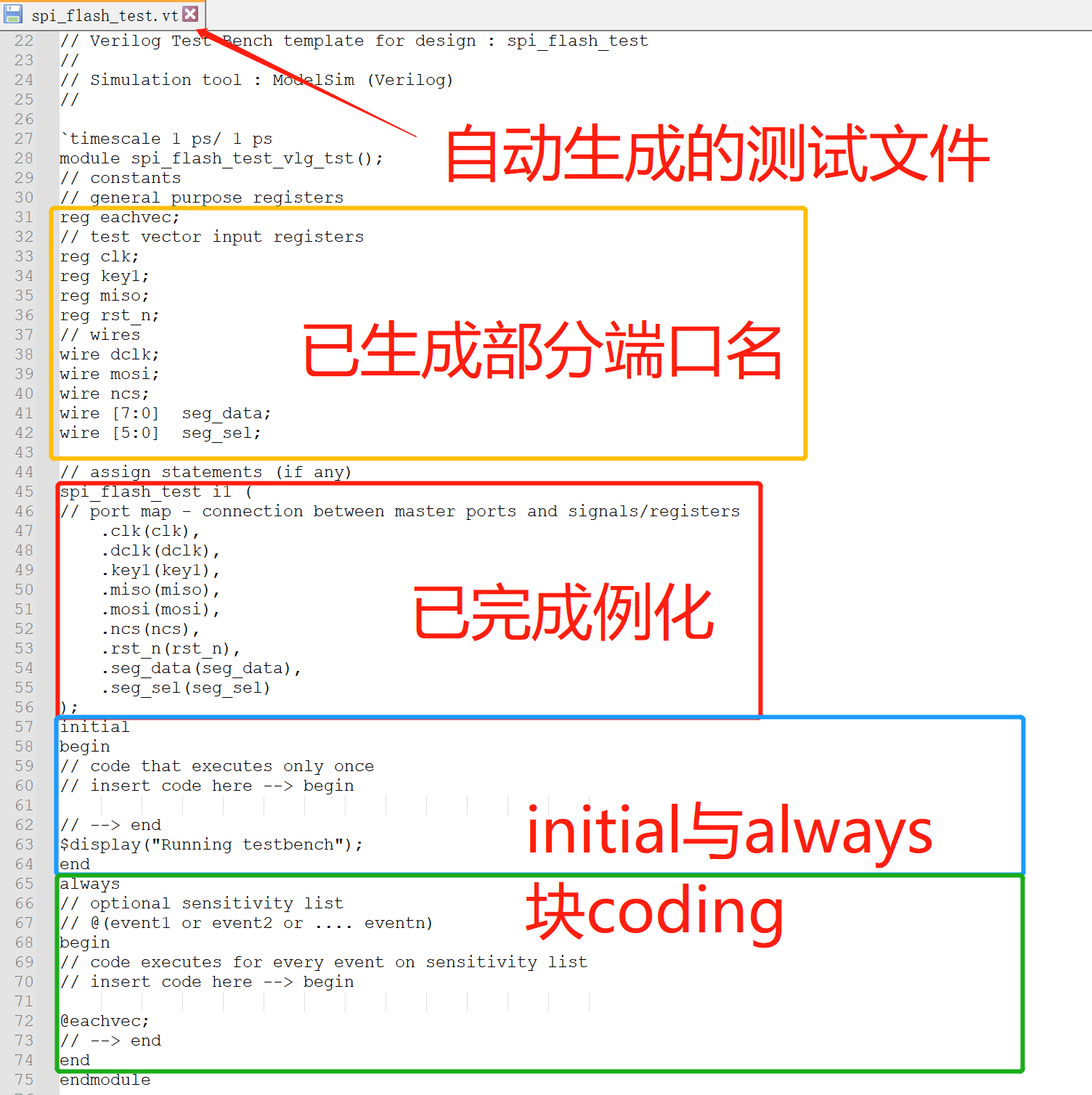

自动生成的xxx.vt文件完成了端口定义和实例化,但是需要设置激励波形,即编写initial语句与always调用块;

具体方法通过文本编辑器来产生激励波形。

ps:自己手动生成的.v测试文件需要自己手动编辑源代码。

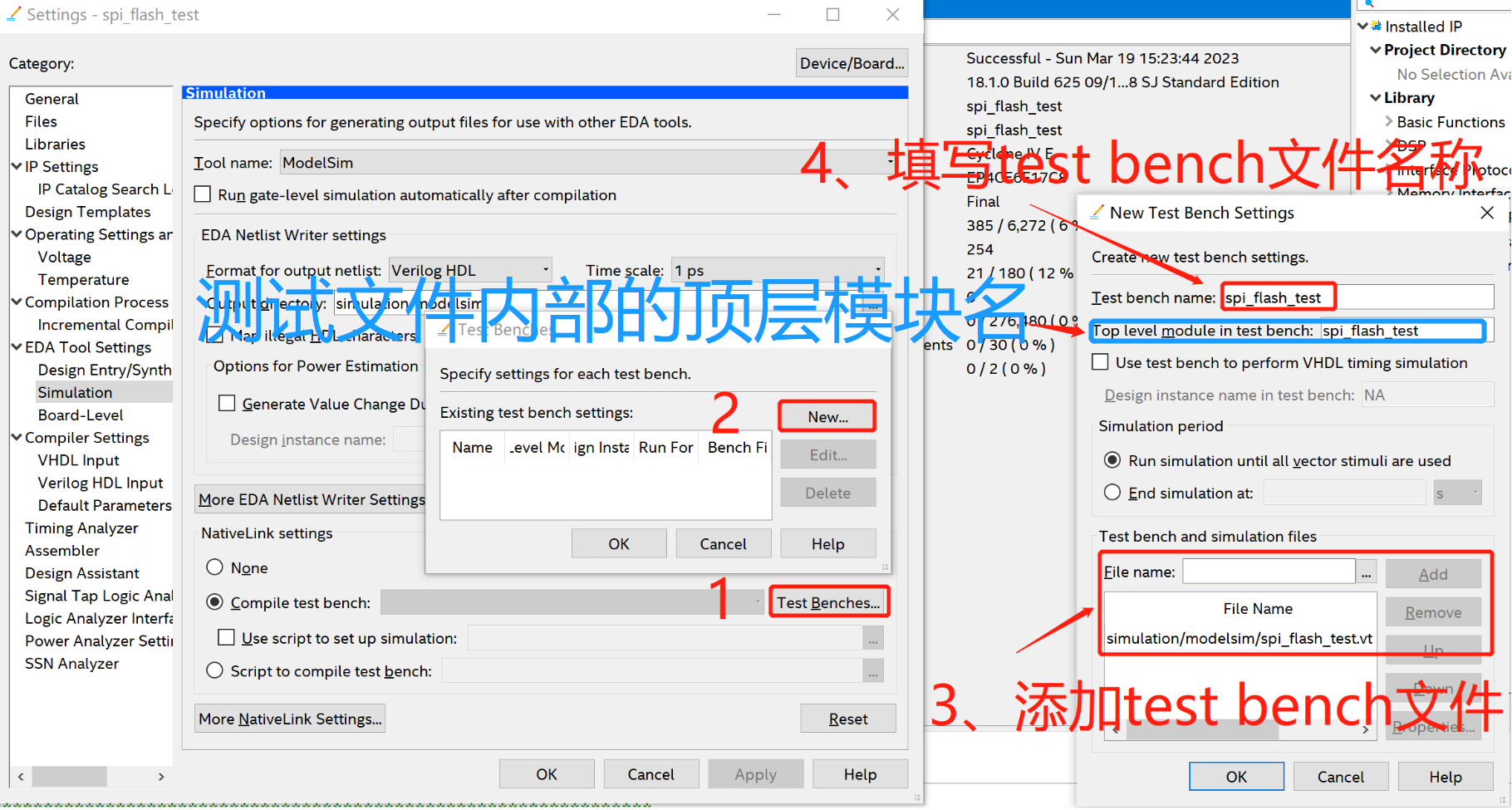

5、添加测试文件并设置仿真时长

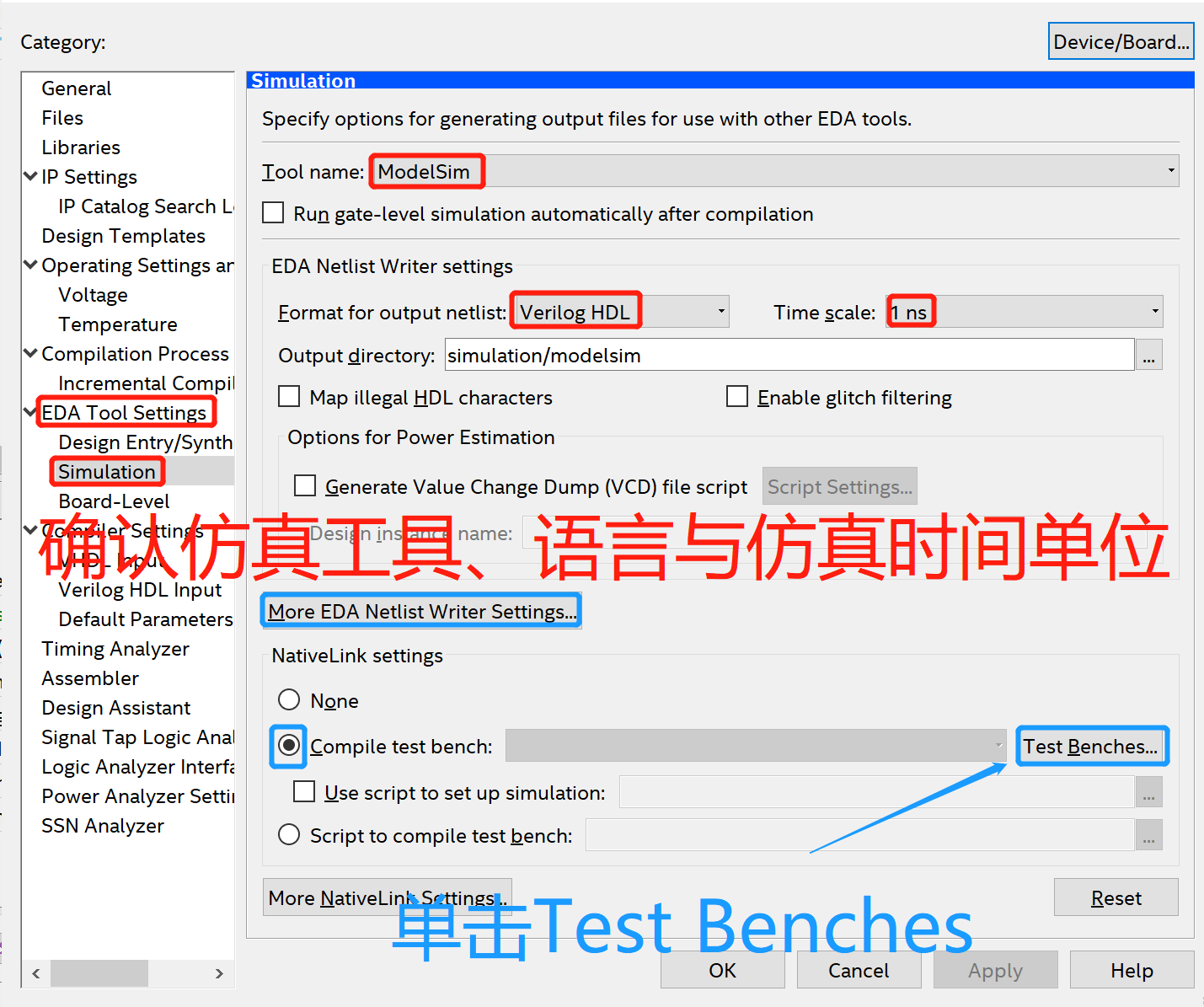

点击Assigments —》Settings—》EDA Tool Settings-Simulation—》Simulation,确认仿真工具(Modelsim)、仿真语言(Verilog)与仿真时间单位(1ps或者1ns,默认1ps)

Note:这里设置的仿真时间单位会在前面自动生成的测试文件中体现为:`timescale 上图选中的仿真时间单位/1ps(默认1ps的仿真时间精度)

添加test bench文件,其中top level module in test bench(测试文件内部的顶层模块名,注意不是测试文件内部调用的其它模块的名称【特别针对只调用单个模块的测试文件,容易错填】)的文件名需要打开vt文件查看确认后填写。

ps:.v测试文件的添加同.vt

番外:End simulation at,即是仿真停止时间(最好提前设置好,仿真时即可不用管,不设置会一直不停仿真直到你手动暂停仿真为止)。

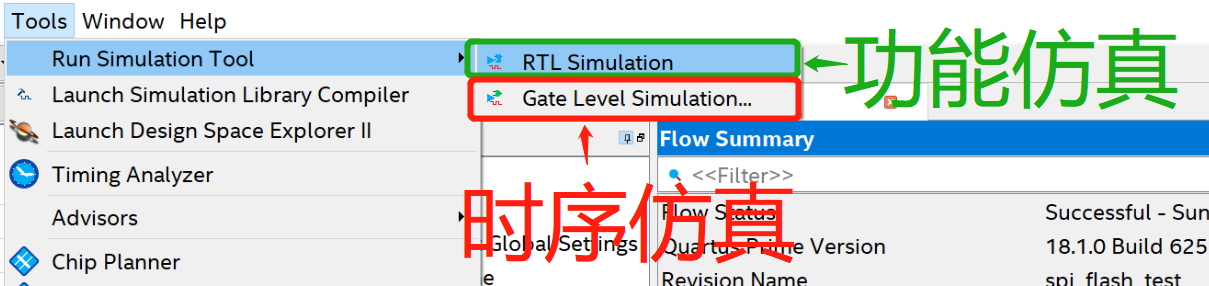

6、启动仿真

功能仿真:Tools—》Run Simulation Tool—》RTL Simulation

时序仿真:Tools—》Run Simulation—》Gate Level Simulation

自动弹出Modelsim页面并进行仿真,自动展示仿真波形

参考链接: