热门标签

热门文章

- 1华为ensp VRRP详解_ensp vrrp

- 2JAVA匿名内部类_java 匿名内部类return

- 3python爬虫实战(1)--爬取新闻数据_爬虫爬取辽宁日报

- 4【小白入门】2021 计算机视觉开源项目整理_计算机视觉 开元

- 5如何在GPU上高效加速深度学习模型?了解并行计算和分布式计算的基本知识_深度学习 gpu加速

- 6NandFlash存储管理技术(磨损均衡、坏块管理、位翻转)_mt29f4g08 ftl

- 7一文带你玩转大模型开发,Transformer工作原理_大模型transformer工作原理

- 8IOSOpenDev~直接安装Deb软件的方法_openeuler安装deb软件命令

- 910 00面试,10 04就出来了 ,问的实在是太(2)

- 10nosql:粗谈redis_redis 中的port、密码和host-name是怎么获取的

当前位置: article > 正文

Xilinx IDELAYCTRL

作者:IT小白 | 2024-05-23 21:05:57

赞

踩

idelayctrl

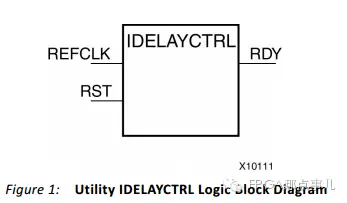

Xilinx器件IO部分都有IDELAYCTRL,很多从Altera转过来的工程师都很疑惑它的用法和作用。IDELAYCTRL是IO的一个模块,在vivado设备可以看到它的位置,通常是按照银行来分布。它能够根据器件的PVT(工艺,电压和温度)差异给IO延迟模块提供精确的延迟抽头。它一定是和IODELAY模块一起使用的,端口RDY代表了IODELAY模块经过正常校准后的结果。

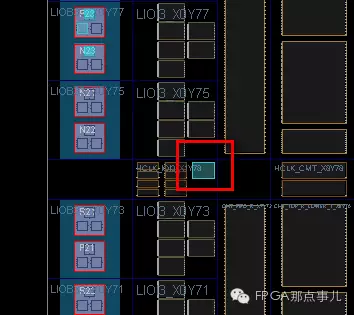

图1.IDELAYCTRL位置(可手动约束),端口模块

模块调用原语:

IDELAYCTRL dlyctrl

(

.RDY(rdy),

.REFCLK(refclk),

.RST(rst)

);

注意事项:

A. IDELAYCTRL需要有复位信号,每次RDY信号拉低后复位,持续50ns以上;

B. REFCLK:频率200MHz,提供延迟的参考抽头基准。

C.当存在跨银行管脚都需要IDELAYCTRL时,最好按照银行复制调用,和LOC约束,否则工具可能报错。了解一下IDLEAY属性,可以更好地了解IDELAYCTRL

IDELAYE2#(

.CINVCTRL_SEL(“ FALSE”),//启用动态时钟反转(“ TRUE” /“ FALSE”)//这可能对异步模式很有帮助

.DELAY_SRC(“ IDATAIN”),

.HIGH_PERFORMANCE_MODE(“ TRUE”),

.IDELAY_TYPE(“ VARIABLE”),

.IDELAY_VALUE(0),

.REFCLK_FREQUENCY(200.0),

.SIGNAL_PATTERN(“ DATA”),

.PIPE_SEL(“ FALSE”)

更多信息,请参考xilinx手册ug471。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/IT小白/article/detail/614413

推荐阅读

相关标签