热门标签

热门文章

- 1计算机视觉(AI)面试大全_计算机视觉面试题

- 2html网页制作之简单登入界面_html表格登录界面

- 3AI CC呼叫中心源码_ai呼叫中心源代码

- 4详细讲解axios封装与api接口封装管理_axios api封装

- 5[SQL挖掘机] - 日期函数 - current_date

- 6用实例带你快速玩转git_玩转 git

- 7软件测试工程师应该学Python还是学Java?_电子产品测试学什么语言

- 8RocketMq-主从集群搭建_rocketmq 主从配置

- 9Java 函数方法指南:如何获取给定日期的月份最后一天_java获取指定时间字符串的月份最后一天

- 10树莓派4B 六个串口的开启与使用_raspberry uart3

当前位置: article > 正文

Verilog仿真跨模块调用内部信号的方法

作者:Monodyee | 2024-04-19 22:49:17

赞

踩

Verilog仿真跨模块调用内部信号的方法

在Verilog仿真时如果需要调用某子模块中的信号在本模块中使用可以使用层次化引用的方法,而不需要在rtl部分用端口引出来。

引用方式:当前例化模块名.子例化模块名.子子例化模块名.参数 将需要的信号引出。

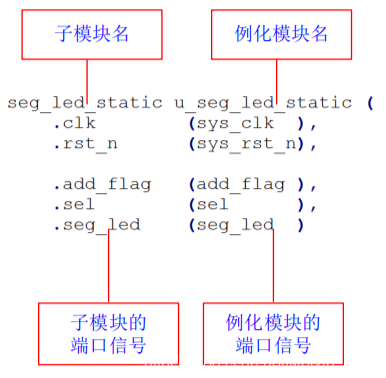

注意是用例化模块名而不是用子模块名,两者区别如下:

如示例代码中的有两处分别引用不同子模块中的信号在本模块使用。

`timescale 1ns/1ns

module tb_top();

wire i_rst_n ;

assign i_rst_n = u_top.u_ctrl.w_sys_rst_n;

reg [7:0] data_in ;

reg clr_n ;

initial begin

i_clk = 1'b1;

clr_n <= 1'b0 ;

data_in <= 8'b0 ;

#520

wait (u_top.u_trig.w_sam_en == 1'b1)begin

clr_n <= 1'b1 ;

data_in <= 8'h5A ;

end

top u_top(

.i_ext_clk (i_clk ),

.o_spi_sclk (o_spi_sclk ),

.o_spi_mosi (o_spi_mosi ),

.i_spi_miso (i_spi_miso )

);

//==========================< Clock block >============================

always #10 i_clk = ~i_clk;

endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

实际上有多种层级引用方式:可参考Verilog基础:标识符的向上向下层次名引用

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/Monodyee/article/detail/454027

推荐阅读

相关标签