- 1vue中elementUI的Loading.service函数的封装

- 26、杨辉三角(蓝桥杯基础题)_杨辉三角形又称pascal三角形,它的第i+1行是(a+b)i的展开式的系数。 它的一个

- 3NLP-信息抽取-关系抽取-2017:LSTM-LSTM-bias实体识别-关系联合抽取【基于一种新的标注策略进行实体和关系的联合抽取】_关系指导的实体关系联合抽取

- 4Logistic回归 R语言_r语言logistics回归调整协变量

- 5蓝桥杯python(二)_将英语单词用小写字母表示,并删除单词后缀er,ly,ing。若单词非这三种后缀,直接将

- 6Java实现链表反转的两种思路

- 7【免费题库】华为OD机试 - 猴子爬山(Java & JS & Python & C & C++)

- 8Hadoop集群部署(基于2.7.1)_启动hadoop,在hdfs中创建用户目录“/user/hadoop”;

- 9大数据分析应用领域有哪些_大数据应用

- 10【群智能算法改进】一种改进的沙丘猫群优化算法 改进沙丘猫群算法 改进SCSO[1]【Matlab代码#34】_logistic混沌初始化

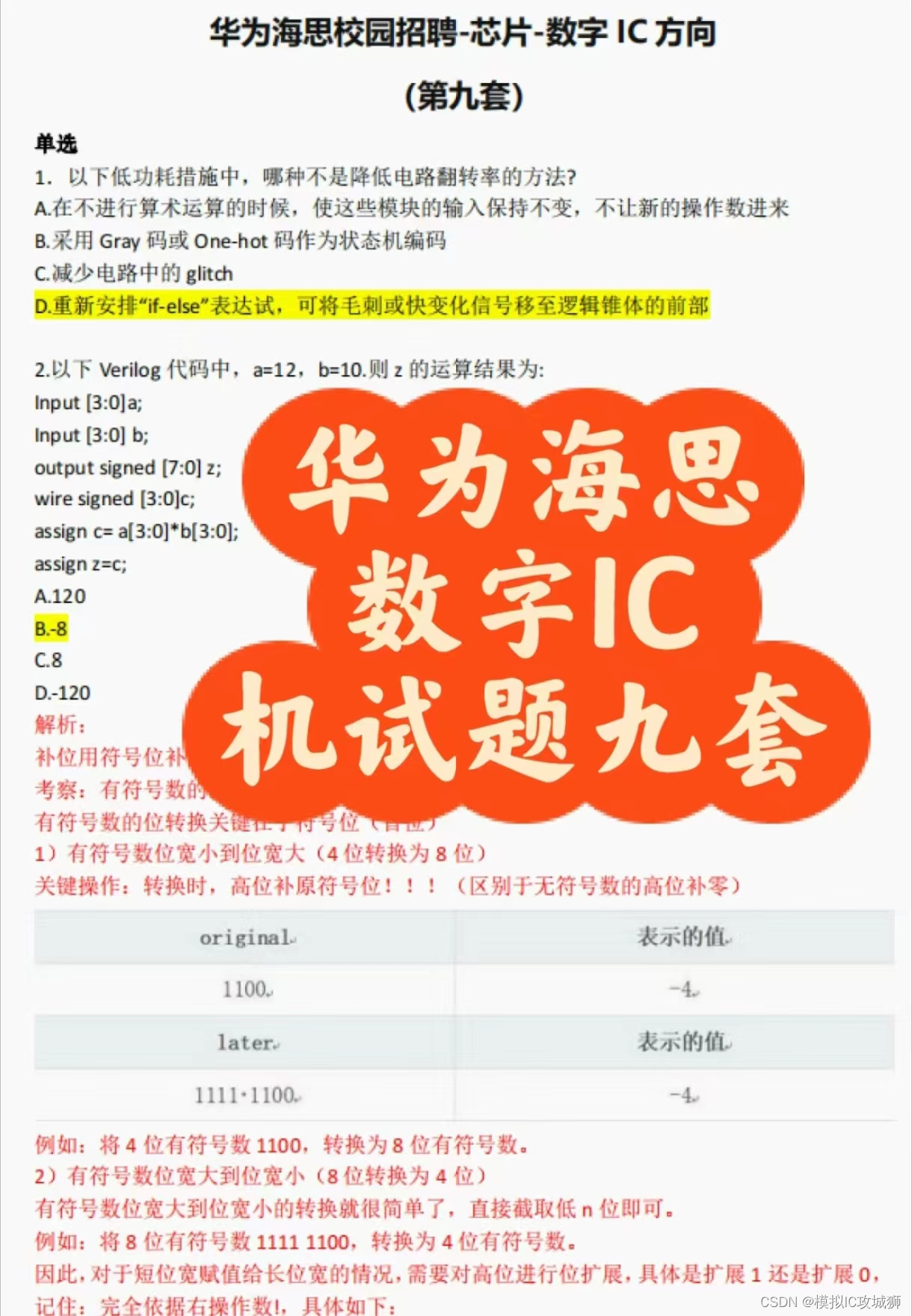

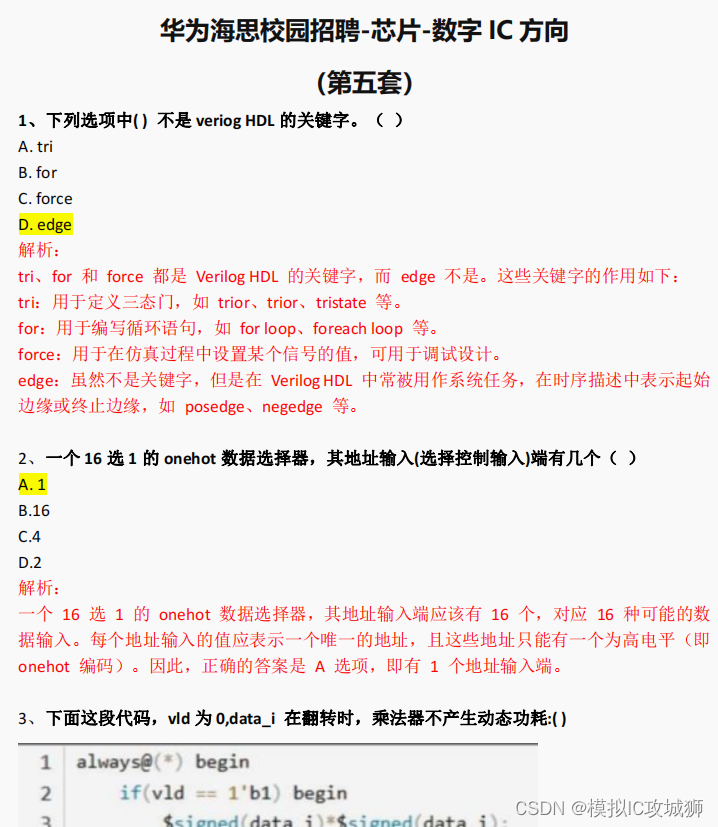

华为海思校园招聘-芯片-数字 IC 方向 题目分享——第五套

赞

踩

华为海思校园招聘-芯片-数字 IC 方向 题目分享——第五套

(共9套,有答案和解析,答案非官方,仅供参考)(共九套,每套四十个选择题)

部分题目分享,完整版获取(WX:didadidadidida313,加我备注:CSDN huawei数字芯片题目,谢绝白嫖哈)

华为海思校园招聘-芯片-数字 IC 方向

(第五套)

1、下列选项中( ) 不是 veriog HDL 的关键字。( )

A. tri

B. for

C. force

D. edge

解析:

tri、for 和 force 都是 Verilog HDL 的关键字,而 edge 不是。这些关键字的作用如下:

tri:用于定义三态门,如 trior、trior、tristate 等。

for:用于编写循环语句,如 for loop、foreach loop 等。

force:用于在仿真过程中设置某个信号的值,可用于调试设计。

edge:虽然不是关键字,但是在 Verilog HDL 中常被用作系统任务,在时序描述中表示起始

边缘或终止边缘,如 posedge、negedge 等。

2、一个 16 选 1 的 onehot 数据选择器,其地址输入(选择控制输入)端有几个( )

A. 1

B.16

C.4

D.2

解析:

一个 16 选 1 的 onehot 数据选择器,其地址输入端应该有 16 个,对应 16 种可能的数

据输入。每个地址输入的值应表示一个唯一的地址,且这些地址只能有一个为高电平(即

onehot 编码)。因此,正确的答案是 A 选项,即有 1 个地址输入端。

3、下面这段代码,vld 为 0,data_i 在翻转时,乘法器不产生动态功耗:( )

注:这里原题中 if 块就没有赋值语句

A.正确

B.错误

解析:

在 vld 为 0 时,根据代码,乘法器还是会执行,此时的输入会被看做是零,输出也为零。因

此,即使 vld 为零,乘法器仍会产生动态功耗。

正确的代码应该使用一个逻辑门来控制乘法器,如下所示:

这样,在 vld 为零时,乘法器不会被激活,输出将保持为零,从而避免动态功耗的产生。

4、下列说法正确的是( )

A.reg 变量一定被综合为寄存器

B.always 块一定是用来描述时序逻辑的

C.变量类型定义为 memory 类型只能使用 always 进行赋值

D.变量类型定义为 memory 类型可以使用 assign 进行赋值

解析:

A. reg 变量一定被综合为寄存器是正确的。

在 Verilog 中,reg 声明的变量在综合时通常被翻译为寄存器(RG)。这是因为 reg 变量只能被

赋值,没有输出,只能在 always 块中被操作。因此,在综合时,reg 对应的硬件元件就是寄

存器。

B. always 块一定是用来描述时序逻辑的是不正确的。

always 块可以用来描述时序逻辑,也可以用来描述组合逻辑。always 块中的代码可以根据不

同的敏感信号(posedge、negedge、level)触发更新,实现时序逻辑;也可以在逻辑内部进行

组合逻辑的操作,根据输入信号得到输出信号。

C. 变量类型定义为 memory 类型只能使用 always 进行赋值是正确的。

在 Verilog 中,memory 是一种多位数据类型,通常用于描述类似于 RAM 的组合逻辑电路。

memory 类型的变量只能使用 always 块来进行操作,无法使用 assign 来赋值。

D. 变量类型定义为 memory 类型可以使用 assign 进行赋值是不正确的。

memory 类型的变量只能使用 always 块来进行赋值,不能使用 assign。assign 是用于描述组

合逻辑的关键字,而 memory 类型的变量是一种综合成组合逻辑的多位数据类型,不能直接

用于 assign 赋值。

5、描述时序逻辑时,只有 if 条件分支没有 else 分支有助于综合(Desgn Compile,DC)自动插

icg ( )

A.正确

B.错误

解析:

A. 不正确。Verilog 中的 reg 变量可以被综合为寄存器或者组合逻辑。综合工具会根据代码

逻辑和综合规则决定 reg 变量被综合为何种逻辑。

C. 不正确。Verilog 中的 memory 类型的变量需要使用 initial 或者 always 块进行赋值,其

中 initial 块是用来初始化存储器中的数据, always 块则可以用来描述存储器的时序逻辑。

D. 不正确。Verilog 中的 memory 类型的变量不能使用 assign 进行赋值,只能使用 initial

块或者 always 块。

因此,正确的选项是 B。always 块主要是用来描述时序逻辑的。

6、以下逻辑正确( )

A.正确

B.错误

解析:

这段代码存在语法错误和逻辑错误。正确的 Verilog HDL 代码应该类似于下面的形式:

其中:

首先定义了一个名为 HIGH_PRI 的参数,并将其赋值为 0。

使用 if‐else 结构进行条件判断:

o 如果 HIGH_PRI 的值为 1,则将 o 的值设置为 c 的值。

o 如果 HIGH_PRI 的值不为 1,则将 a 的值设为 b 的值。

7、将逻辑通过 CLK Gate 方式引入 CK 路径中,可以减少 D 端逻辑的路径时延( )

A 正确

B.错误

解析:

将逻辑通过 CLK Gate 的方式引入时钟路径中,可以在时钟信号到达寄存器 D 端之前,关

闭时钟信号,从而减少 D 端逻辑的路径时延,减小时钟抖动以及减少功耗。

当时钟信号到达时钟栅门时,如果 CLK Gate 处于关闭状态,则时钟信号被阻断,在时钟信

号到达寄存器的 D 端之前,数据输入信号不能进入寄存器,以此减少逻辑路径的时间延迟。

因此,将逻辑通过 CLK Gate 的方式引入 CK 路径中,可以减少 D 端逻辑的路径时延,同

时还可以减小时钟抖动和功耗。

8、I2C 器件中,7bit 模式的器件和 10bit 地址模式的器件,可以连接到同一个 2C 总线中?( )

A.正确

B.错误

解析:

I2C 总线支持 7 位和 10 位寻址模式。7 位寻址模式提供 128 个地址,而 10 位寻址模式

提供 1024 个地址。I2C 总线允许同时连接 7 个 7 位寻址模式的器件,和 1024 个 10 位

寻址模式的器件。因此,7 位模式的器件和 10 位地址模式的器件可以连接到同一个 I2C 总

线中,且不会有冲突。

需要注意的是,连接多个器件到 I2C 总线中需要非常小心,因为总线上的信号是共享的,

在不合理的设计或错误的连接方式下,可能会导致总线的电气特性失衡,而导致系统故障。

9、下面代码 c、b 信号每个时钟周期都相同( )

A.正确

B.错误

解析:

根据 Verilog HDL 中的信号赋值规则,在一个时钟上升沿到来时,always 块中的代码会被并

行执行。这意味着在一个时钟周期内,always 块中的所有语句都会被执行完成。在本例中,

always 块在上升沿时被执行,将 b 的值设置为 a 的值,然后再将 c 的值设置为 b 的值。因此,

指导下一个上升沿到来,c 和 b 的值都不会发生变化,且在每个时钟周期中,b 和 c 的值都相

同。