热门标签

热门文章

- 1运维笔记:inotify+rsync实现实时监控备份_centos 实时同步备份

- 2【栈】无法吃午餐的学生数量(leetcode1700)_无法吃午餐的学生数量 leetcode python

- 3Socket编程详解

- 4Ubuntu20.04下安装QtCreator 5.14.2(安装/卸载/创建快捷键/添加收藏)_ubuntu20.04 qtcreator

- 5Linux—root密码丢失重置_linux系统忘记root密码

- 6Java实现简易UDP客户端、服务器端通信程序_java 创建一个udp服务

- 7【原创】程序员必备的10大健康装备!——我们要工作更要健康!

- 8最细致讲解yolov8模型推理完整代码--(前处理,后处理)_yolov8推理

- 924个提高知识和技能极限的机器学习项目_有点难度的机器学习项目

- 1052-Android之内置应用_libcrashpad_handler_trampoline

当前位置: article > 正文

冯诺依曼体系结构_存算一体:突破冯诺依曼架构瓶颈的希望?

作者:weixin_40725706 | 2024-02-21 08:54:19

赞

踩

存算一体 冯诺依曼结构

半导体技术发展至今,已进入后摩尔定律时代。通过提升工艺来提升冯·诺依曼架构性能的难度越来越大。存算一体(In-memory Computing)作为一种新兴的技术,为彻底解决冯诺依曼架构的瓶颈带来了希望。

01

—

冯·诺依曼架构的瓶颈

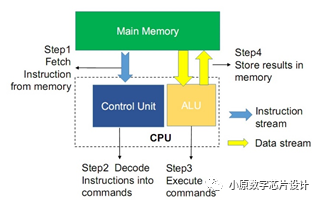

传统的计算机采用冯·诺依曼体系结构,在这种体系结构中计算和存储功能是分离的,分别由中央处理器CPU 和存储器完成。CPU 和存储器通过总线互连通信,CPU 从存储器读出数据,完成计算,然后将结果写回存储器。

Fig. 1. 冯·诺依曼架构示意图

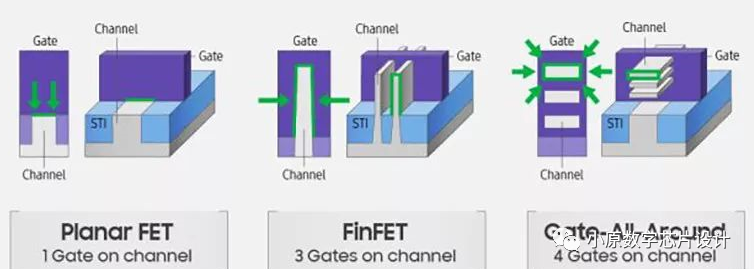

随着半导体产业的发展和需求的差异,处理器和存储器二者之间走向了不同的工艺路线。面向用户对处理器的高性能需求,半导体厂商通过减小器件尺寸,使用更多的金属布线层来降低互连线延迟,不断提高处理器的性能。

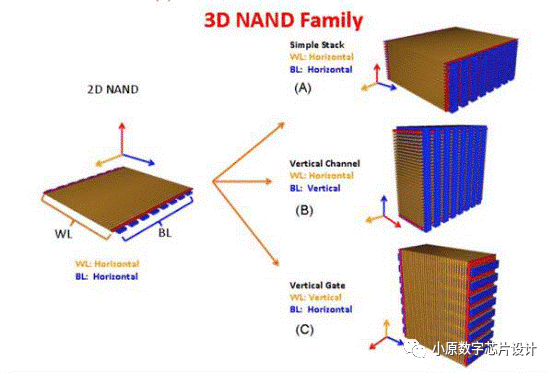

Fig. 3. 3D NAND Flash Memory

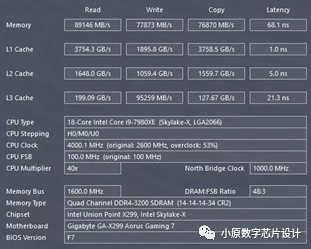

处理器与存储器需求不同,工艺不同,封装不同,导致二者在工业生产层面无法完美兼容,且二者之间的性能差距越来越大。当前主流的商用微处理器主频已达3GHz以上,存储总线主频仅400MHz;处理器速度每年增长60%,存储器存取延迟每年仅改善7%。处理器性能远远大于DRAM。由通信带宽和延迟构成的“存储墙(Memory wall)”成为提高系统性能的最大障碍。以Intel i9-7980XE 18 核 36 线程CPU为例,其配合超频过的 DDR4 3200MHz 的内存,测试出的内存读取速度为 90GB/S。再看图中的 L1 Cache,3.7TB/S。这颗 CPU 最大睿频 4.4GHz,就是说 CPU 执行一个指令需要的时间是0.22ns(纳秒),而内存的延迟是 68.1ns。换句话说,只要去内存里取一个字节,就需要 CPU 等待 300 个周期。

Fig. 4. CPU and cache memory speed mismatch

存储与计算模块的分离带来的问题还有功耗墙(powe

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/weixin_40725706/article/detail/122227

推荐阅读

相关标签