热门标签

热门文章

- 1conda install pytorch==1.0.0 或者 conda install pytorch==0.4.0,提示mkl>=2018的解决办法_conda mkl >=2018

- 2BeanPostProcessor妙用(转载)_beanpostprocessor实际用处·

- 3Linux中的软连接和硬链接

- 4android 4.0 BLE开发官方文档介绍_ble 官方文档

- 5NLP实践:pytorch 实现基于LSTM的预训练模型以及词性分类任务_mytorch加载预训练模型nlp

- 6ElasticSearch父子关联文档实现关系型数据库join操作_es 父子关联

- 7【面试题 - mysql】进阶篇 - MVCC多版本并发控制原理_mysql mvcc面试题

- 8我的创作纪念日——文章汇总

- 9python自动化测试工具selenium使用指南_python 使用 selenium

- 10一个字稳,云原生产品家族支撑冬奥会九大业务场景,打造云上奥运新体验_冬奥会的核心应用系统包括

当前位置: article > 正文

数字秒表设计仿真VHDL跑表,源码,视频_简易跑表仿真图

作者:weixin_40725706 | 2024-05-07 16:36:18

赞

踩

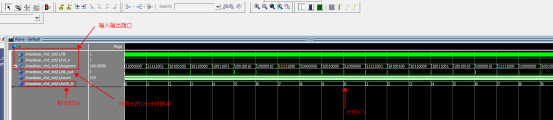

简易跑表仿真图

名称:简单秒表设计仿真VHDL跑表

软件:Quartus

语言:VHDL

代码功能:

数字秒表功能描述

本次练习只需要一个数码管(假设该数码管已被选中),实现数码管显示功能,具体要求如下(设数码管为共阳)

1)实现秒表计时功能。

2)复位时,数码管显示

3)数码管依次从0变到9显示。

2信号列表 clk:50MHz的工作时钟,输入

系统复位信号,输入,低电平有效

segment:8位,输出,数码管显示信号,共8位。由低到高,分别表示数码管的a,b,c,d,e,f,g,h。当该比特为0时,表示点亮相应位置;为1时熄灭。

本代码包含2个工程,2工程代码一样,但是一个使用modelsim仿真,一个使用quartus自带的wvf仿真。

演示视频:简单秒表设计仿真VHDL跑表_Verilog/VHDL资源下载

FPGA代码资源下载网:hdlcode.com

代码下载:

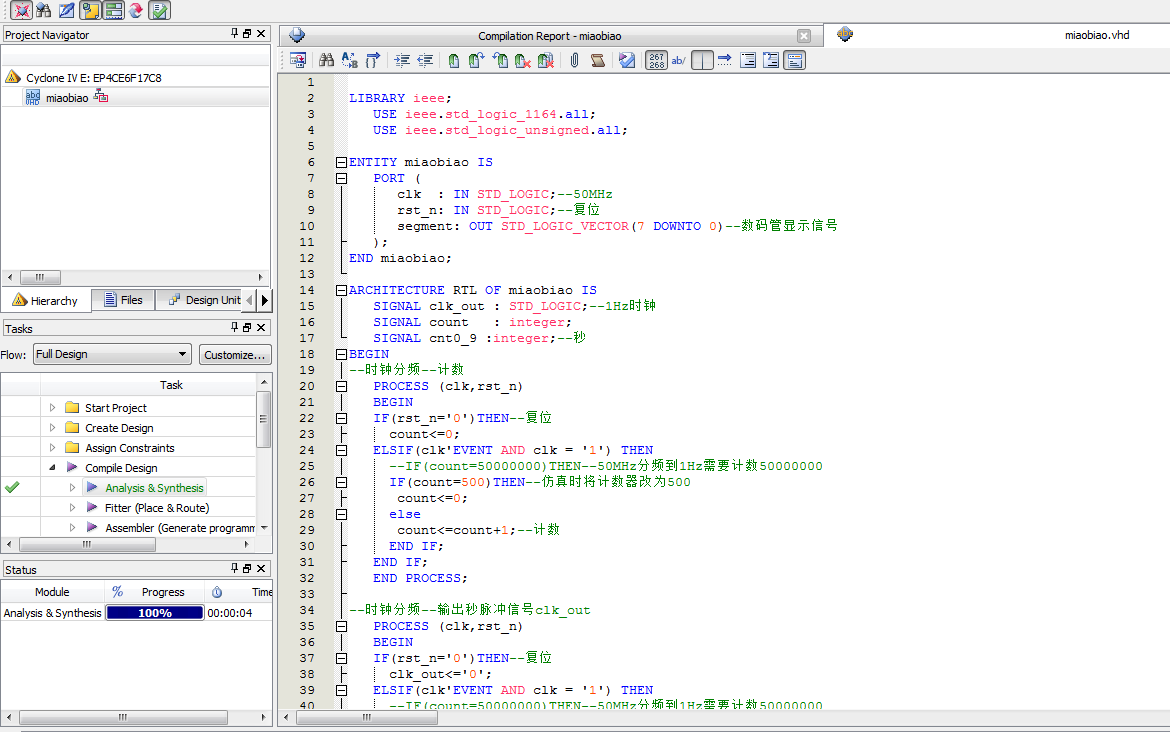

部分代码展示

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; ENTITY miaobiao IS PORT ( clk : IN STD_LOGIC;--50MHz rst_n: IN STD_LOGIC;--复位 segment: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管显示信号 ); END miaobiao; ARCHITECTURE RTL OF miaobiao IS SIGNAL clk_out : STD_LOGIC;--1Hz时钟 SIGNAL count : integer; SIGNAL cnt0_9 :integer;--秒 BEGIN --时钟分频--计数 PROCESS (clk,rst_n) BEGIN IF(rst_n='0')THEN--复位 count<=0; ELSIF(clk'EVENT AND clk = '1') THEN --IF(count=50000000)THEN--50MHz分频到1Hz需要计数50000000 IF(count=500)THEN--仿真时将计数器改为500 count<=0; else count<=count+1;--计数 END IF; END IF; END PROCESS; --时钟分频--输出秒脉冲信号clk_out PROCESS (clk,rst_n) BEGIN IF(rst_n='0')THEN--复位 clk_out<='0'; ELSIF(clk'EVENT AND clk = '1') THEN --IF(count=50000000)THEN--50MHz分频到1Hz需要计数50000000 IF(count=500)THEN--仿真时将计数器改为500 clk_out<='1';--输出1Hz秒计时信号 else clk_out<='0'; END IF; END IF; END PROCESS; --秒计数 PROCESS (clk_out,rst_n) BEGIN IF(rst_n='0')THEN--复位 cnt0_9<=0; ELSIF(clk_out'EVENT AND clk_out = '1') THEN--使用秒脉冲信号计数 IF(cnt0_9<9)THEN--最大到9 cnt0_9<=cnt0_9+1;--加 else cnt0_9<=0;--清零 END IF;

设计文档:

设计文档.doc ----quartus仿真

设计文档.doc ----modeslim仿真

1. 工程文件

2. 程序文件

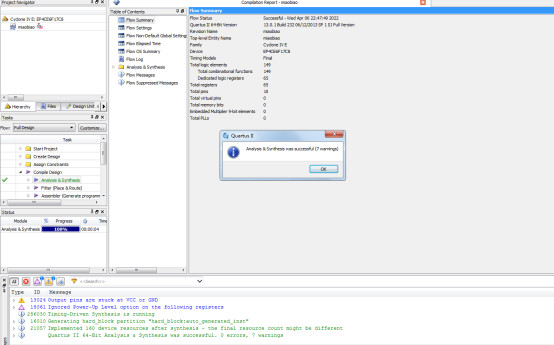

3. 程序编译

4. Testbench

5. modelism仿真图

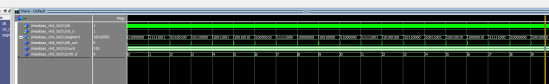

6. quartus wvf仿真图

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/weixin_40725706/article/detail/550207

推荐阅读

相关标签