- 1GitHub标星即将突破100K!辛辛苦苦才给你整理了188道Java面试题,如此干货,不来白嫖血亏_一万个人抢100个红包,如何实现(不用队列),如何保证2个人不能抢到同一个红包

- 2最新Java必备技能之环境搭建篇 (linux ab压力测试Nginx)(实战)(3),2024年最新面试软件测试工程师会问到那些问题_nginx ab测试

- 3全面解析自然语言处理(NLP):基础、挑战及应用前景_nlp自然语言处理

- 4C语言练习,利用求阶乘函数Fact(),编程计算并输出从1到n之间所有数的阶乘值。_利用求阶乘函数fact(),编程计算并输出从1到n之间所有数的阶乘值。 **输入格式要求

- 5【眼疾病识别】图像识别+深度学习技术+人工智能+卷积神经网络算法+计算机课设+Python+TensorFlow

- 6avr单片机led数码管六位动态显示时分秒c语言程序,AVR单片机8位数码管显示的程序实现(两种方法介绍)...

- 7原来的cpu程序,现在要用到GPU了,makefile咋改_makefile.gpu

- 8【运维知识高级篇】一篇文章带你搞懂代码质量检测SonarQube!_sonarqube质量阈错误

- 9vue3 选项式生命周期API 和 组合式生命周期API 执行先后顺序

- 10机器学习模型可解释性进行到底 —— SHAP值理论(一)_shap算法

vivado 设置设备约束_dci cascade

赞

踩

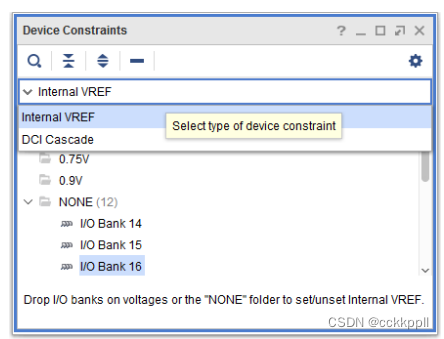

设置设备约束

在“设备约束”窗口(如下图所示)中,可以设置约束,包括DCI_ CASCADE和INTERNAL_。AMD设备具有可配置的SelectIO™支持许多标准接口的接口驱动程序和接收器。此功能集包括输出强度和转换速率的可编程控制,使用数字控制阻抗(DCI)的片上终端,以及内部生成参考电压的能力(INTERNAL_VREF)。根据I/O标准,AMD DCI可以控制驱动器的输出阻抗,也可以为驱动器、接收器或两者添加并行端接,目的是准确匹配传输线的特性阻抗。DCI主动调整I/O内部的阻抗以校准VRN和VRP引脚上的外部精密参考电阻器。这补偿由于工艺变化或温度变化引起的I/O阻抗变化以及电源电压。

DCI在每个I/O组中使用两个多用途参考引脚来控制驱动器的阻抗或组中所有I/O的并联端接值。具有差分输入缓冲器的单端I/O标准需要VREF。当VREF为在I/O组中需要,使用该组的以下引脚作为VREF电源输入:

•对于基于UltraScale体系结构的设备,请使用专用的VREF引脚

•对于7系列设备,使用两个多功能VREF引脚或者,可以使用internal_VREF约束生成内部VREF。使用内部参考电压可以消除在PCB,并且可以释放给定I/O组中的多用途VREF引脚用于其他I/O端口分配。每个I/O组都有一个VREF平面,每个组都可以将可选的INTERNAL_VREF设置为整个组的单个电压电平。

创建DCI_CASCADE约束

DCI_CASCADE约束将两个或多个相邻的I/O组链接在一起以供DCI参考电压目的。具有DCI参考电压的I/O组为主,所有其他I/O级联中的银行是奴隶。级联中的所有银行必须位于的同一I/O列中装置

注意:您可以为7系列设备、Zynq 7000和UltraScale配置DCI_CASCADE约束基于体系结构的设备。有关此约束的详细信息,请参见Vivado中的DCI_CASCADE《设计套件属性参考指南》(UG912)。要创建DCI_CASCADE约束,请执行以下操作:

1.在“设备约束”窗口中,从顶部的下拉列表中选择“DCI级联”窗户。

2.选择要级联的I/O组,右键单击,然后选择“添加DCI级联”。

3.在Add DCI Cascade(添加DCI级联)对话框中,选择一个I/O组作为新DCI的主机级联,然后单击“确定”。主库显示在“设备约束”窗口中。

注:DCI级联必须有一个主I/O组和至少一个从I/O组。

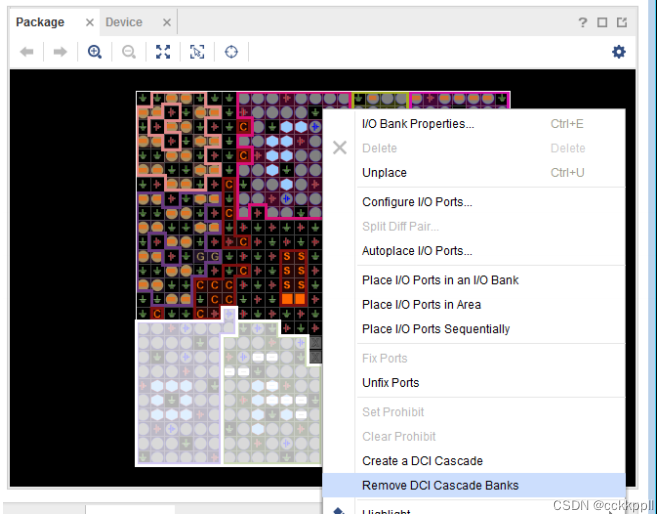

提示:或者,也可以在Package窗口或Package Pins中创建DCI_CASCADE约束窗在要级联的库上单击鼠标右键,然后选择“创建DCI级联”。用于创建DCI_CASCADE约束的Tcl命令示例

注意:使用此Tcl命令时,get_iobanks指定主库。在本例中,31和32是从银行,36是主银行。修改或删除DCI级联约束要修改DCI级联,请在“设备约束”窗口中执行以下任意操作:

•要更改主控形状,右键单击DCI级联,然后选择添加DCI级联。在Add DCI中在“级联”对话框中,选择另一个银行作为主银行。

•要将I/O组添加到DCI级联,请将I/O组拖放到DCI层叠上。

•要从DCI级联中删除I/O组,请将I/O组拖放到“未使用”文件夹

•要删除整个DCI级联,右键单击DCI级联并选择删除DCICascade Banks)。

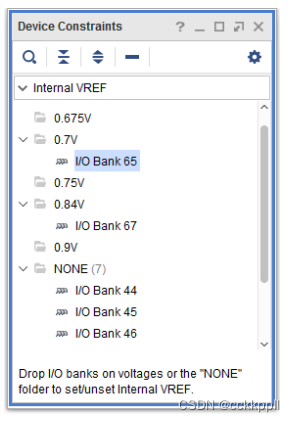

创建INTERNAL_VREF约束

AMD设备可以通过启用INTERNAL_VREF约束。内部生成消除了提供特定PCB上的VREF电源导轨,并释放给定I/O组中的多用途VREF引脚用作普通I/O引脚。

提示:所有没有INTERNAL_VREF约束的I/O组都显示在中的NONE文件夹下设备约束窗口。要创建INTERNAL_VREF约束,请将I/O组拖放到所需电压上文件夹(例如0.7V或0.84V)。

用于创建INTERNAL_VREF约束的Tcl命令示例

设置配置组电压选择

配置组电压选择(CFGBVS)逻辑输入引脚在VCCO_0之间参考和GND。CFGBVS引脚必须设置为高或低,以确定的I/O电压支持气缸组0中的针脚。在Vivado工具中,您可以使用Tcl命令来设置CFGBVS绑定信息到VCCO或GND。您可以设置配置电压或VCCO_0电压,至1.5、1.8、2.5或3.3。基于这些设置,DRC在7系列的气缸组0、14和15上运行设备。对于UltraScale设备,DRC在第0组和第65组上运行。当导出IBIS模型。以下是一个示例:

默认情况下,CFGBVS属性为空。Vivado工具检查CFGBVS属性设置为VCCO或GND。如果CFGBVS属性有一个值,Vivado工具会检查CONFIG_MODE属性。DRC是根据IOSTANDARD和CONFIG_VOLTAGE发布的银行的设置。导出到CSV文件时,Vivado工具为提供VCCO绑定信息相关组(适用于7系列设备:组0、14和15;适用于AMD UltraScale™ 基于体系结构的设备:组0和65)。对于例如,如果使用JTAG/边界扫描,CFGBVS为GND,CONFIG_VOLTAGE为3.3,则工具发出严重警告:DRC CFGBVS-4。这表示CONFIG_VOLTAGE已设置而必须设置为VCCO,其值为1.8。对于AMD UltraScale+™ 设备,不能手动设置CFGBVS或CONFIG_VOLTAGE。默认情况下,CFGBVS设置为GNDCONFIG_VOLTAGE设置为1.8 V。