- 1Hadoop详解_大数据的特点谁提出的

- 2mfc用oledb链接mysql_MFC用ADO连接数据库(ACCESS)

- 3手动下载并安装nltk_data_nltk data lives in the gh-pages branch of this rep

- 46行代码入门RAG开发_rag代码

- 5matlab的边缘检测方法,Matlab多种图像边缘检测方法

- 6Axure RP 9 for Mac/win:打造极致交互体验的原型设计神器_axure mac

- 7【在FastAPI应用中嵌入Gradio界面的实现方法】如何在有一个Fastapi应用的基础上,新加一个gradio程序_gradio fastapi

- 8打造安全高效的身份管理:七大顶级CIAM工具推荐

- 9基于C++Qt实现考试系统[2024-05-05]_qt考试系统

- 10【ubuntu连接xshell最新2024史上最全小白教程】_ubuntu xshell

Xilinx GTY

赞

踩

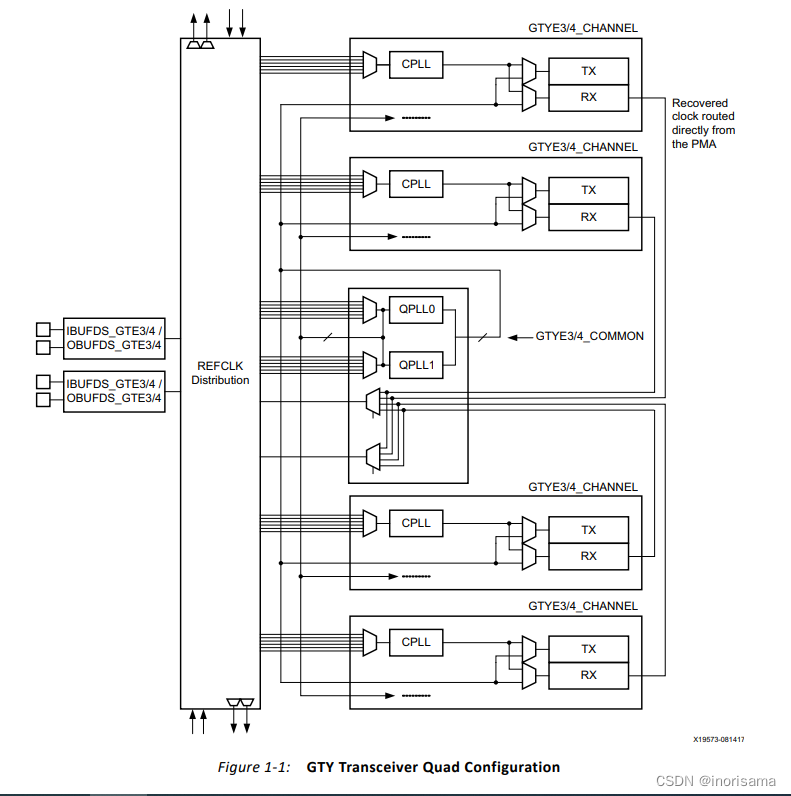

1. GTY 时钟结构

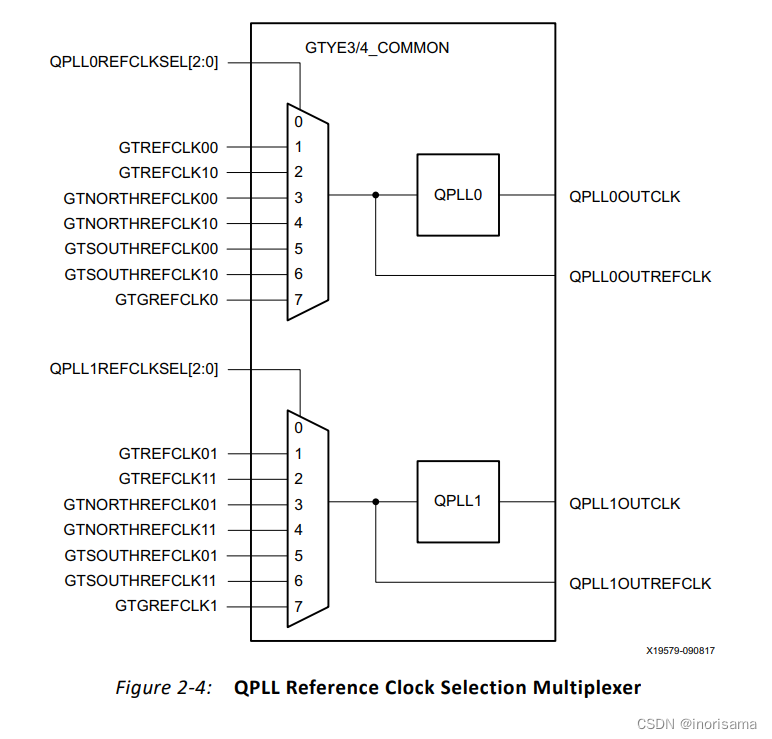

时钟来源如下图所示,通过QPLL_x_REFCLKSEL选择COMMON的时钟源。

2. QPLL & CPLL的结构

PLL基本概念:PLL锁相环知识总结

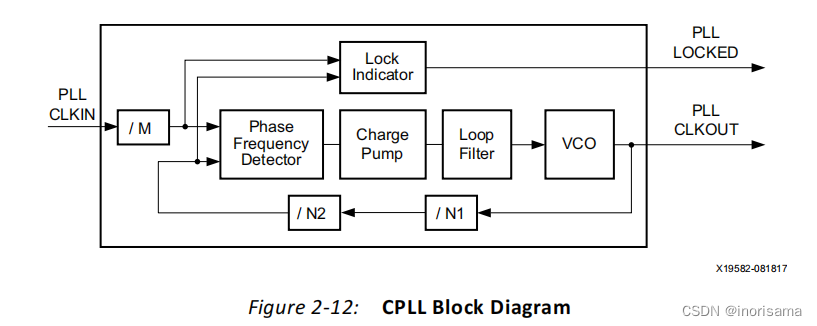

2.1 CPLL

GTY的 CPLL的工作范围是2.0GHz~6.25GHz。输出时钟公式:

GTY的 CPLL的工作范围是2.0GHz~6.25GHz。输出时钟公式:

线速率计算方式:

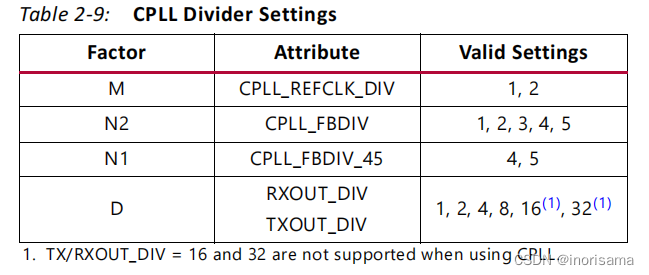

其中N1,N2,M,D的取值范围为:

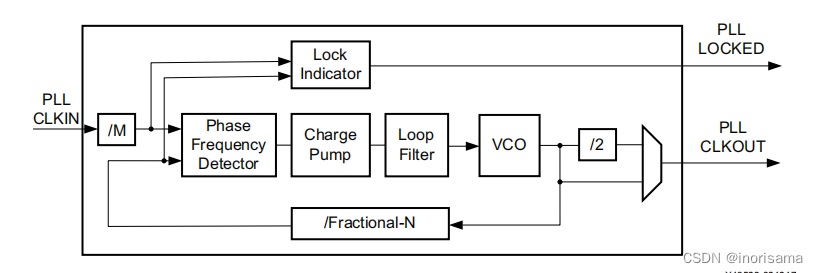

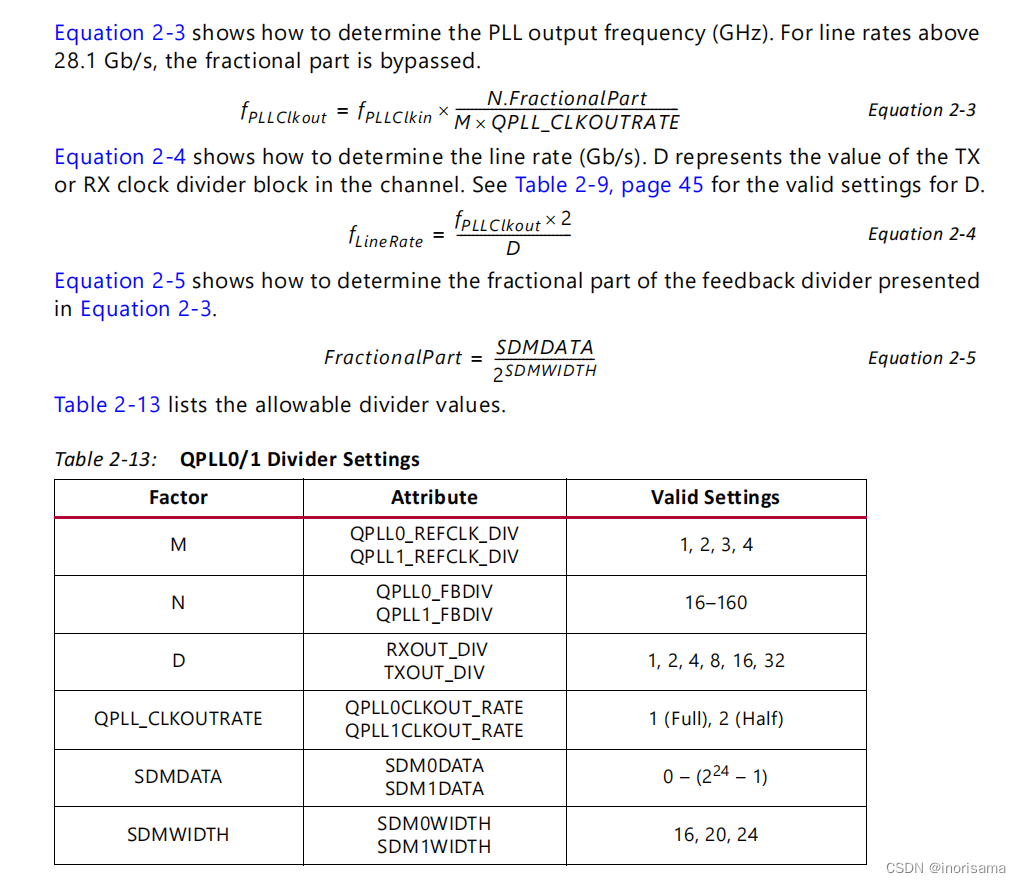

2.2 QPLL

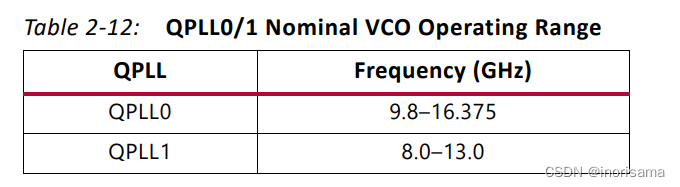

QPLL0和QPLL1的区别:

从QPLL结构来看,相比CPLL,出了VCO的输出评率范围属于高频段外,QPLL提供了分数倍频,能够控制的输出频率更加精细。

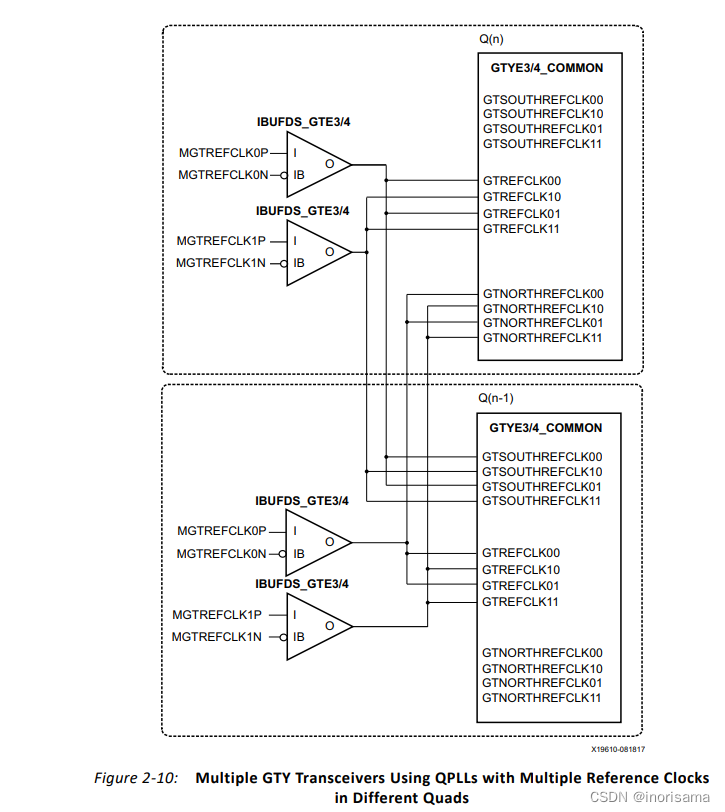

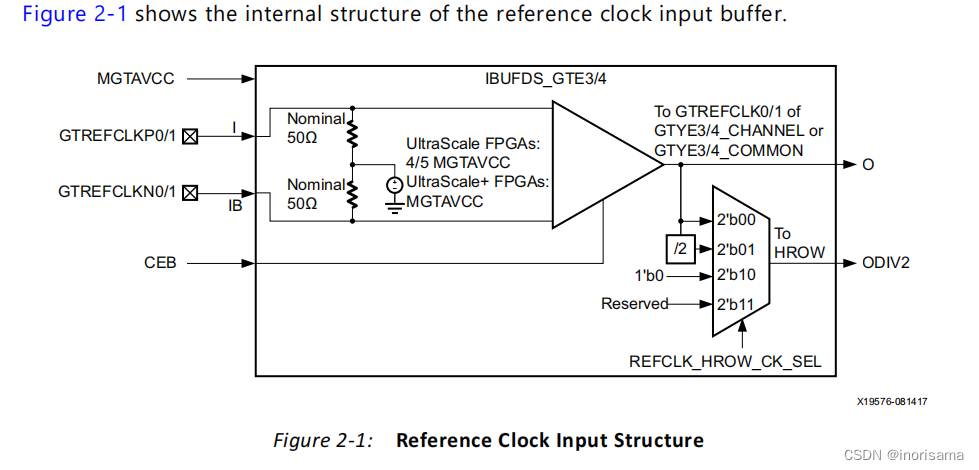

2. IBUFDS_GTEx

在Transceiver中,使用的REFCLK[0/1]从PAD进入FPGA后,首先需要经过特殊的基本单元模块——IBUFDS_GTEx,

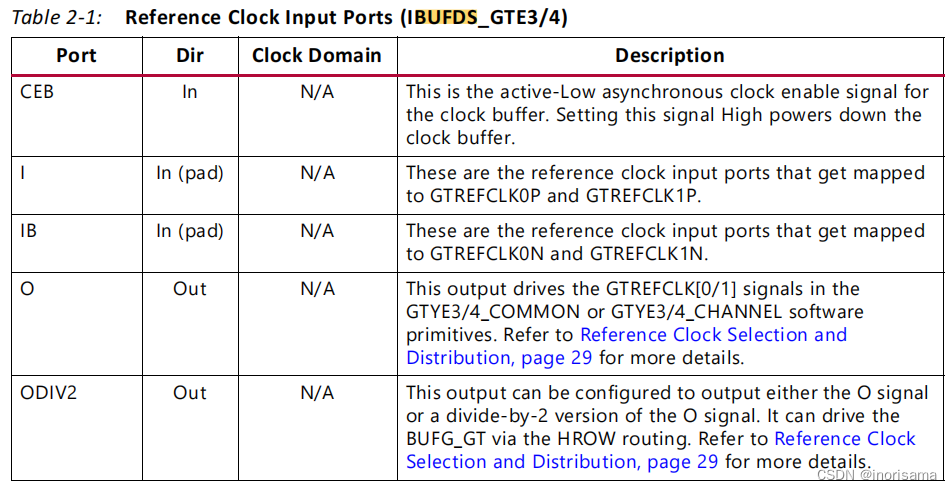

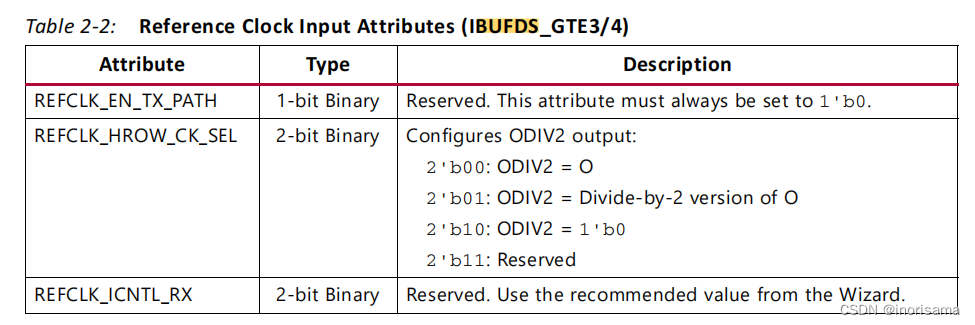

其端口定义为:

其端口定义为:

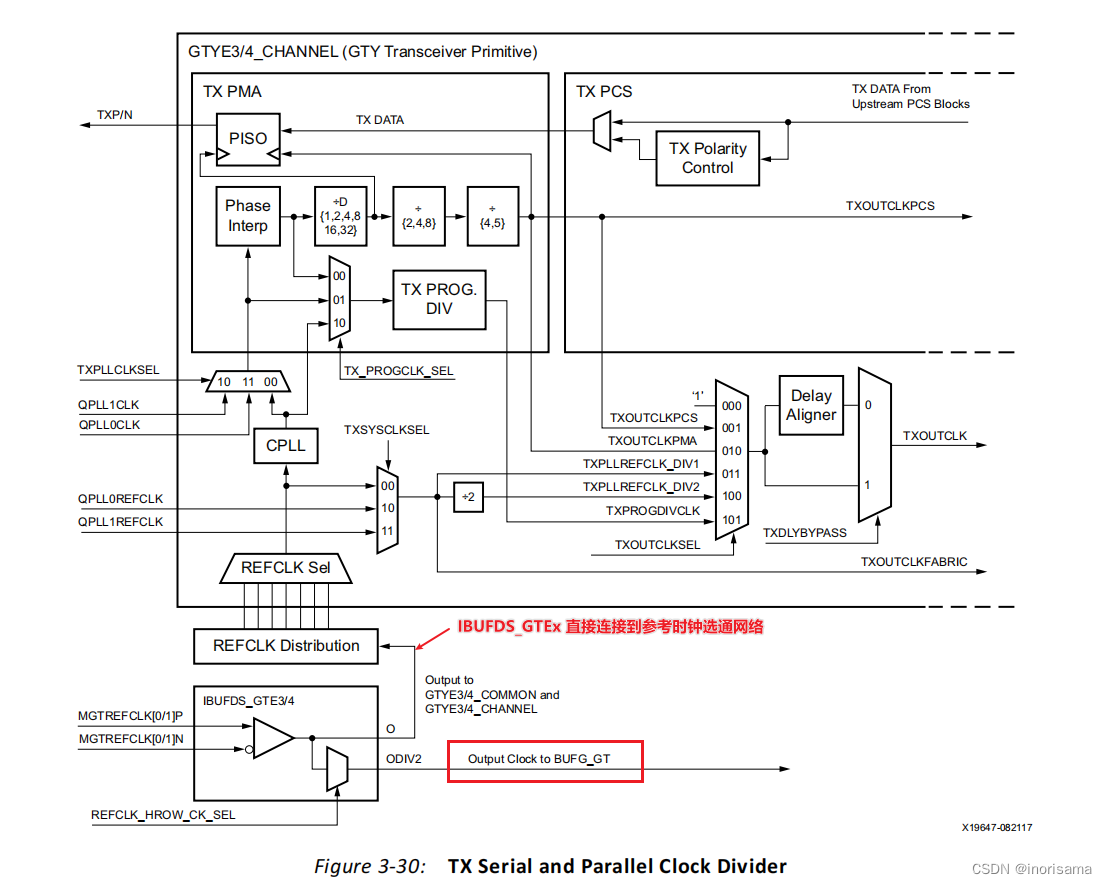

可以看出,IBUFDS_GTEx和普通的IBUFDS是有明显的区别的:它的输出端口O只能用作驱动基本模块GTYx_COMMON/GTY_CHANNEL 的GTREFCLK[0/1],而不能作为其他用途。如果想使用输入参考时钟驱动用户逻辑,需要使用ODIV2+BUFG的方式,将REFCLK引入到FPGA的全局时钟网络,如下图所示:

可以看出,IBUFDS_GTEx和普通的IBUFDS是有明显的区别的:它的输出端口O只能用作驱动基本模块GTYx_COMMON/GTY_CHANNEL 的GTREFCLK[0/1],而不能作为其他用途。如果想使用输入参考时钟驱动用户逻辑,需要使用ODIV2+BUFG的方式,将REFCLK引入到FPGA的全局时钟网络,如下图所示:

从TXOUTCLKPMA 和TXOUTCLKPCS的分频关系可以看出 :

PMACLK = PCSCLK x {8,10,16,20,32,40}

TXOUTCLK 的来源:

PCSCLK,

PMACLK,

TXPLL_REF_CLK_DIV1,

TXPLL_REF_CLK_DIV2,

TXPROGDIV_CLK(来源于QPLL0,QPLL1,CPLL)的分频

IBUG_GTEx 的源语定义如下:

- IBUFDS_GTE3 #(

- .REFCLK_EN_TX_PATH(1'b0), // Refer to Transceiver User Guide.

- .REFCLK_HROW_CK_SEL(2'b00), // Refer to Transceiver User Guide.

- .REFCLK_ICNTL_RX(2'b00) // Refer to Transceiver User Guide

- )IBUFDS GTE3 inst (

- .O() // 1-bit output: Refer to Transceiver User Guide.

- .ODIV2(ODIV2), // 1-bit output: Refer to Transceiver User Guide.

- .CEB(CEB), // 1-bit input: Refer to Transceiver User Guide.

- .I(I) , // 1-bit input: Refer to Transceiver User Guide.

- .IB(IB) // 1-bit input: Refer to Transceiver User Guide.

- );

- // End of IBUFDS_GTE3_inst instantiation

参考资料:

【VIVADO IP】UltraScale FPGAs Transceivers Wizard - 知乎 (zhihu.com)