热门标签

当前位置: article > 正文

基于FPGA的数字时钟设计Verilog代码Quartus仿真_fpga仿真时钟信号产生程序

作者:不正经 | 2024-06-15 10:33:45

赞

踩

fpga仿真时钟信号产生程序

名称:基于FPGA的数字时钟设计Verilog代码Quartus仿真(文末获取)

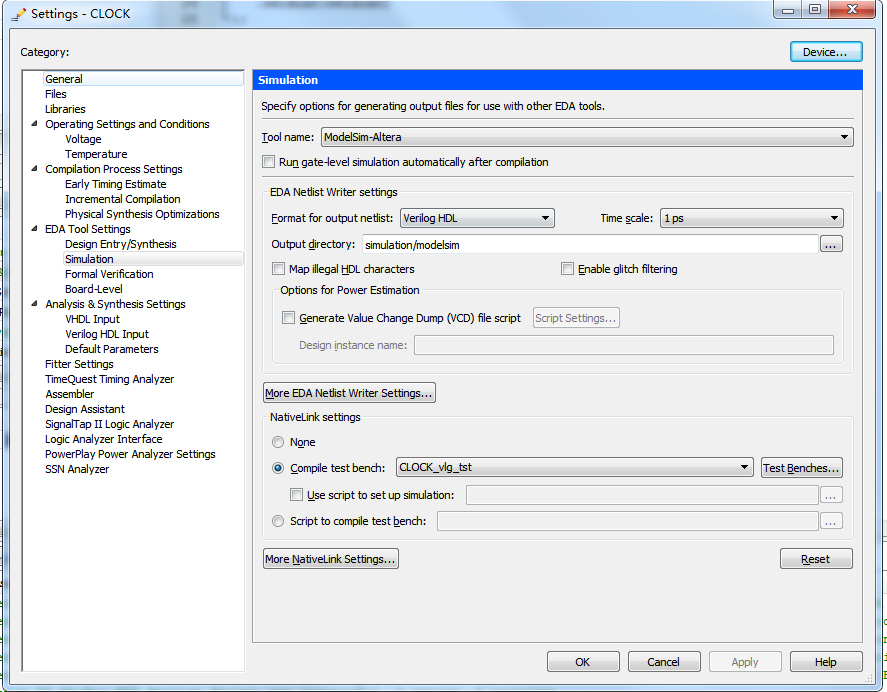

软件:Quartus

语言:Verilog

代码功能:

设计要求:

① 基本计时和显示功能(24小时制显示),即时,分,秒的正常显示模式。包括:

1. 24小时制显示

2. 动态扫描显示;

3. 显示格式:88-88-88

② 能调整设置当前时间(含时、分),即设计两个按键,按动校时键,时计数器加一,按动校分键,则电路处于校分状态。

③ 整点报时,要求整点的倒计时5秒时,闪烁LED来报时

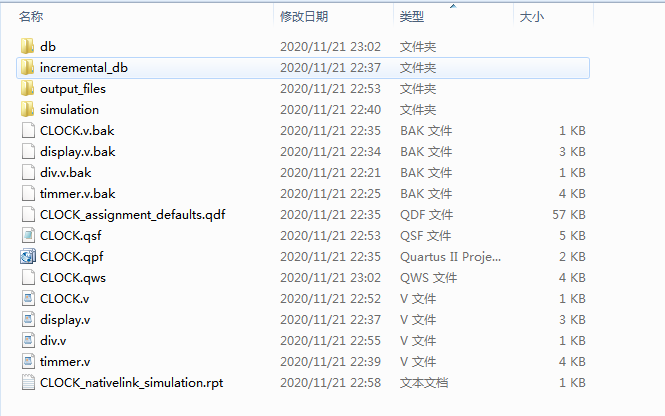

1. 工程文件

2. 程序文件

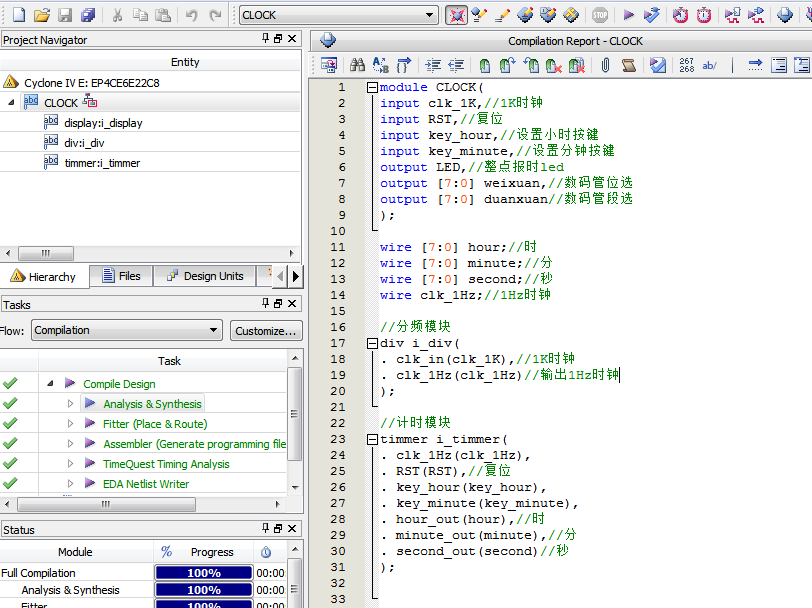

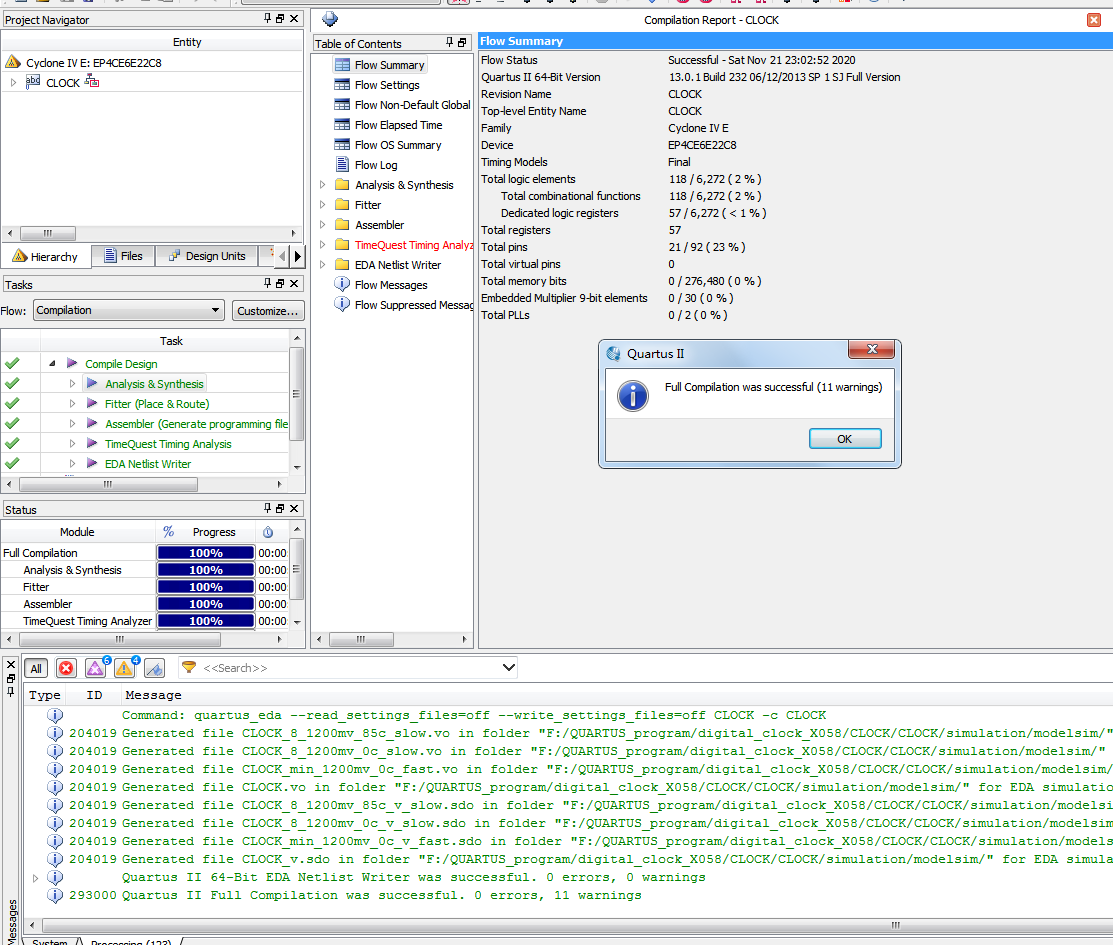

3. 程序编译

4. RTL图

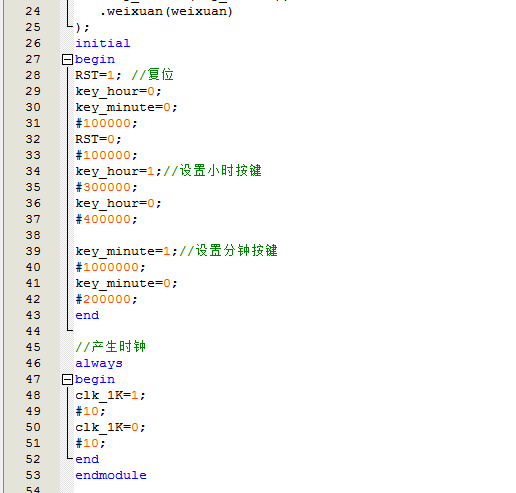

5. Testbench

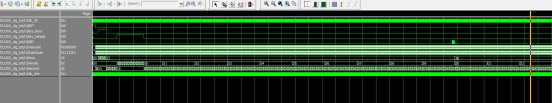

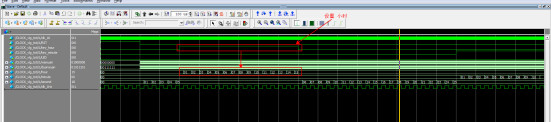

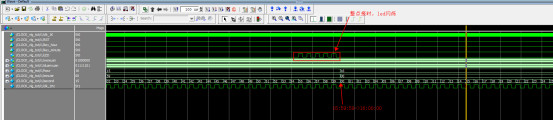

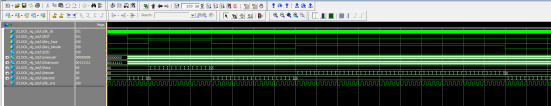

6. 仿真图

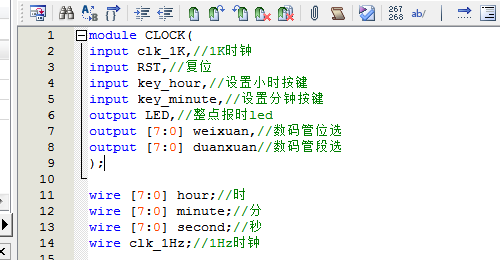

部分代码展示:

module CLOCK( input clk_1K,//1K时钟 input RST,//复位 input key_hour,//设置小时按键 input key_minute,//设置分钟按键 output LED,//整点报时led output [7:0] weixuan,//数码管位选 output [7:0] duanxuan//数码管段选 ); wire [7:0] hour;//时 wire [7:0] minute;//分 wire [7:0] second;//秒 wire clk_1Hz;//1Hz时钟 //分频模块 div i_div( . clk_in(clk_1K),//1K时钟 . clk_1Hz(clk_1Hz)//输出1Hz时钟 ); //计时模块 timmer i_timmer( . clk_1Hz(clk_1Hz), . RST(RST),//复位 . key_hour(key_hour), . key_minute(key_minute), . hour_out(hour),//时 . minute_out(minute),//分 . second_out(second)//秒 ); //数码管显示模块 display i_display( . clk_1K(clk_1K),// . clk_1Hz(clk_1Hz), . RST(RST),//复位 . LED(LED), . hour(hour),//时 . minute(minute),//分 . second(second),//秒 . weixuan(weixuan),//数码管位选 . duanxuan(duanxuan)//数码管段选 ); endmodule

源代码

扫描文章末尾的公众号二维码

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/不正经/article/detail/721975

推荐阅读

相关标签