- 1ubuntu-14.04.5-server安装及配置android编译服务器实录_ubuntu14 server android

- 2凡尔码安全巡检卡替代传统纸质记录卡

- 3【Backbone】Vim(Vision Mamba)架构学习笔记_vim mamba

- 4上下双相机引导定位,下相机怎么标定?_上下相机定位贴合

- 5c++ eos智能合约开发_EOS智能合约开发为何编译成WebAssembly?

- 6最详细的 K8S 学习笔记总结

- 7Flutter 视频详情头部模块组件封装与布局技巧_flutter 布局header

- 8linux终端信息输出到文件_linux 将终端内容显示在文件

- 9电机控制之FOC_克拉克变换

- 10java实验(头歌)--面向对象封装继承和多态_java面向对象封装继承和多态头歌

FPGA调用 Video Mixer IP 实现多路视频拼接,提供4套工程源码和技术支持

赞

踩

1.前言

Video Mixer IP是OSD的升级版,vivado2019.1后OSD已不再使用,Video Mixer IP主要功能就是实现视频叠加输出,最多可叠加16路视频,但现实项目几乎用不到这么多路。本设计调用Xilinx主推的VDMA做图像缓存,调用Video Mixer IP做视频拼接,提供4套vivado工程,分别为1路视频直接输出,2路视频拼接,3路视频拼接,4路视频拼接,旨在让大家掌握Video Mixer IP的用法,包括IP配置,SDK配置等;

本文详细描述了设计方案,工程代码编译通过后上板调试验证,可直接项目移植,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字成像和图像传输领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

2.我这儿已有的多路视频拼接方案

多路视频拼接是FPGA图像处理的基本操作,项目中应用广泛,目前我这儿已有的多路视频拼接方案有如下几种:

2.1 输入VGA时序视频拼接

输入视频时序为VGA时序,视频缓存在DDR的不同地址后输出,从而实现视频拼接,这种方案的优点是输入视频时序为VGA,不需要时序转换,适合不喜欢用AXI4-Stream时序的老玩家,由于输入入视频时序为VGA,所以也不需要调用Xilinx主推的VDMA等一大堆IP,更不需要SDK配置,无论是FPGA的移植性还是适应性还是资源消耗都更为友好,这个实现方式我之前专门出过一篇博客,感兴趣的可以点击链接去参考:点击直接前往博客

2.2 输入AXI4-Stream时序视频拼接

本方案,本方案调用Xilinx主推的VDMA做图像缓存,调用Video Mixer IP做视频拼接,所以输入视频时序必须为AXI4-Stream,如果你的输入视频时序为VGA,则需要调用Xilinx的IP转为AXI4-Stream时序,且需要运行SDK软件配置IP才能使用,用起来相对麻烦,但有点是基于AXI4-Stream的视频流适合大批量数据传输,使用上更加简单,你无需关心底层逻辑如何实现的,只需要知道如何用SDK配置即可;

2.3 输入VGA时序视频缩放后拼接

输入视频时序为VGA时序,视频经过纯verilog编写的图像缩放模块对视频进行任意尺寸的缩放,达到你的要求后再将视频缓存在DDR的不同地址后输出,从而实现视频拼接,这种方案的优点是输入视频可以进行缩放操作,因为视频拼接往往伴随着视频缩放,这样更为接近真实的项目需求,且图像缩放模块支持任意比例、任意尺寸的缩放,使得你的拼接变得更具有私人定制的属性,时序为VGA,不需要时序转换,适合不喜欢用AXI4-Stream时序的老玩家,由于输入入视频时序为VGA,所以也不需要调用Xilinx主推的VDMA等一大堆IP,更不需要SDK配置,无论是FPGA的移植性还是适应性还是资源消耗都更为友好,这个实现方式我之前专门出过一篇博客,感兴趣的可以点击链接去参考:点击直接前往博客

2.4 输入AXI4-Stream时序视频缩放后拼接

本方案输入视频时序为AXI4-Stream时序,经过输入时序同样为AXI4-Stream的图像缩放模块对视频进行任意尺寸的缩放,再调用Xilinx主推的VDMA做图像缓存,调用Video Mixer IP做视频拼接,这种方案的优点是输入视频可以进行缩放操作,因为视频拼接往往伴随着视频缩放,这样更为接近真实的项目需求,且图像缩放模块支持任意比例、任意尺寸的缩放,使得你的拼接变得更具有私人定制的属性,要求输入视频时序必须为AXI4-Stream,如果你的输入视频时序为VGA,则需要调用Xilinx的IP转为AXI4-Stream时序,且需要运行SDK软件配置IP才能使用,用起来相对麻烦,但有点是基于AXI4-Stream的视频流适合大批量数据传输,使用上更加简单,你无需关心底层逻辑如何实现的,只需要知道如何用SDK配置即可;这个实现方式我之前专门出过一篇博客,感兴趣的可以点击链接去参考:点击直接前往博客

2.5 输入4路 PAL 视频拼接输出

这个方案就是具体的现实项目了,输入视频为4路PAL制式的隔行扫描视频,经过视频去隔行后缓存DDR再4路拼接输出,这个实现方式我之前专门出过两篇博客,感兴趣的可以点击链接去参考:点击直接前往博客

点击直接前往博客

2.6 输入4路 SDI 视频拼接输出

这个方案就是具体的现实项目了,输入视频为4路SDI 制式的隔行扫描视频,经过SDI解串、解码、时序恢复后缓存DDR再4路拼接输出,这个实现方式我之前专门出过一篇博客,感兴趣的可以点击链接去参考:点击直接前往博客

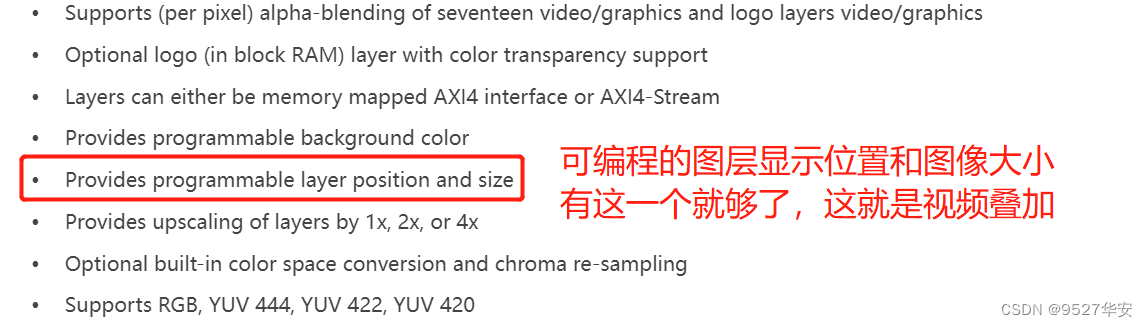

3.Video Mixer IP官方数据手册解读

官方手册是PG243,链接点这里PG243

这是干货文章,所以我们只看手册的重点:

这里还有个图像放大功能,但不能缩小,感觉很鸡肋,可以不管他

数据手的核心内容我直接翻译成图片如下:

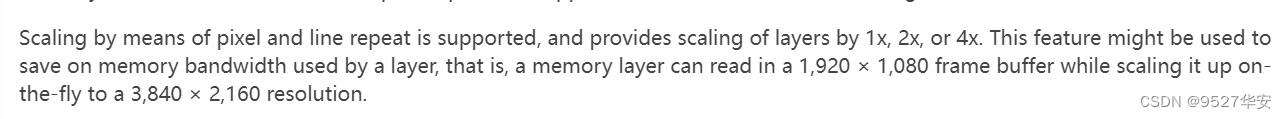

Master Layer:底层,是视频叠加的最底层,不能编程,只能指定大小;

Layer0–>Layer16:叠加图层,也就是输入视频,叠加在底层之上,大小和位置可通过SDK编程控制。

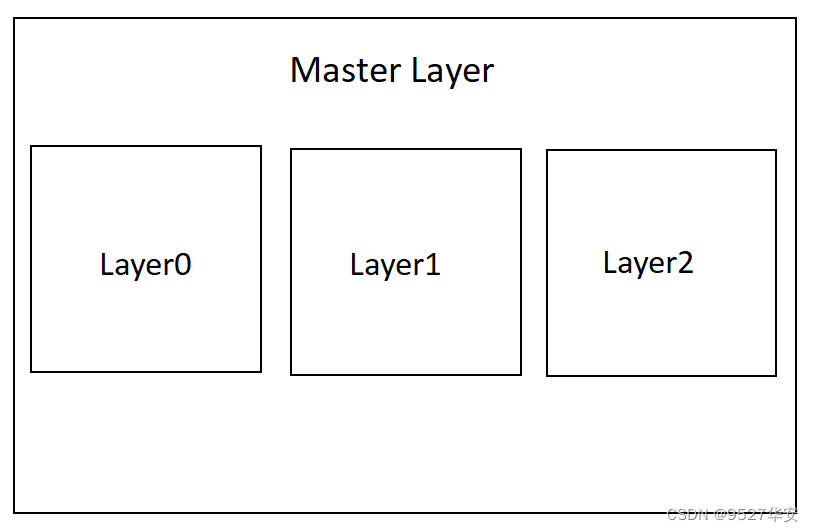

4.Video Mixer IP寄存器配置和UI配置

BD配置如下:

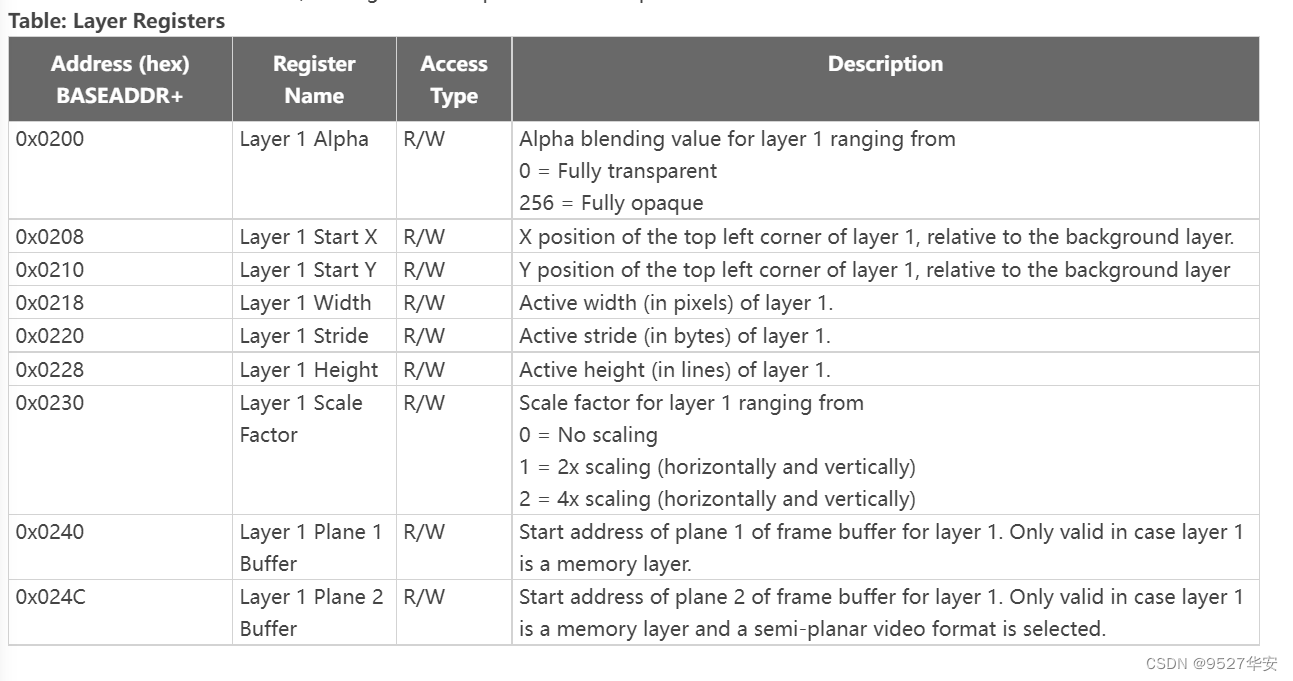

寄存器配置说明如下:具体配置看SDK代码,工程源码和SDK配置C代码的获取方式在文章末尾,请耐心看到最后;

5.工程1:一路视频叠加输出

开发板FPGA型号:Xilinx Kintex7-xc7k325tffg676-2;

开发环境:vivado2019.1;

输入:OV5640摄像头,分辨率1280X720@60Hz;

输出:HDMI 1080P叠加一路720P视频输出;

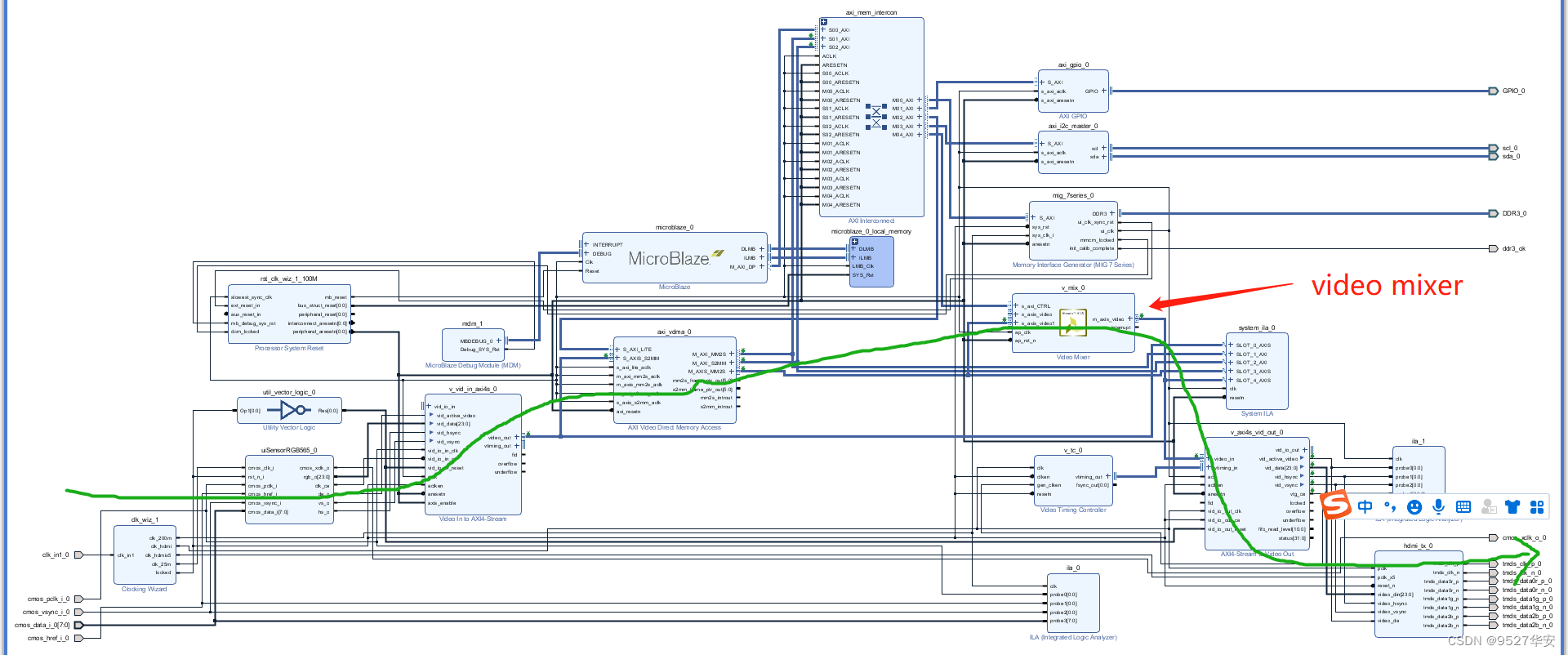

Vivado Block Design工程如图:

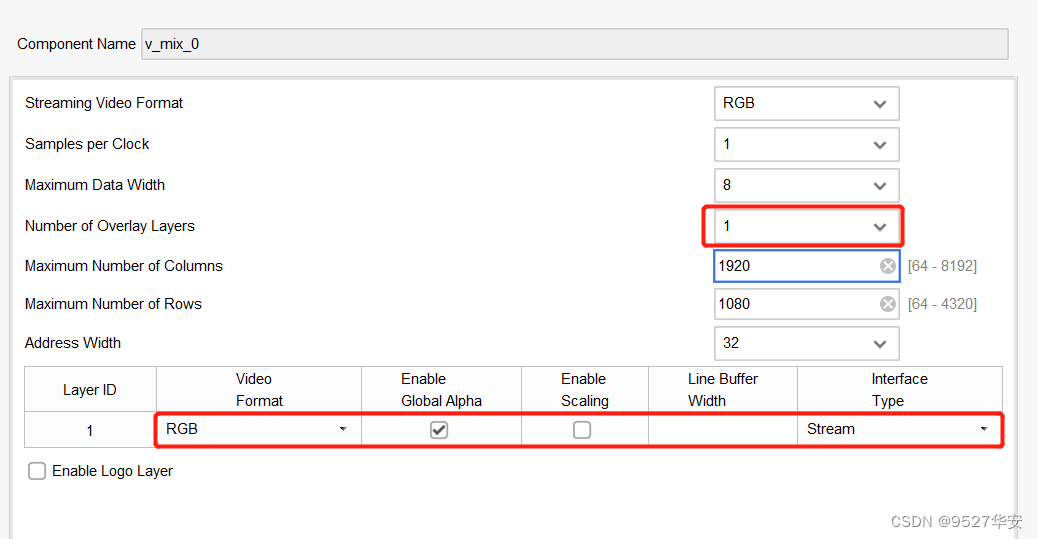

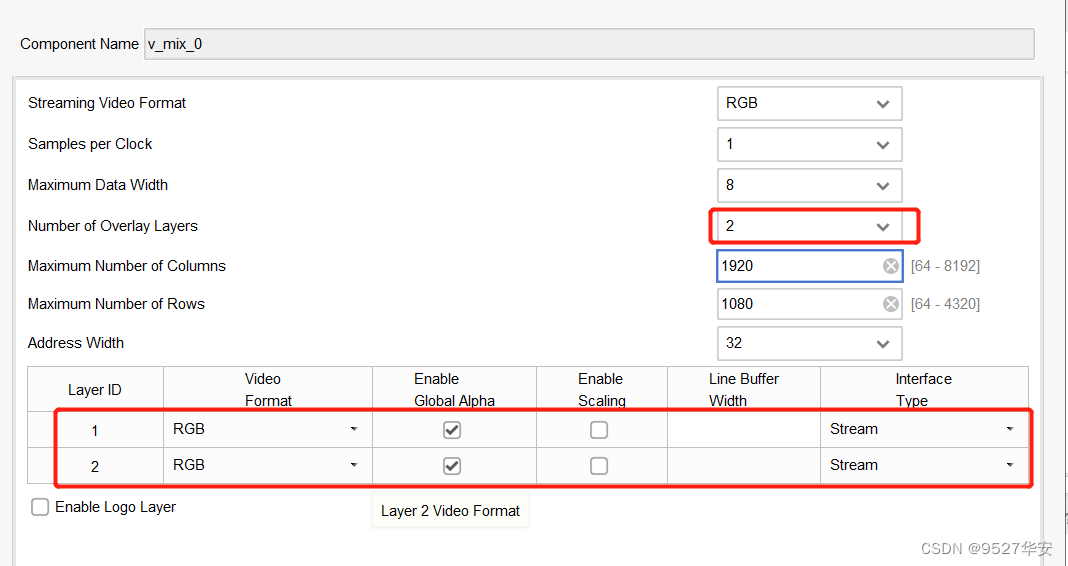

mixer配置如下:

输出如下:

6.工程2:两路视频叠加输出

开发板FPGA型号:Xilinx Kintex7-xc7k325tffg676-2;

开发环境:vivado2019.1;

输入:OV5640摄像头,分辨率1280X720@60Hz;

输出:HDMI 1080P叠加2路960X540视频输出;

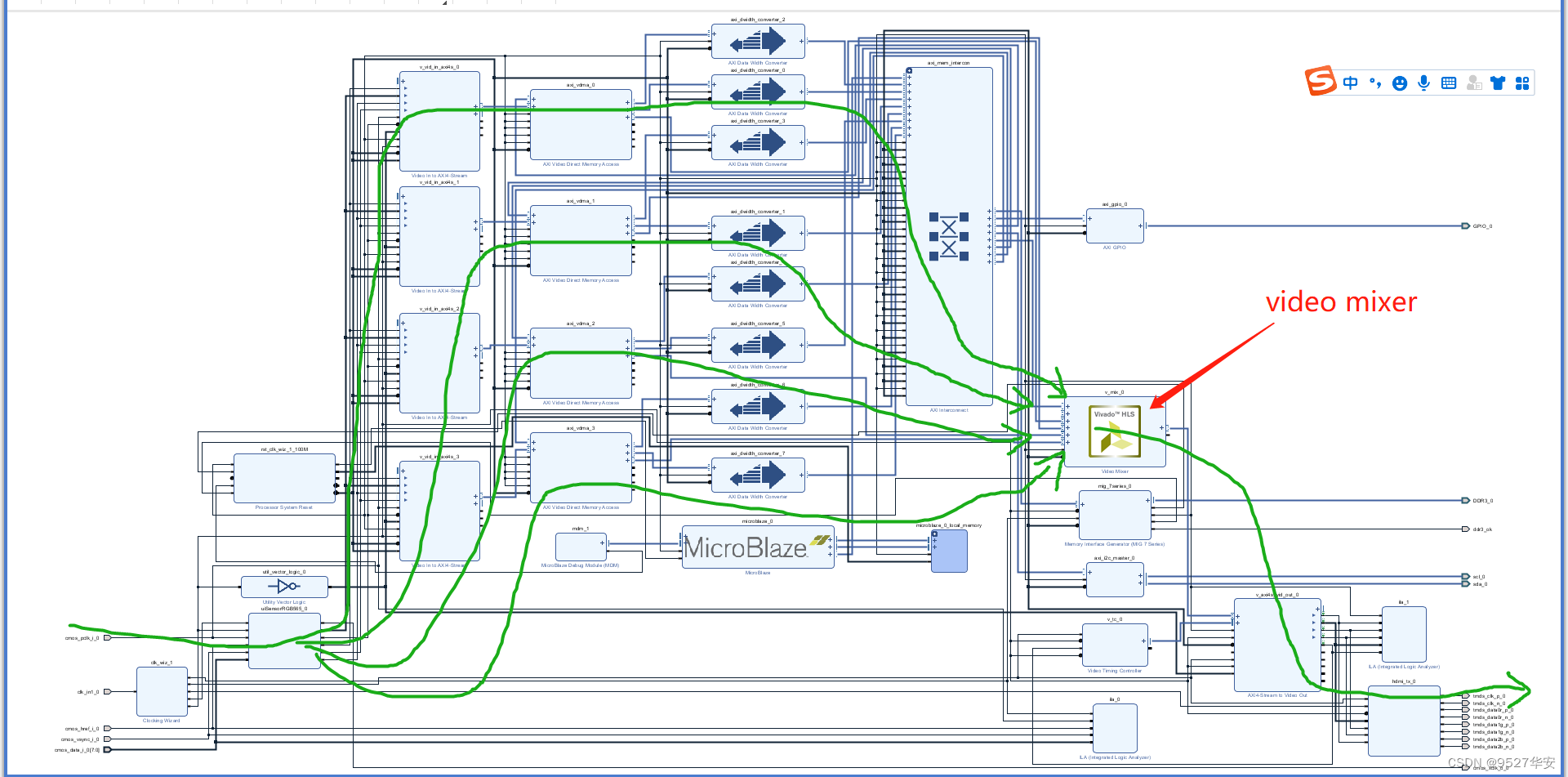

Vivado Block Design工程如图:

mixer配置如下:

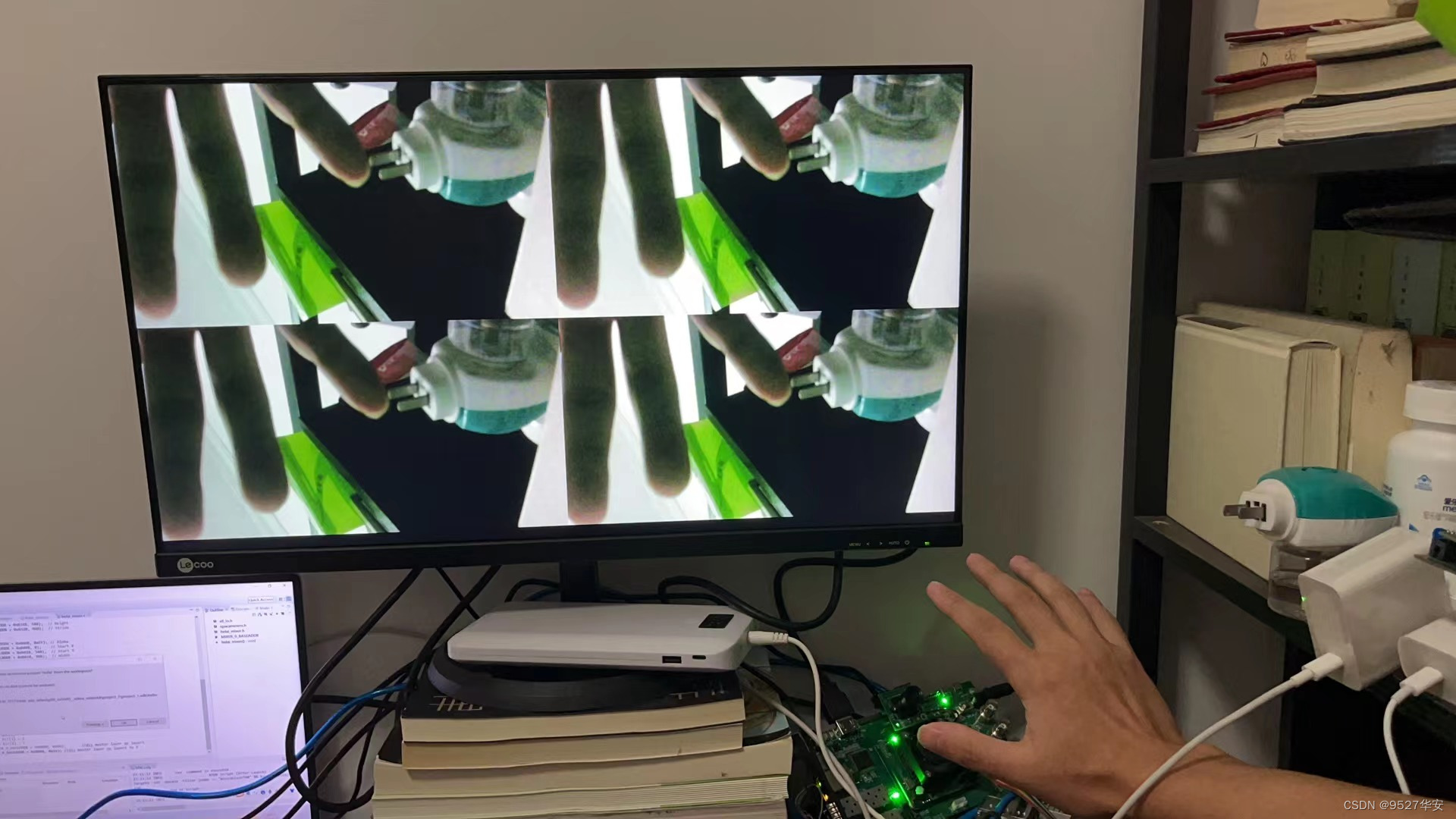

输出如下:

7.工程3:四路视频叠加输出

开发板FPGA型号:Xilinx Kintex7-xc7k325tffg676-2;

开发环境:vivado2019.1;

输入:OV5640摄像头,分辨率1280X720@60Hz;

输出:HDMI 1080P叠加4路960X540视频输出;

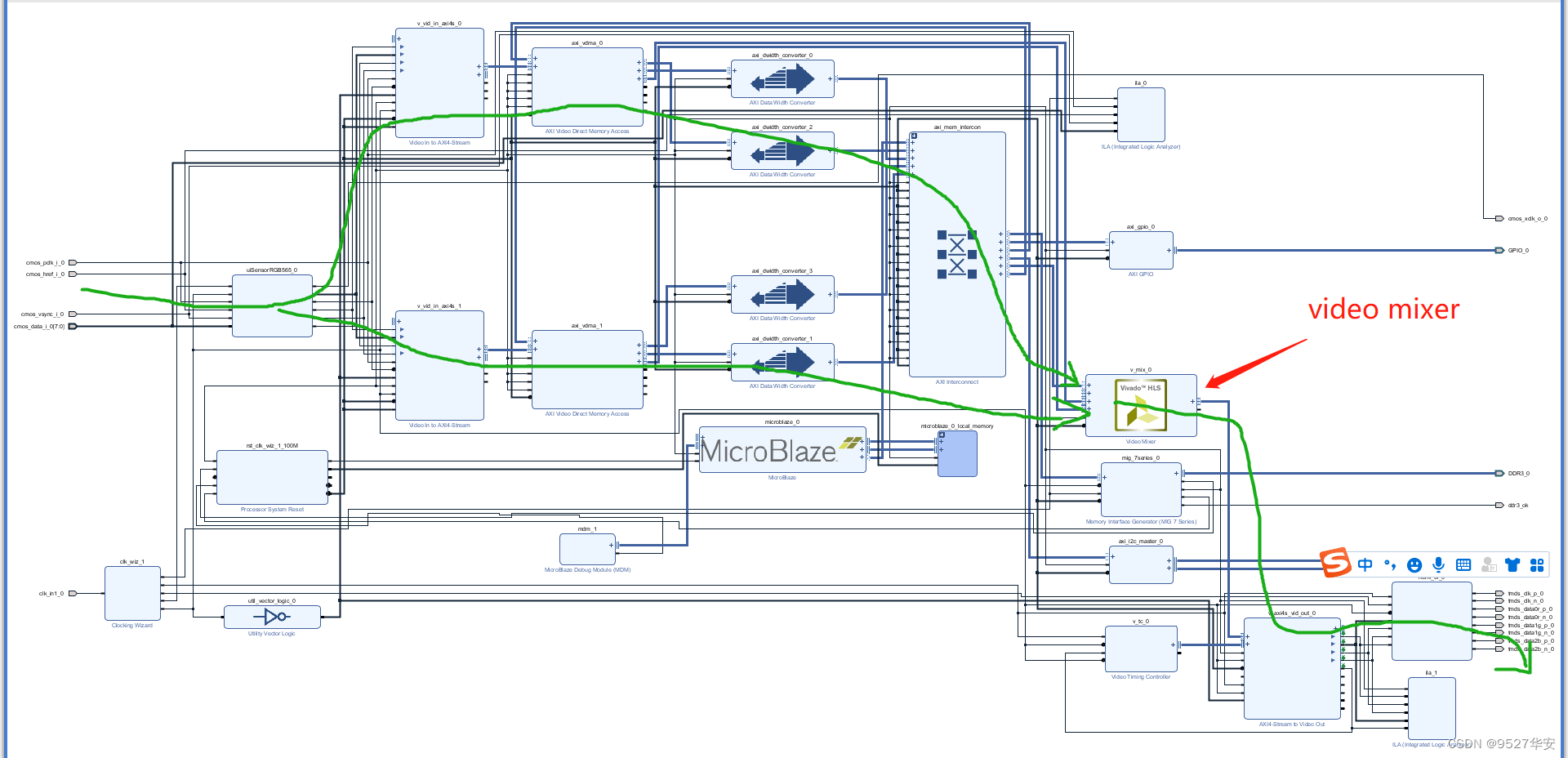

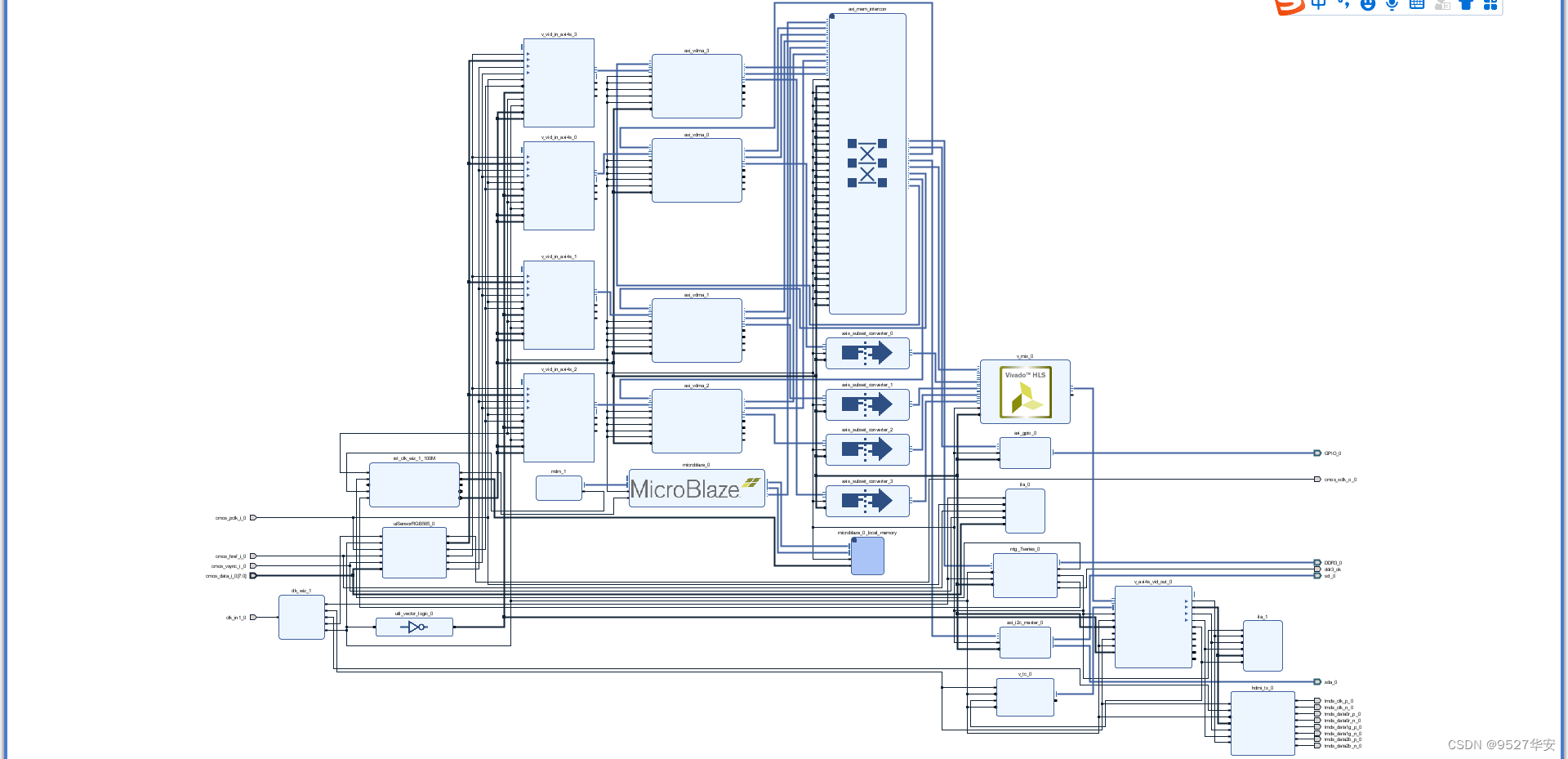

Vivado Block Design工程如图:

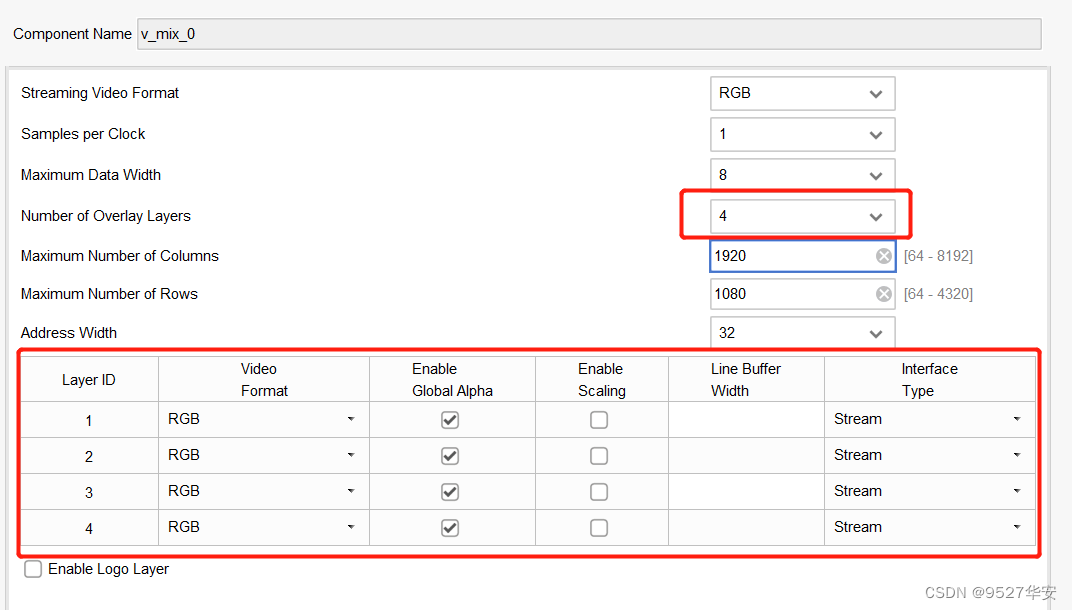

mixer配置如下:

输出如下:

8.工程4:四路视频叠加优化输出

开发板FPGA型号:Xilinx Kintex7-xc7k325tffg676-2;

开发环境:vivado2019.1;

输入:OV5640摄像头,分辨率1280X720@60Hz;

输出:HDMI 1080P叠加4路960X540视频输出;

优化:去掉了AXI data width converter,如下:

替换成AIX4-Stream Subset Converter,如下:

优化的效果是降低了资源消耗,优化后的Vivado Block Design工程如图:

9.福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务: