热门标签

热门文章

- 1码农小汪-设计模式-迭代器模式_迭代器模式在spring中的应用

- 2一文读懂前端缓存

- 3fatal error: zlib.h: No such file or directory #include <zlib.h>

- 4Hive 常用函数_hive lpad

- 5在 Docker 环境下安装 OpenWrt_docker安装openwrt

- 6从几种常见的分辨率谈起_1024*600分辨率是多少p

- 7selenium配置chrome浏览器的选项_default_content_setting_values

- 8【git使用】清空本地仓库与远程仓库_git如何本地删除master以外的其它分支

- 9[Simulink] 基于模型的测试与验证学习笔记_Step 3: Detecting Desig Errors_simulink design verifier

- 10基于STM32和阿里云的智能台灯(STM32+ESP8266+MQTT+阿里云+语音模块)

当前位置: article > 正文

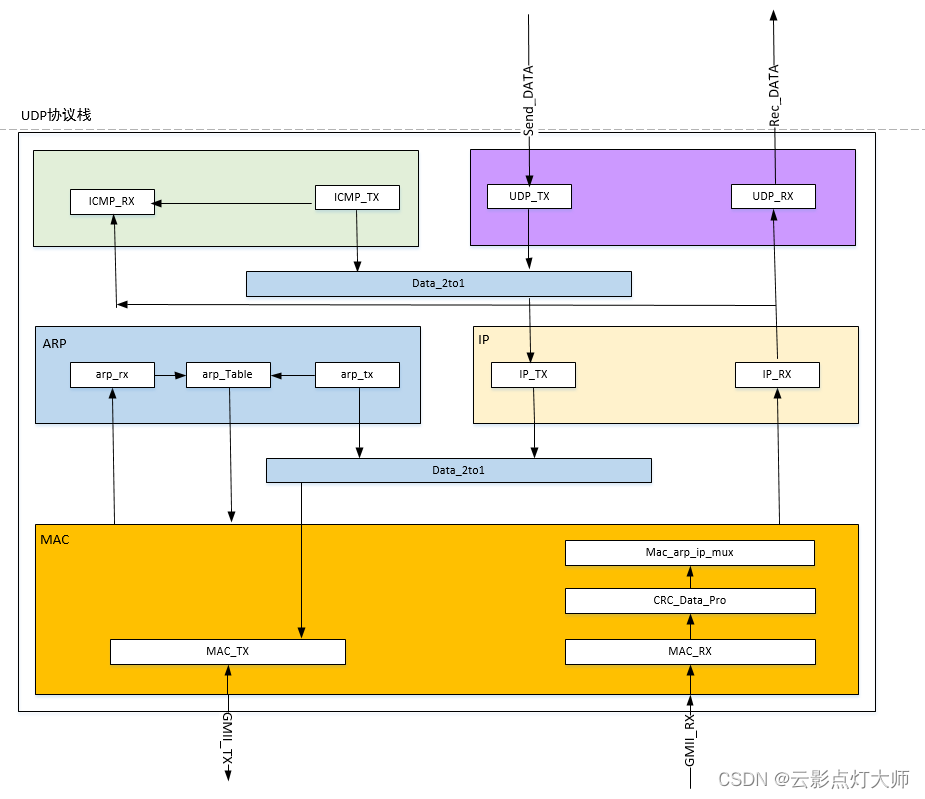

FPGA——三速自适应以太网设计(1)基本模块_fpga以太网模块设计

作者:笔触狂放9 | 2024-05-11 14:24:54

赞

踩

fpga以太网模块设计

FPGA——以太网设计(1)基本模块

1. 协议解析

每层都嵌套在上层的数据字段

(1)MAC层

以太网帧长: 64B~1518B

(2)IP层 和 ARP层

IP层

ARP层

(3)UDP层 和 ICMP层

UDP层

ICMP层

2.1 MAC接收模块

module MAC_rx#( parameter P_TARTGET_MAC = {8'h00,8'h00,8'h00,8'h00,8'h00,8'h00}, P_SOURCE_MAC = {8'h00,8'h00,8'h00,8'h00,8'h00,8'h00}, P_CRC_CHECK = 1 )( input i_clk , input i_rst , /*--------info port--------*/ input [47:0] i_target_mac , input i_target_mac_valid , input [47:0] i_source_mac , input i_source_mac_valid , /*--------data port--------*/ output [15:0] o_post_type , output [7 :0] o_post_data , output o_post_last , output o_post_valid , output [47:0] o_rec_src_mac , output o_rec_src_valid , output o_crc_error , output o_crc_valid , /*--------GMII port--------*/ input [7 :0] i_GMII_data , input i_GMII_valid ); /***************function**************/ /***************parameter*************/ /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg ro_post_last ; reg ro_post_valid ; reg [47:0] ro_rec_src_mac ; reg ro_rec_src_valid ; reg ro_crc_error ; reg [7 :0] ri_GMII_data ; reg ri_GMII_valid ; reg [7 :0] ri_GMII_data_1d ; reg ri_GMII_valid_1d ; reg [7 :0] ri_GMII_data_2d ; reg ri_GMII_valid_2d ; reg [7 :0] ri_GMII_data_3d ; reg ri_GMII_valid_3d ; reg [7 :0] ri_GMII_data_4d ; reg ri_GMII_valid_4d ; reg [7 :0] ri_GMII_data_5d ; reg ri_GMII_valid_5d ; reg [47:0] r_target_mac ; reg [47:0] r_source_mac ; reg [47:0] r_rec_mac ; reg r_rec_mac_access ; reg [15:0] r_rec_cnt ; reg r_headr_check ; reg r_header_access ; reg [15:0] r_rec_type ;//0x0800-IP 0X0806-ARP reg r_crc_rst ; reg r_crc_en ; reg r_crc_en_1d ; reg [15:0] r_rec_5d_cnt ; reg [31:0] r_crc_result ; reg ro_crc_valid ; /***************wire******************/ wire [31:0] w_crc_result ; /***************component*************/ CRC32_D8 CRC32_D8_u0( .i_clk (i_clk ), .i_rst (r_crc_rst ), .i_en (r_crc_en ), .i_data (ri_GMII_data_5d ), .o_crc (w_crc_result ) ); /***************assign****************/ assign o_post_type = r_rec_type ; assign o_post_data = ri_GMII_data_5d ; assign o_post_last = ro_post_last ; assign o_post_valid = ro_post_valid ; assign o_rec_src_mac = ro_rec_src_mac ; assign o_rec_src_valid = ro_rec_src_valid ; assign o_crc_error = ro_crc_error ; assign o_crc_valid = ro_crc_valid ; /***************always****************/ //数据打5拍,为了对齐信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_GMII_data <= 'd0; ri_GMII_valid <= 'd0; ri_GMII_data_1d <= 'd0; ri_GMII_valid_1d <= 'd0; ri_GMII_data_2d <= 'd0; ri_GMII_valid_2d <= 'd0; ri_GMII_data_3d <= 'd0; ri_GMII_valid_3d <= 'd0; ri_GMII_data_4d <= 'd0; ri_GMII_valid_4d <= 'd0; end else begin ri_GMII_data <= i_GMII_data ; ri_GMII_valid <= i_GMII_valid; ri_GMII_data_1d <= ri_GMII_data ; ri_GMII_valid_1d <= ri_GMII_valid; ri_GMII_data_2d <= ri_GMII_data_1d ; ri_GMII_valid_2d <= ri_GMII_valid_1d; ri_GMII_data_3d <= ri_GMII_data_2d ; ri_GMII_valid_3d <= ri_GMII_valid_2d; ri_GMII_data_4d <= ri_GMII_data_3d ; ri_GMII_valid_4d <= ri_GMII_valid_3d; ri_GMII_data_5d <= ri_GMII_data_4d ; ri_GMII_valid_5d <= ri_GMII_valid_4d; end end //valid后,输入目标mac地址锁存 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_target_mac <= P_TARTGET_MAC; else if(i_target_mac_valid) r_target_mac <= i_target_mac; else r_target_mac <= r_target_mac; end //valid后,输入源mac地址锁存 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_source_mac <= P_SOURCE_MAC ; else if(i_source_mac_valid) r_source_mac <= i_source_mac; else r_source_mac <= r_source_mac; end //GMII接口输入有效 // r_rec_cnt 为 6 停一个周期 接收SFD // 继续 + 1 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_rec_cnt <= 'd0; else if(ri_GMII_valid && r_rec_cnt == 6 && ri_GMII_data == 8'h55) r_rec_cnt <= r_rec_cnt; else if(ri_GMII_valid) r_rec_cnt <= r_rec_cnt + 1; else r_rec_cnt <= 'd0; end // r_rec_cnt 7 ~ 12 存好收到目的的MAC地址 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_rec_mac <= 'd0; else if(ri_GMII_valid && r_rec_cnt >= 7 && r_rec_cnt <= 12) r_rec_mac <= {r_rec_mac[39:0],ri_GMII_data}; else r_rec_mac <= r_rec_mac; end // r_rec_cnt 13 检测收到目的mac与自身mac是否相等 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_rec_mac_access <= 'd0; else if(r_rec_cnt == 13 && r_rec_mac != r_source_mac) r_rec_mac_access <= 'd0; else if(r_rec_cnt == 13 && (r_rec_mac == r_source_mac || &r_rec_mac)) r_rec_mac_access <= 'd1; else r_rec_mac_access <= r_rec_mac_access; end //r_rec_cnt 0~6 检验前导码 是否为55 再6 检测SFD 是否为D5 always@(*) begin case(r_rec_cnt) 0,1,2,3,4,5 :r_headr_check <= ri_GMII_data == 8'h55 ? 'd1 : 'd0; 6 :r_headr_check <= ri_GMII_data == 8'hD5 || ri_GMII_data == 8'h55 ? 'd1 : 'd0; default :r_headr_check <= 'd1; endcase end //头没有问题,就通过信号不拉低 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_header_access <= 'd1; else if(!ri_GMII_valid) r_header_access <= 'd1; else if(ri_GMII_valid && r_rec_cnt >= 0 && r_rec_cnt <= 6 && !r_headr_check) r_header_access <= 'd0; else r_header_access <= r_header_access; end // r_rec_cnt 13~ 18 源MAC地址接收 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_rec_src_mac <= 'd0; else if(ri_GMII_valid && r_rec_cnt >= 13 && r_rec_cnt <= 18) ro_rec_src_mac <= {ro_rec_src_mac[39:0],ri_GMII_data}; else ro_rec_src_mac <= ro_rec_src_mac; end // r_rec_cnt 19 源MAC地址接收有效 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_rec_src_valid <= 'd0; else if(r_rec_cnt == 19) ro_rec_src_valid <= 'd1; else ro_rec_src_valid <= ro_rec_src_valid; end //r_rec_cnt 19 ~ 20 接收类型 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_rec_type <= 'd0; else if(ri_GMII_valid && r_rec_cnt >= 19 && r_rec_cnt <= 20) r_rec_type <= {r_rec_type[7:0],ri_GMII_data}; else r_rec_type <= r_rec_type; end //延迟5个周期的 GMII 有效 r_rec_5d_cnt + 1 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_rec_5d_cnt <= 'd0; else if(ri_GMII_valid_5d) r_rec_5d_cnt <= r_rec_5d_cnt + 1; else r_rec_5d_cnt <= 'd0; end //正常信号的下降沿 有效为0 //延迟5个周期 计数为 21 有效为1 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_post_valid <= 'd0; else if(ro_post_last) ro_post_valid <= 'd0; else if(r_rec_5d_cnt == 21) ro_post_valid <= 'd1; else ro_post_valid <= ro_post_valid; end //GMII有效信号下降沿 输出 ro_post_last always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_post_last <= 'd0; else if(!i_GMII_valid && ri_GMII_valid) ro_post_last <= 'd1; else ro_post_last <= 'd0; end // always@(posedge i_clk,posedge i_rst) // begin // if(i_rst) // ro_arp_valid <= 'd0; // else if(!ri_GMII_valid && ri_GMII_data_1d) // ro_arp_valid <= 'd0; // else if(r_rec_type == 16'h0806 && r_rec_5d_cnt == 20) // ro_arp_valid <= 'd1; // else // ro_arp_valid <= ro_ip_valid; // end // always@(posedge i_clk,posedge i_rst) // begin // if(i_rst) // ro_arp_last <= 'd0; // else if(!i_GMII_valid && ri_GMII_valid && r_rec_type == 16'h0806) // ro_arp_last <= 'd1; // else // ro_arp_last <= 'd0; // end //CRC使能信号 来 CRC模块数据复位信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_crc_rst <= 'd1; else if(r_rec_5d_cnt == 7) r_crc_rst <= 'd0; else if(!r_crc_en && r_crc_en_1d) r_crc_rst <= 'd1; else r_crc_rst <= r_crc_rst; end // GMII有效的下降沿 关闭crc校验使能 // always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_crc_en <= 'd0; else if(!ri_GMII_valid && ri_GMII_data_1d) r_crc_en <= 'd0; else if(r_rec_5d_cnt == 7) r_crc_en <= 'd1; else r_crc_en <= r_crc_en; end //CRC使能信号打拍 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_crc_en_1d <= 'd0; else r_crc_en_1d <= r_crc_en; end //获取外部输入的CRC结果 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_crc_result <= 'd0; else if(ri_GMII_valid) r_crc_result <= {ri_GMII_data,r_crc_result[31:8]}; else r_crc_result <= r_crc_result; end //CRC使能下降沿 CRC有效 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_crc_valid <= 'd0; else if(!r_crc_en && r_crc_en_1d) ro_crc_valid <= 'd1; else ro_crc_valid <= 'd0; end //CRC校验 error always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_crc_error <= 'd0; else if(!P_CRC_CHECK) ro_crc_error <= 'd0; else if(!r_crc_en && r_crc_en_1d && r_crc_result != w_crc_result) ro_crc_error <= 'd1; else ro_crc_error <= 'd0; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

- 175

- 176

- 177

- 178

- 179

- 180

- 181

- 182

- 183

- 184

- 185

- 186

- 187

- 188

- 189

- 190

- 191

- 192

- 193

- 194

- 195

- 196

- 197

- 198

- 199

- 200

- 201

- 202

- 203

- 204

- 205

- 206

- 207

- 208

- 209

- 210

- 211

- 212

- 213

- 214

- 215

- 216

- 217

- 218

- 219

- 220

- 221

- 222

- 223

- 224

- 225

- 226

- 227

- 228

- 229

- 230

- 231

- 232

- 233

- 234

- 235

- 236

- 237

- 238

- 239

- 240

- 241

- 242

- 243

- 244

- 245

- 246

- 247

- 248

- 249

- 250

- 251

- 252

- 253

- 254

- 255

- 256

- 257

- 258

- 259

- 260

- 261

- 262

- 263

- 264

- 265

- 266

- 267

- 268

- 269

- 270

- 271

- 272

- 273

- 274

- 275

- 276

- 277

- 278

- 279

- 280

- 281

- 282

- 283

- 284

- 285

- 286

- 287

- 288

- 289

- 290

- 291

- 292

- 293

- 294

- 295

- 296

- 297

- 298

- 299

- 300

- 301

- 302

- 303

- 304

- 305

- 306

- 307

- 308

- 309

- 310

- 311

- 312

- 313

- 314

- 315

- 316

- 317

- 318

- 319

- 320

- 321

- 322

- 323

- 324

- 325

- 326

- 327

- 328

- 329

- 330

- 331

- 332

- 333

- 334

- 335

- 336

- 337

- 338

- 339

- 340

- 341

- 342

- 343

- 344

- 345

- 346

- 347

- 348

- 349

- 350

- 351

- 352

- 353

- 354

- 355

- 356

- 357

- 358

- 359

- 360

- 361

- 362

- 363

- 364

- 365

- 366

- 367

2.2 MAC发送模块

module MAC_tx#( parameter P_TARTGET_MAC = {8'h00,8'h00,8'h00,8'h00,8'h00,8'h00}, P_SOURCE_MAC = {8'h00,8'h00,8'h00,8'h00,8'h00,8'h00}, P_CRC_CHECK = 1 )( input i_clk , input i_rst , /*--------info port--------*/ input [47:0] i_target_mac , input i_target_mac_valid , input [47:0] i_source_mac , input i_source_mac_valid , /*--------data port--------*/ input i_udp_valid , output o_udp_ready , input [15:0] i_send_type , input [15:0] i_send_len , input [7 :0] i_send_data , input i_send_last , input i_send_valid , /*--------GMII port--------*/ output [7 :0] o_GMII_data , output o_GMII_valid ); /***************function**************/ /***************parameter*************/ /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg [15:0] ri_send_type ; reg [15:0] ri_send_len ; reg [7 :0] ri_send_data ; reg ri_send_valid ; reg ri_send_valid_1d ; reg [7 :0] ro_GMII_data ; reg ro_GMII_valid ; reg ro_GMII_valid_1d ; reg [47:0] r_target_mac ; reg [47:0] r_source_mac ; reg r_fifo_mac_rd_en ; reg [15:0] r_mac_pkg_cnt ; reg [7 :0] r_mac_data ; reg r_mac_data_valid ; reg r_mac_data_valid_1d ; reg [15:0] r_mac_data_cnt ; reg r_crc_rst ; reg r_crc_en ; reg [1 :0] r_crc_out_cnt ; reg r_crc_out_cnt_1d ; reg [15:0] r_gap_lat ; reg r_gap_lock ; reg [15:0] r_gap_cnt ; reg ri_udp_valid ; reg ro_udp_ready ; /***************wire******************/ wire [7 :0] w_fifo_mac_dout ; wire w_fifo_mac_full ; wire w_fifo_mac_empty ; wire w_send_valid_pos ; wire w_send_valid_neg ; wire [31:0] w_crc_result ; /***************component*************/ FIFO_MAC_8X64 FIFO_MAC_8X64_U0 ( .clk (i_clk ), // input wire clk .din (ri_send_data ), // input wire [7 : 0] din .wr_en (ri_send_valid ), // input wire wr_en .rd_en (r_fifo_mac_rd_en ), // input wire rd_en .dout (w_fifo_mac_dout ), // output wire [7 : 0] dout .full (w_fifo_mac_full ), // output wire full .empty (w_fifo_mac_empty ) // output wire empty ); CRC32_D8 CRC32_D8_u0( .i_clk (i_clk ), .i_rst (r_crc_rst ), .i_en (r_crc_en ), .i_data (r_mac_data ), .o_crc (w_crc_result ) ); /***************assign****************/ assign o_GMII_data = ro_GMII_data ; assign o_GMII_valid = ro_GMII_valid ; assign w_send_valid_pos = ri_send_valid & !ri_send_valid_1d; assign w_send_valid_neg = !ri_send_valid & ri_send_valid_1d; assign o_udp_ready = ro_udp_ready ; /***************always****************/ //锁存 目的mac always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_target_mac <= P_TARTGET_MAC; else if(i_target_mac_valid) r_target_mac <= i_target_mac; else r_target_mac <= r_target_mac; end //锁存 源mac always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_source_mac <= P_SOURCE_MAC ; else if(i_source_mac_valid) r_source_mac <= i_source_mac; else r_source_mac <= r_source_mac; end //锁存输入的 发送mac帧信息 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_send_type <= 'd0; ri_send_len <= 'd0; ri_send_data <= 'd0; ri_send_valid <= 'd0; end else if(i_send_valid) begin ri_send_type <= i_send_type ; ri_send_len <= i_send_len ; ri_send_data <= i_send_data ; ri_send_valid <= i_send_valid; end else begin ri_send_type <= ri_send_type ; ri_send_len <= ri_send_len ; ri_send_data <= 'd0 ; ri_send_valid <= 'd0; end end //mac帧的计数器 //CRC校验输出完成 停止 //输入信号有效上升沿开始 计数 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_mac_pkg_cnt <= 'd0; else if(r_crc_out_cnt == 3) r_mac_pkg_cnt <= 'd0; else if(w_send_valid_pos || r_mac_pkg_cnt) r_mac_pkg_cnt <= r_mac_pkg_cnt + 1; else r_mac_pkg_cnt <= r_mac_pkg_cnt; end //组mac帧 : 前导码 + SFD + 目的mac + 源mac always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_mac_data <= 'd0; else case(r_mac_pkg_cnt) 0,1,2,3,4,5,6 :r_mac_data <= 8'h55; 7 :r_mac_data <= 8'hd5; 8 :r_mac_data <= ri_send_type == 16'h0806 ? 8'hff : r_target_mac[47:40]; 9 :r_mac_data <= ri_send_type == 16'h0806 ? 8'hff : r_target_mac[39:32]; 10 :r_mac_data <= ri_send_type == 16'h0806 ? 8'hff : r_target_mac[31:24]; 11 :r_mac_data <= ri_send_type == 16'h0806 ? 8'hff : r_target_mac[23:16]; 12 :r_mac_data <= ri_send_type == 16'h0806 ? 8'hff : r_target_mac[15: 8]; 13 :r_mac_data <= ri_send_type == 16'h0806 ? 8'hff : r_target_mac[7 : 0]; 14 :r_mac_data <= r_source_mac[47:40]; 15 :r_mac_data <= r_source_mac[39:32]; 16 :r_mac_data <= r_source_mac[31:24]; 17 :r_mac_data <= r_source_mac[23:16]; 18 :r_mac_data <= r_source_mac[15: 8]; 19 :r_mac_data <= r_source_mac[7 : 0]; 20 :r_mac_data <= ri_send_type[15: 8]; 21 :r_mac_data <= ri_send_type[7 : 0]; default :r_mac_data <= w_fifo_mac_dout; endcase end //mac有效信号 // mac数据计数到值 关闭 //发送有效上升沿 开启 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_mac_data_valid <= 'd0; else if(r_mac_data_cnt == ri_send_len + 1) r_mac_data_valid <= 'd0; else if(w_send_valid_pos) r_mac_data_valid <= 'd1; else r_mac_data_valid <= r_mac_data_valid; end //mac总数计数器 //到设置长度清零 //fifo读使能 开启计数 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_mac_data_cnt <= 'd0; else if(r_mac_data_cnt == ri_send_len + 1) r_mac_data_cnt <= 'd0; else if(r_fifo_mac_rd_en | r_mac_data_cnt) r_mac_data_cnt <= r_mac_data_cnt + 1; else r_mac_data_cnt <= r_mac_data_cnt; end //mac帧的计数器 到20 开启读fifo使能 //到mac总数关闭 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_fifo_mac_rd_en <= 'd0; else if(r_mac_data_cnt == ri_send_len - 1) r_fifo_mac_rd_en <= 'd0; else if(r_mac_pkg_cnt == 20) r_fifo_mac_rd_en <= 'd1; else r_fifo_mac_rd_en <= r_fifo_mac_rd_en; end //CRC校验复位 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_crc_rst <= 'd1; else if(r_mac_pkg_cnt == 8 ) r_crc_rst <= 'd0; else if(r_crc_out_cnt == 3) r_crc_rst <= 'd1; else r_crc_rst <= r_crc_rst; end //CRC校验使能,mac帧计时器为 8时 开启 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_crc_en <= 'd0; else if(r_mac_data_cnt == ri_send_len + 1) r_crc_en <= 'd0; else if(r_mac_pkg_cnt == 8 ) r_crc_en <= 'd1; else r_crc_en <= r_crc_en; end // r_crc_out_cnt 数据有效下降沿开启计数 等于3清零 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_crc_out_cnt <= 'd0; else if(r_crc_out_cnt == 3) r_crc_out_cnt <= 'd0; else if((!r_mac_data_valid && r_mac_data_valid_1d) || r_crc_out_cnt) r_crc_out_cnt <= r_crc_out_cnt + 1; else r_crc_out_cnt <= r_crc_out_cnt; end //输出mac帧数据 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_GMII_data <= 'd0; else if(r_mac_data_valid) ro_GMII_data <= r_mac_data; else case(r_crc_out_cnt) 0 :ro_GMII_data <= w_crc_result[7 : 0]; 1 :ro_GMII_data <= w_crc_result[15: 8]; 2 :ro_GMII_data <= w_crc_result[23:16]; 3 :ro_GMII_data <= w_crc_result[31:24]; default :ro_GMII_data <= 'd0; endcase end // r_crc_out_cnt_1d always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_crc_out_cnt_1d <= 'd0; else if(r_crc_out_cnt == 3) r_crc_out_cnt_1d <= 'd1; else r_crc_out_cnt_1d <= 'd0; end //数据有效的时候 GMII输出有效 //只有在CRC结束,r_crc_out_cnt_1d 拉高的时候,GMII输出无效 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_GMII_valid <= 'd0; else if(r_crc_out_cnt_1d) ro_GMII_valid <= 'd0; else if(r_mac_data_valid) ro_GMII_valid <= 'd1; else ro_GMII_valid <= ro_GMII_valid; end //信号打拍 获得上升沿 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_send_valid_1d <= 'd0; r_mac_data_valid_1d <= 'd0; end else begin ri_send_valid_1d <= ri_send_valid ; r_mac_data_valid_1d <= r_mac_data_valid; end end /*-------------------UDP------------------------*/ always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_udp_valid <= 'd0 ; ro_GMII_valid_1d <= 'd0; end else begin ri_udp_valid <= i_udp_valid; ro_GMII_valid_1d <= ro_GMII_valid; end end always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_udp_ready <= 'd1; else if(i_udp_valid) ro_udp_ready <= 'd0; else if( r_mac_data_cnt == ri_send_len - 1) ro_udp_ready <= 'd1; else ro_udp_ready <= ro_udp_ready; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

- 175

- 176

- 177

- 178

- 179

- 180

- 181

- 182

- 183

- 184

- 185

- 186

- 187

- 188

- 189

- 190

- 191

- 192

- 193

- 194

- 195

- 196

- 197

- 198

- 199

- 200

- 201

- 202

- 203

- 204

- 205

- 206

- 207

- 208

- 209

- 210

- 211

- 212

- 213

- 214

- 215

- 216

- 217

- 218

- 219

- 220

- 221

- 222

- 223

- 224

- 225

- 226

- 227

- 228

- 229

- 230

- 231

- 232

- 233

- 234

- 235

- 236

- 237

- 238

- 239

- 240

- 241

- 242

- 243

- 244

- 245

- 246

- 247

- 248

- 249

- 250

- 251

- 252

- 253

- 254

- 255

- 256

- 257

- 258

- 259

- 260

- 261

- 262

- 263

- 264

- 265

- 266

- 267

- 268

- 269

- 270

- 271

- 272

- 273

- 274

- 275

- 276

- 277

- 278

- 279

- 280

- 281

- 282

- 283

- 284

- 285

- 286

- 287

- 288

- 289

- 290

- 291

- 292

- 293

- 294

- 295

- 296

- 297

- 298

- 299

- 300

- 301

- 302

- 303

- 304

- 305

- 306

- 307

- 308

- 309

- 310

- 311

- 312

- 313

- 314

- 315

- 316

- 317

- 318

- 319

- 320

- 321

- 322

- 323

- 324

- 325

- 326

- 327

- 328

- 329

- 330

- 331

- 332

- 333

- 334

- 335

- 336

- 337

- 338

- 339

- 340

- 341

3.1 IP接收模块

module IP_rx#( parameter P_ST_TARGET_IP = {8'd192,8'd168,8'd1,8'd0}, parameter P_ST_SOURCE_IP = {8'd192,8'd168,8'd1,8'd1} )( input i_clk , input i_rst , /*--------info port --------*/ input [31:0] i_target_ip , input i_target_valid , input [31:0] i_source_ip , input i_source_valid , /*--------data port--------*/ output [15:0] o_udp_len , output [7 :0] o_udp_data , output o_udp_last , output o_udp_valid , output [15:0] o_icmp_len , output [7 :0] o_icmp_data , output o_icmp_last , output o_icmp_valid , output [31:0] o_source_ip , output o_source_ip_valid , /*--------mac port--------*/ input [7 :0] i_mac_data , input i_mac_last , input i_mac_valid ); /***************function**************/ /***************parameter*************/ /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg [31:0] r_target_ip ; reg [31:0] r_source_ip ; reg [7 :0] ri_mac_data ; reg [7 :0] ri_mac_data_1d ; reg ri_mac_last ; reg ri_mac_valid ; reg ri_mac_valid_1d ; reg [15:0] ro_udp_len ; reg ro_udp_last ; reg ro_udp_valid ; reg [15:0] ro_icmp_len ; reg ro_icmp_last ; reg ro_icmp_valid ; reg [15:0] r_ip_len ; reg [7 :0] r_ip_type ; reg [31:0] r_ip_source ; reg [31:0] r_ip_target ; reg [15:0] r_ip_cnt ; reg ro_source_ip_valid ; /***************wire******************/ /***************component*************/ /***************assign****************/ assign o_udp_data = ri_mac_data_1d ; assign o_icmp_data = ri_mac_data_1d ; assign o_udp_len = ro_udp_len ; assign o_udp_last = ro_udp_last ; assign o_udp_valid = ro_udp_valid ; assign o_icmp_len = ro_icmp_len ; assign o_icmp_last = ro_icmp_last ; assign o_icmp_valid = ro_icmp_valid ; assign o_source_ip = r_ip_source ; assign o_source_ip_valid = ro_source_ip_valid; /***************always****************/ //目的ip有效信号 锁存 目的ip always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_target_ip <= P_ST_TARGET_IP; else if(i_target_valid) r_target_ip <= i_target_ip; else r_target_ip <= r_target_ip; end //源ip效信号 锁存 源ip always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_source_ip <= P_ST_SOURCE_IP; else if(i_source_valid) r_source_ip <= i_source_ip; else r_source_ip <= r_source_ip; end //信号和数据打拍 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_mac_data <= 'd0; ri_mac_last <= 'd0; ri_mac_valid <= 'd0; ri_mac_data_1d <= 'd0; ri_mac_valid_1d <= 'd0; end else begin ri_mac_data <= i_mac_data ; ri_mac_last <= i_mac_last ; ri_mac_valid <= i_mac_valid; ri_mac_data_1d <= ri_mac_data; ri_mac_valid_1d <= ri_mac_valid; end end //mac端口有效 ip计数器+1 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_cnt <= 'd0; else if(ri_mac_valid) r_ip_cnt <= r_ip_cnt + 1; else r_ip_cnt <= 'd0; end // 2 3 字节数据为ip报文总长度 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_len <= 'd0; else if(r_ip_cnt >= 2 && r_ip_cnt <= 3) r_ip_len <= {r_ip_len[7:0],ri_mac_data}; else r_ip_len <= r_ip_len; end //第9字节 ip 协议类型 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_type <= 'd0; else if(r_ip_cnt == 9) r_ip_type <= ri_mac_data; else r_ip_type <= r_ip_type; end //第12 13 14 15字节 ip源地址 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_source <= 'd0; else if(r_ip_cnt >= 12 && r_ip_cnt <= 15) r_ip_source <= {r_ip_source[23:0],ri_mac_data}; else r_ip_source <= r_ip_source; end //输出ip源地址有效 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_source_ip_valid <= 'd0; else if(r_ip_cnt == 15) ro_source_ip_valid <= 'd1; else ro_source_ip_valid <= 'd0; end //第16 17 18 19字节 ip目的地址 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_target <= 'd0; else if(r_ip_cnt >= 16 && r_ip_cnt <= 19) r_ip_target <= {r_ip_target[23:0],ri_mac_data}; else r_ip_target <= r_ip_target; end //计算UDP 或者 ICMP 的数据长度 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ro_udp_len <= 'd0; ro_icmp_len <= 'd0; end else begin ro_udp_len <= r_ip_len - 20; ro_icmp_len <= r_ip_len - 20; end end // 第20字节 检测是目的和源IP是否正确 //检测协议类型 UDP还是ICMP always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_udp_valid <= 'd0; else if(!ri_mac_valid && ri_mac_valid_1d) ro_udp_valid <= 'd0; else if(r_ip_cnt == 20 && r_ip_target == r_source_ip && r_ip_type == 17) ro_udp_valid <= 'd1; else ro_udp_valid <= ro_udp_valid; end //ICMP 同上 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_icmp_valid <= 'd0; else if(!ri_mac_valid && ri_mac_valid_1d) ro_icmp_valid <= 'd0; else if(r_ip_cnt == 20 && r_ip_target == r_source_ip && r_ip_type == 1) ro_icmp_valid <= 'd1; else ro_icmp_valid <= ro_icmp_valid; end //i_mac_valid 信号的下降沿 拉高 last信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_udp_last <= 'd0; else if(!i_mac_valid && ri_mac_valid && r_ip_type == 17) ro_udp_last <= 'd1; else ro_udp_last <= 'd0; end always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_icmp_last <= 'd0; else if(!i_mac_valid && ri_mac_valid && r_ip_type == 1) ro_icmp_last <= 'd1; else ro_icmp_last <= 'd0; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

- 175

- 176

- 177

- 178

- 179

- 180

- 181

- 182

- 183

- 184

- 185

- 186

- 187

- 188

- 189

- 190

- 191

- 192

- 193

- 194

- 195

- 196

- 197

- 198

- 199

- 200

- 201

- 202

- 203

- 204

- 205

- 206

- 207

- 208

- 209

- 210

- 211

- 212

- 213

- 214

- 215

- 216

- 217

- 218

- 219

- 220

- 221

- 222

- 223

- 224

- 225

- 226

- 227

- 228

- 229

- 230

- 231

- 232

- 233

- 234

- 235

- 236

- 237

- 238

- 239

- 240

- 241

- 242

- 243

3.2 IP发送模块

module IP_tx#( parameter P_ST_TARGET_IP = {8'd192,8'd168,8'd1,8'd0}, parameter P_ST_SOURCE_IP = {8'd192,8'd168,8'd1,8'd1} )( input i_clk , input i_rst , /*--------info port --------*/ input [31:0] i_target_ip , input i_target_valid , input [31:0] i_source_ip , input i_source_valid , /*--------data port--------*/ input [7 :0] i_send_type , input [15:0] i_send_len , input [7 :0] i_send_data , input i_send_last , input i_send_valid , output [31:0] o_arp_seek_ip , output o_arp_seek_valid , /*--------mac port--------*/ output [15:0] o_mac_type , output [15:0] o_mac_len , output [7 :0] o_mac_data , output o_mac_last , output o_mac_valid ); /***************function**************/ /***************parameter*************/ /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg [31:0] r_target_ip ; reg [31:0] r_source_ip ; reg [7 :0] ri_send_type ; reg [15:0] ri_send_len ; reg [7 :0] ri_send_data ; reg ri_send_last ; reg ri_send_valid ; reg ri_send_valid_1d ; reg r_fifo_ip_rd_en ; reg [7 :0] r_ip_data ; reg [7 :0] r_ip_valid ; reg [15:0] r_ip_data_cnt ; reg [15:0] r_ip_message ; reg [31:0] r_ip_check ; reg [15:0] ro_mac_type ; reg ro_mac_last ; reg [31:0] ro_arp_seek_ip ; reg ro_arp_seek_valid ; /***************wire******************/ wire [31:0] w_fifo_ip_dout ; wire w_fifo_ip_full ; wire w_fifo_ip_empty ; /***************component*************/ //把要发送的数据存进FIFO,要发送时读出来 FIFO_MAC_8X64 FIFO_IP_8X64_U0 ( .clk (i_clk ), // input wire clk .din (ri_send_data ), // input wire [7 : 0] din .wr_en (ri_send_valid ), // input wire wr_en .rd_en (r_fifo_ip_rd_en ), // input wire rd_en .dout (w_fifo_ip_dout ), // output wire [7 : 0] dout .full (w_fifo_ip_full ), // output wire full .empty (w_fifo_ip_empty ) // output wire empty ); /***************assign****************/ assign o_mac_data = r_ip_data ; assign o_mac_valid = r_ip_valid ; assign o_mac_len = ri_send_len; assign o_mac_type = ro_mac_type; assign o_mac_last = ro_mac_last; assign o_arp_seek_ip = ro_arp_seek_ip ; assign o_arp_seek_valid = ro_arp_seek_valid; /***************always****************/ //目的地址有效 锁存 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_target_ip <= P_ST_TARGET_IP; else if(i_target_valid) r_target_ip <= i_target_ip; else r_target_ip <= r_target_ip; end //源地址有效 锁存 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_source_ip <= P_ST_SOURCE_IP; else if(i_source_valid) r_source_ip <= i_source_ip; else r_source_ip <= r_source_ip; end //锁存 类型和数据等信息 ip报文长度 为 UDP报文 + 20 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_send_type <= 'd0; ri_send_len <= 'd0; ri_send_data <= 'd0; ri_send_last <= 'd0; ri_send_valid <= 'd0; end else if(i_send_valid) begin ri_send_type <= i_send_type ; ri_send_len <= i_send_len + 20; ri_send_data <= i_send_data ; ri_send_last <= i_send_last ; ri_send_valid <= i_send_valid ; end else begin ri_send_type <= ri_send_type ; ri_send_len <= ri_send_len ; ri_send_data <= ri_send_data ; ri_send_last <= 'd0; ri_send_valid <= 'd0; end end // r_ip_data_cnt 计数 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_data_cnt <= 'd0; else if(r_ip_data_cnt == ri_send_len - 1) r_ip_data_cnt <= 'd0; else if(ri_send_valid || r_ip_data_cnt) r_ip_data_cnt <= r_ip_data_cnt + 1; else r_ip_data_cnt <= r_ip_data_cnt; end // ip报文的个数 计数 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_message <= 'd0; else if(o_mac_last) r_ip_message <= r_ip_message + 1; else r_ip_message <= r_ip_message; end //进行首部校验和 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_check <= 'd0; else if(ri_send_valid && r_ip_data_cnt == 0) r_ip_check <= 16'h4500 + ri_send_len + r_ip_message + 16'h4000 + {8'd64,ri_send_type} + r_source_ip[31:16] + r_source_ip[15:0] + r_target_ip[31:16] + r_target_ip[15:0]; else if(r_ip_data_cnt == 1) r_ip_check <= r_ip_check[31:16] + r_ip_check[15:0]; else if(r_ip_data_cnt == 2) r_ip_check <= r_ip_check[31:16] + r_ip_check[15:0]; else if(r_ip_data_cnt == 3) r_ip_check <= ~r_ip_check; else r_ip_check <= r_ip_check; end //打拍生成边沿 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ri_send_valid_1d <= 'd0; else ri_send_valid_1d <= ri_send_valid; end //发送有效信号上升沿 ip帧有效拉高 // mac帧结束信号拉高,ip帧有效拉低 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_valid <= 'd0; else if(ro_mac_last) r_ip_valid <= 'd0; else if(ri_send_valid && !ri_send_valid_1d) r_ip_valid <= 'd1; else r_ip_valid <= r_ip_valid; end //组帧输出 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_ip_data <= 'd0; else case(r_ip_data_cnt) 0 : r_ip_data <= {4'b0100,4'b0101}; //版本+首部长度 1 : r_ip_data <= 'd0; //服务类型 2 : r_ip_data <= ri_send_len[15:8]; //总长度的高8位 3 : r_ip_data <= ri_send_len[7 :0]; //总长度的低8位 4 : r_ip_data <= r_ip_message[15:8]; //报文标识的高8位 5 : r_ip_data <= r_ip_message[7 :0]; //报文标识的低8位 6 : r_ip_data <= {3'b010,5'b00000}; //标志+片偏移 7 : r_ip_data <= 'd0; //片偏移 8 : r_ip_data <= 'd64; //生存时间 9 : r_ip_data <= ri_send_type; //协议类型 10 : r_ip_data <= r_ip_check[15:8]; 11 : r_ip_data <= r_ip_check[7 :0]; 12 : r_ip_data <= r_source_ip[31:24]; 13 : r_ip_data <= r_source_ip[23:16]; 14 : r_ip_data <= r_source_ip[15:8]; 15 : r_ip_data <= r_source_ip[7 :0]; 16 : r_ip_data <= r_target_ip[31:24]; 17 : r_ip_data <= r_target_ip[23:16]; 18 : r_ip_data <= r_target_ip[15:8]; 19 : r_ip_data <= r_target_ip[7 :0]; default : r_ip_data <= w_fifo_ip_dout; endcase end // ip帧 计数到18 从FIFO中读取数据 // mac帧结束信号拉高,不读了 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_fifo_ip_rd_en <= 'd0; else if(ro_mac_last) r_fifo_ip_rd_en <= 'd0; else if(r_ip_data_cnt == 18) r_fifo_ip_rd_en <= 'd1; else r_fifo_ip_rd_en <= r_fifo_ip_rd_en; end //ip帧计数器计到最大 mac 帧结束了 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_mac_last <= 'd0; else if(r_ip_data_cnt == ri_send_len - 1) ro_mac_last <= 'd1; else ro_mac_last <= 'd0; end //输出mac层的报文类型 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ro_mac_type <= 'd0; end else begin ro_mac_type <= 16'h0800; end end //ARP always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ro_arp_seek_ip <= P_ST_TARGET_IP; ro_arp_seek_valid <= 'd0; end else if(ri_send_valid && !ri_send_valid_1d) begin ro_arp_seek_ip <= r_target_ip; ro_arp_seek_valid <= 'd1; end else begin ro_arp_seek_ip <= ro_arp_seek_ip; ro_arp_seek_valid <= 'd0; end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

- 175

- 176

- 177

- 178

- 179

- 180

- 181

- 182

- 183

- 184

- 185

- 186

- 187

- 188

- 189

- 190

- 191

- 192

- 193

- 194

- 195

- 196

- 197

- 198

- 199

- 200

- 201

- 202

- 203

- 204

- 205

- 206

- 207

- 208

- 209

- 210

- 211

- 212

- 213

- 214

- 215

- 216

- 217

- 218

- 219

- 220

- 221

- 222

- 223

- 224

- 225

- 226

- 227

- 228

- 229

- 230

- 231

- 232

- 233

- 234

- 235

- 236

- 237

- 238

- 239

- 240

- 241

- 242

- 243

- 244

- 245

- 246

- 247

- 248

- 249

- 250

- 251

- 252

- 253

- 254

- 255

- 256

- 257

- 258

- 259

- 260

- 261

- 262

- 263

- 264

- 265

- 266

- 267

- 268

- 269

- 270

- 271

- 272

- 273

- 274

- 275

- 276

- 277

4.1 UDP接收模块

module UDP_rx#( parameter P_TARGET_PORT = 16'h8080 , P_SOURCE_PORT = 16'h8080 )( input i_clk , input i_rst , /*--------info port-------*/ input [15:0] i_target_port , input i_target_valid , input [15:0] i_source_port , input i_source_valid , /*--------data port--------*/ output [15:0] o_udp_len , output [7 :0] o_udp_data , output o_udp_last , output o_udp_valid , /*--------ip port--------*/ input [15:0] i_ip_len , input [7 :0] i_ip_data , input i_ip_last , input i_ip_valid ); /***************function**************/ /***************parameter*************/ /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg [15:0] r_target_port ; reg [15:0] r_source_port ; reg [15:0] ri_ip_len ; reg [7 :0] ri_ip_data ; reg ri_ip_last ; reg ri_ip_valid ; reg [15:0] ro_udp_len ; reg ro_udp_last ; reg ro_udp_valid ; reg [15:0] r_udp_cnt ; /***************wire******************/ /***************component*************/ /***************assign****************/ assign o_udp_len = ro_udp_len ; assign o_udp_data = ri_ip_data ; assign o_udp_last = ro_udp_last ; assign o_udp_valid = ro_udp_valid ; /***************always****************/ //锁存 目标端口 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_target_port <= 'd0; else if(i_target_valid) r_target_port <= i_target_port; else r_target_port <= r_target_port; end //锁存 源端口 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_source_port <= 'd0; else if(i_source_valid) r_source_port <= i_source_port; else r_source_port <= r_source_port; end //ip有效信号 锁存ip的信息 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_ip_len <= 0; ri_ip_data <= 0; ri_ip_last <= 0; ri_ip_valid <= 0; end else if(i_ip_valid) begin ri_ip_len <= i_ip_len ; ri_ip_data <= i_ip_data ; ri_ip_last <= i_ip_last ; ri_ip_valid <= i_ip_valid; end else begin ri_ip_len <= ri_ip_len ; ri_ip_data <= 'd0 ; ri_ip_last <= 'd0 ; ri_ip_valid <= 'd0; end end //ip有效信号,r_udp_cnt + 1 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_udp_cnt <= 'd0; else if(ri_ip_valid) r_udp_cnt <= r_udp_cnt + 1; else r_udp_cnt <= 'd0; end //UDP帧的长度 为 IP帧长度 - 8 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_udp_len <= 'd0; else ro_udp_len <= ri_ip_len - 8; end //UDP接收到第7位 拉高UDP有效,跟数据一起出来 //UDP发送到长度-1 时,拉低有效信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_udp_valid <= 'd0; else if(r_udp_cnt == ri_ip_len - 1) ro_udp_valid <= 'd0; else if(r_udp_cnt == 7) ro_udp_valid <= 'd1; else ro_udp_valid <= ro_udp_valid; end //拉高last结束信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_udp_last <= 'd0; else if(r_udp_cnt == ri_ip_len - 2) ro_udp_last <= 'd1; else ro_udp_last <= 'd0; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

4.2 UDP发送模块

module UDP_tx#( parameter P_TARGET_PORT = 16'h8080 , P_SOURCE_PORT = 16'h8080 )( input i_clk , input i_rst , /*--------info port-------*/ input [15:0] i_target_port , input i_target_valid , input [15:0] i_source_port , input i_source_valid , /*--------data port--------*/ input [15:0] i_send_len , input [7 :0] i_send_data , input i_send_last , input i_send_valid , /*--------ip port--------*/ output [15:0] o_ip_len , output [7 :0] o_ip_data , output o_ip_last , output o_ip_valid ); /***************function**************/ /***************parameter*************/ localparam P_ST_MIN_LEN = 18 + 8; /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg [15:0] r_target_port ; reg [15:0] r_source_port ; reg [15:0] ri_send_len ; reg [7 :0] ri_send_data ; reg ri_send_last ; reg ri_send_valid ; reg [15:0] ro_ip_len ; reg [7 :0] ro_ip_data ; reg ro_ip_last ; reg ro_ip_valid ; reg r_fifo_udp_rd_en; reg [15:0] r_udp_cnt ; reg r_fifo_udp_empty; /***************wire******************/ wire [7:0] w_fifo_udp_dout ; wire w_fifo_udp_full ; wire w_fifo_udp_empty; /***************component*************/ //要写的数据存进FIFO FIFO_MAC_8X64 FIFO_UDP_8X64_U0 ( .clk (i_clk ), // input wire clk .din (ri_send_data ), // input wire [7 : 0] din .wr_en (ri_send_valid ), // input wire wr_en .rd_en (r_fifo_udp_rd_en ), // input wire rd_en .dout (w_fifo_udp_dout ), // output wire [7 : 0] dout .full (w_fifo_udp_full ), // output wire full .empty (w_fifo_udp_empty ) // output wire empty ); /***************assign****************/ assign o_ip_len = ro_ip_len ; assign o_ip_data = ro_ip_data ; assign o_ip_last = ro_ip_last ; assign o_ip_valid = ro_ip_valid ; /***************always****************/ //锁存 目的端口 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_target_port <= P_TARGET_PORT; else if(i_target_valid) r_target_port <= i_target_port; else r_target_port <= r_target_port; end //锁存 源端口 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_source_port <= P_SOURCE_PORT; else if(i_source_valid) r_source_port <= i_source_port; else r_source_port <= r_source_port; end //锁存输入的IP数据 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_send_data <= 'd0; ri_send_last <= 'd0; ri_send_valid <= 'd0; end else begin ri_send_data <= i_send_data ; ri_send_last <= i_send_last ; ri_send_valid <= i_send_valid; end end //锁存输入的数据长度 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ri_send_len <= 'd0; else if(i_send_valid) ri_send_len <= i_send_len ; else ri_send_len <= ri_send_len; end //发送UDP数据长度小于18 并且已经完成18+8 的UDP帧 ,后计数器清空 //大于18 ,正常发完 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_udp_cnt <= 'd0; else if(ri_send_len < 18 && r_udp_cnt == P_ST_MIN_LEN - 1) r_udp_cnt <= 'd0; else if(ri_send_len >= 18 && r_udp_cnt == (ri_send_len + 8) - 1) r_udp_cnt <= 'd0; else if(ri_send_valid || r_udp_cnt) r_udp_cnt <= r_udp_cnt + 1; else r_udp_cnt <= r_udp_cnt; end //如果数据长度小于18 就默认18 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_ip_len <= 'd0; else if(ri_send_len < 18) ro_ip_len <= 18; else ro_ip_len <= ri_send_len + 8; end //如果收到ip_last信号,ip有效拉低 //收到输入有效信号,ip有效拉高 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_ip_valid <= 'd0; else if(ro_ip_last) ro_ip_valid <= 'd0; else if(ri_send_valid) ro_ip_valid <= 'd1; else ro_ip_valid <= ro_ip_valid; end //UDP发完后,拉高ip_last信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_ip_last <= 'd0; else if(ri_send_len < 18 && r_udp_cnt == P_ST_MIN_LEN - 1) ro_ip_last <= 'd1; else if(ri_send_len >= 18 && r_udp_cnt == (ri_send_len + 8) - 1) ro_ip_last <= 'd1; else ro_ip_last <= 'd0; end //输出完8字节 UDP帧的头 FIFO读使能打开 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_fifo_udp_rd_en <= 'd0; else if(r_udp_cnt == (ri_send_len + 8) - 1) r_fifo_udp_rd_en <= 'd0; else if(r_udp_cnt == 6) r_fifo_udp_rd_en <= 'd1; else r_fifo_udp_rd_en <= r_fifo_udp_rd_en; end //空信号打拍 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_fifo_udp_empty <= 'd0; else r_fifo_udp_empty <= w_fifo_udp_empty; end //组帧输出 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_ip_data <= 'd0; else case(r_udp_cnt) 0 : ro_ip_data <= r_source_port[15:8]; 1 : ro_ip_data <= r_source_port[7 :0]; 2 : ro_ip_data <= r_target_port[15:8]; 3 : ro_ip_data <= r_target_port[7 :0]; 4 : ro_ip_data <= ro_ip_len[15:8]; 5 : ro_ip_data <= ro_ip_len[7 :0]; 6 : ro_ip_data <= 'd0; 7 : ro_ip_data <= 'd0; default : ro_ip_data <= !r_fifo_udp_empty ? w_fifo_udp_dout : 'd0; endcase end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

- 175

- 176

- 177

- 178

- 179

- 180

- 181

- 182

- 183

- 184

- 185

- 186

- 187

- 188

- 189

- 190

- 191

- 192

- 193

- 194

- 195

- 196

- 197

- 198

- 199

- 200

- 201

- 202

- 203

- 204

- 205

- 206

- 207

- 208

- 209

- 210

- 211

- 212

- 213

- 214

- 215

- 216

5.1 ICMP接收模块

module ICMP_rx( input i_clk , input i_rst , /*--------rec port--------*/ input [15:0] i_icmp_len , input [7 :0] i_icmp_data , input i_icmp_last , input i_icmp_valid , /*--------send port--------*/ output o_trig_reply , output [15:0] o_trig_seq ); /***************function**************/ /***************parameter*************/ /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg [15:0] ri_icmp_len ; reg [7 :0] ri_icmp_data ; reg ri_icmp_last ; reg ri_icmp_valid ; reg ro_trig_reply ; reg [15:0] r_icmp_cnt ; reg [7 :0] r_type ; reg [15:0] ro_trig_seq ; /***************wire******************/ /***************component*************/ /***************assign****************/ assign o_trig_reply = ro_trig_reply ; assign o_trig_seq = ro_trig_seq ; /***************always****************/ //输入信号打拍 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_icmp_len <= 'd0; ri_icmp_data <= 'd0; ri_icmp_last <= 'd0; ri_icmp_valid <= 'd0; end else begin ri_icmp_len <= i_icmp_len ; ri_icmp_data <= i_icmp_data ; ri_icmp_last <= i_icmp_last ; ri_icmp_valid <= i_icmp_valid; end end //开始计数 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_icmp_cnt <= 'd0; else if(ri_icmp_valid) r_icmp_cnt <= r_icmp_cnt + 1; else r_icmp_cnt <= 'd0; end //存下icmp类型 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_type <= 'd0; else if(ri_icmp_valid && r_icmp_cnt == 0) r_type <= ri_icmp_data; else r_type <= r_type; end //ICMP帧的 序号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_trig_seq <= 'd0; else if(r_icmp_cnt >=6 && r_icmp_cnt <= 7) ro_trig_seq <= {ro_trig_seq[7 :0],ri_icmp_data}; else ro_trig_seq <= ro_trig_seq; end //类型为8 计数8个 拉高序号的回复信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_trig_reply <= 'd0; else if(r_icmp_cnt == 7 && r_type == 8) ro_trig_reply <= 'd1; else ro_trig_reply <= 'd0; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

5.2 ICMP发送模块

module ICMP_tx( input i_clk , input i_rst , input i_trig_reply , input [15:0] i_trig_seq , output [15:0] o_icmp_len , output [7 :0] o_icmp_data , output o_icmp_last , output o_icmp_valid ); /***************function**************/ /***************parameter*************/ localparam P_LEN = 40 ; /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg ri_trig_reply ; reg [15:0] ri_trig_seq ; reg [15:0] ro_icmp_len ; reg [7 :0] ro_icmp_data ; reg ro_icmp_last ; reg ro_icmp_valid ; reg [15:0] r_icmp_cnt ; reg [31:0] r_icmp_check ; reg [7 :0] r_check_cnt ; /***************wire******************/ /***************component*************/ /***************assign****************/ assign o_icmp_len = ro_icmp_len ; assign o_icmp_data = ro_icmp_data ; assign o_icmp_last = ro_icmp_last ; assign o_icmp_valid = ro_icmp_valid; /***************always****************/ //序号值 和 信号 打一拍 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_trig_reply <= 'd0; ri_trig_seq <= 'd0; end else begin ri_trig_reply <= i_trig_reply; ri_trig_seq <= i_trig_seq; end end //r_check_cnt 在 ri_trig_reply拉高后 +1 //r_icmp_cnt 计数完,r_check_cnt清空 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_check_cnt <= 'd0; else if(r_icmp_cnt == P_LEN - 1) r_check_cnt <= 'd0; else if(r_check_cnt == 3) r_check_cnt <= r_check_cnt + 1; else if(ri_trig_reply | r_check_cnt) r_check_cnt <= r_check_cnt + 1; else r_check_cnt <= r_check_cnt; end //ICMP的校验和 和IP层的首部校验和一样 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_icmp_check <= 'd0; else if(r_check_cnt == 0) r_icmp_check <= 16'h0001 + ri_trig_seq; else if(r_check_cnt == 1) r_icmp_check <= r_icmp_check[31:16] + r_icmp_check[15:0]; else if(r_check_cnt == 2) r_icmp_check <= r_icmp_check[31:16] + r_icmp_check[15:0]; else if(r_check_cnt == 3) r_icmp_check <= ~r_icmp_check; else r_icmp_check <= r_icmp_check; end //校验完成后 开始组帧计数 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_icmp_cnt <= 'd0; else if(r_icmp_cnt == P_LEN - 1) r_icmp_cnt <= 'd0; else if(r_check_cnt == 3 || r_icmp_cnt) r_icmp_cnt <= r_icmp_cnt + 1; else r_icmp_cnt <= r_icmp_cnt; end //ICMP的长度 输出 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_icmp_len <= 'd0; else ro_icmp_len <= P_LEN; end //校验完成输出 ICMP帧,使能拉高 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_icmp_valid <= 'd0; else if(r_icmp_cnt == P_LEN - 1) ro_icmp_valid <= 'd0; else if(r_check_cnt == 3) ro_icmp_valid <= 'd1; else ro_icmp_valid <= ro_icmp_valid; end //输出结束信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_icmp_last <= 'd0; else if(r_icmp_cnt == P_LEN - 2) ro_icmp_last <= 'd1; else ro_icmp_last <= 'd0; end //组帧 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_icmp_data <= 'd0; else case(r_icmp_cnt) 0 :ro_icmp_data <= 'd0; 1 :ro_icmp_data <= 'd0; 2 :ro_icmp_data <= r_icmp_check[15:8]; 3 :ro_icmp_data <= r_icmp_check[7 :0]; 4 :ro_icmp_data <= 8'h00; 5 :ro_icmp_data <= 8'h01; 6 :ro_icmp_data <= ri_trig_seq[15:8]; 7 :ro_icmp_data <= ri_trig_seq[7 :0]; default :ro_icmp_data <= 'd0; endcase end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

6.1 ARP接收模块

module ARP_rx#( parameter P_TARGET_IP = {8'd192,8'd168,8'd1,8'd1}, parameter P_SOURCE_MAC = {8'h00,8'h00,8'h00,8'h00,8'h00,8'h00}, parameter P_SOURCE_IP = {8'd192,8'd168,8'd1,8'd2} )( input i_clk , input i_rst , input [31:0] i_source_ip , input i_s_ip_valid , /*--------info port--------*/ output [47:0] o_target_mac , output [31:0] o_target_ip , output o_target_valid , output o_tirg_reply , /*--------MAC port--------*/ input [7 :0] i_mac_data , input i_mac_last , input i_mac_valid ); /***************function**************/ /***************parameter*************/ /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg [47:0] ro_target_mac ; reg [31:0] ro_target_ip ; reg ro_target_valid ; reg [7 :0] ri_mac_data ; reg [7 :0] ri_mac_data_1d ; reg ri_mac_last ; reg ri_mac_valid ; reg [15:0] r_mac_cnt ; reg [15:0] r_arp_op ; reg ro_tirg_reply ; reg [31:0] ri_source_ip ; /***************wire******************/ /***************component*************/ /***************assign****************/ assign o_target_mac = ro_target_mac ; assign o_target_ip = ro_target_ip ; assign o_tirg_reply = ro_tirg_reply ; assign o_target_valid = ro_target_valid; /***************always****************/ //打拍 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_mac_data <= 'd0; ri_mac_last <= 'd0; ri_mac_valid <= 'd0; ri_mac_data_1d <= 'd0; end else begin ri_mac_data <= i_mac_data ; ri_mac_last <= i_mac_last ; ri_mac_valid <= i_mac_valid; ri_mac_data_1d <= ri_mac_data; end end //源ip 锁存 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ri_source_ip <= P_SOURCE_IP; else if(i_s_ip_valid) ri_source_ip <= i_source_ip; else ri_source_ip <= ri_source_ip; end //mac计数器 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_mac_cnt <= 'd0; else if(ri_mac_valid) r_mac_cnt <= r_mac_cnt + 1; else r_mac_cnt <= 'd0; end //获得ARP的操作类型 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_arp_op <= 'd0; else if(r_mac_cnt >= 6 && r_mac_cnt <= 7) r_arp_op <= {r_arp_op[7 :0],ri_mac_data}; else r_arp_op <= r_arp_op; end //获得目的mac always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_target_mac <= 'd0; else if(r_mac_cnt >= 8 && r_mac_cnt <= 13 && (r_arp_op == 1 || r_arp_op == 2)) ro_target_mac <= {ro_target_mac[39:0],ri_mac_data}; else ro_target_mac <= ro_target_mac; end //获得目的ip always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_target_ip <= 'd0; else if(r_mac_cnt >= 14 && r_mac_cnt <= 17 && (r_arp_op == 1 || r_arp_op == 2)) ro_target_ip <= {ro_target_ip[23:0],ri_mac_data}; else ro_target_ip <= ro_target_ip; end //计数到17 拉高有效信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_target_valid <= 'd0; else if(r_mac_cnt == 17) ro_target_valid <= 'd1; else ro_target_valid <= 'd0; end //计数到18 类型为1 请求 //回复信号触发信号 拉高 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_tirg_reply <= 'd0; else if(r_mac_cnt == 18 && r_arp_op == 1) ro_tirg_reply <= 'd1; else ro_tirg_reply <= 'd0; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

6.2 ARP发送模块

module ARP_tx#( parameter P_TARGET_IP = {8'd192,8'd168,8'd1,8'd1}, parameter P_SOURCE_MAC = {8'h00,8'h00,8'h00,8'h00,8'h00,8'h00}, parameter P_SOURCE_IP = {8'd192,8'd168,8'd1,8'd2} )( input i_clk , input i_rst , input [31:0] i_target_ip , input i_target_valid , input [47:0] i_source_mac , input i_s_mac_valid , input [31:0] i_source_ip , input i_s_ip_valid , input [47:0] i_reply_mac , output [31:0] o_seek_ip , output o_seek_valid , input i_trig_reply , input i_active_send , output [7 :0] o_mac_data , output o_mac_last , output o_mac_valid ); /***************function**************/ /***************parameter*************/ localparam P_LEN = 46 ; /***************port******************/ /***************mechine***************/ /***************reg*******************/ reg [31:0] r_target_ip ; reg ri_trig_reply ; reg ri_active_send ; reg [7 :0] ro_mac_data ; reg ro_mac_last ; reg ro_mac_valid ; reg [15:0] r_mac_cnt ; reg [15:0] r_arp_op ; reg [47:0] ri_source_mac ; reg [31:0] ri_source_ip ; reg [31:0] ro_seek_ip ; reg ro_seek_valid ; reg [47:0] ri_reply_mac ; reg [15:0] r_arp_cnt ; /***************wire******************/ wire w_act ; /***************component*************/ /***************assign****************/ assign o_mac_data = ro_mac_data ; assign o_mac_last = ro_mac_last ; assign o_mac_valid = ro_mac_valid ; assign o_seek_ip = ro_seek_ip ; assign o_seek_valid = ro_seek_valid ; assign w_act = r_arp_cnt == 10; /***************always****************/ //主动ARP和被动ARP 触发有效 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_seek_valid <= 'd0; else if(i_trig_reply | i_active_send) ro_seek_valid <= 'd1; else ro_seek_valid <= 'd0; end //输出 源ip always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_seek_ip <= 'd0; else ro_seek_ip <= ri_source_ip; end //输入目的有效 获得目的ip always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_target_ip <= P_TARGET_IP; else if(i_target_valid) r_target_ip <= i_target_ip; else r_target_ip <= r_target_ip; end //输入mac有效,获得源mac always@(posedge i_clk,posedge i_rst) begin if(i_rst) ri_source_mac <= P_SOURCE_MAC; else if(i_s_mac_valid) ri_source_mac <= i_source_mac; else ri_source_mac <= ri_source_mac; end //输入ip有效,获得源ip always@(posedge i_clk,posedge i_rst) begin if(i_rst) ri_source_ip <= P_SOURCE_IP; else if(i_s_ip_valid) ri_source_ip <= i_source_ip; else ri_source_ip <= ri_source_ip; end // 被动触发 和主动触发信号打拍 always@(posedge i_clk,posedge i_rst) begin if(i_rst) begin ri_trig_reply <= 'd0; ri_active_send <= 'd0; end else begin ri_trig_reply <= i_trig_reply ; ri_active_send <= i_active_send | w_act; end end //r_arp_cnt计数器 0 到 11 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_arp_cnt <= 'd0; else if(r_arp_cnt < 11) r_arp_cnt <= r_arp_cnt + 1; else r_arp_cnt <= r_arp_cnt; end //打拍后的触发信号,控制开始mac帧计数 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_mac_cnt <= 'd0; else if(r_mac_cnt == P_LEN - 1) r_mac_cnt <= 'd0; else if(ri_trig_reply || ri_active_send || r_mac_cnt) r_mac_cnt <= r_mac_cnt + 1; else r_mac_cnt <= r_mac_cnt; end //打拍后的触发信号,控制回复类型值 always@(posedge i_clk,posedge i_rst) begin if(i_rst) r_arp_op <= 'd0; else if(ri_trig_reply) r_arp_op <= 'd2; else if(ri_active_send) r_arp_op <= 'd1; else r_arp_op <= r_arp_op; end //得到mac帧 用于回复 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ri_reply_mac <= 'd0; else ri_reply_mac <= i_reply_mac; end //组帧输出 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_mac_data <= 'd0; else case(r_mac_cnt) 0 :ro_mac_data <= 'd0; 1 :ro_mac_data <= 'd1; 2 :ro_mac_data <= 8'h08; 3 :ro_mac_data <= 8'h00; 4 :ro_mac_data <= 'd6; 5 :ro_mac_data <= 'd4; 6 :ro_mac_data <= r_arp_op[15:8]; 7 :ro_mac_data <= r_arp_op[7 :0]; 8 :ro_mac_data <= ri_source_mac[47:40]; 9 :ro_mac_data <= ri_source_mac[39:32]; 10 :ro_mac_data <= ri_source_mac[31:24]; 11 :ro_mac_data <= ri_source_mac[23:16]; 12 :ro_mac_data <= ri_source_mac[15: 8]; 13 :ro_mac_data <= ri_source_mac[7 : 0]; 14 :ro_mac_data <= ri_source_ip[31:24]; 15 :ro_mac_data <= ri_source_ip[23:16]; 16 :ro_mac_data <= ri_source_ip[15: 8]; 17 :ro_mac_data <= ri_source_ip[7 : 0]; 18 :ro_mac_data <= r_arp_op == 2 ? ri_reply_mac[47:40] : 8'h00; 19 :ro_mac_data <= r_arp_op == 2 ? ri_reply_mac[39:32] : 8'h00; 20 :ro_mac_data <= r_arp_op == 2 ? ri_reply_mac[31:24] : 8'h00; 21 :ro_mac_data <= r_arp_op == 2 ? ri_reply_mac[23:16] : 8'h00; 22 :ro_mac_data <= r_arp_op == 2 ? ri_reply_mac[15: 8] : 8'h00; 23 :ro_mac_data <= r_arp_op == 2 ? ri_reply_mac[7 : 0] : 8'h00; 24 :ro_mac_data <= r_target_ip[31:24]; 25 :ro_mac_data <= r_target_ip[23:16]; 26 :ro_mac_data <= r_target_ip[15: 8]; 27 :ro_mac_data <= r_target_ip[7 : 0]; default :ro_mac_data <= 'd0; endcase end //到长度就拉低有效信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_mac_valid <= 'd0; else if(r_mac_cnt == P_LEN - 1) ro_mac_valid <= 'd0; else if(ri_trig_reply || ri_active_send ) ro_mac_valid <= 'd1; else ro_mac_valid <= ro_mac_valid; end //产生last信号 always@(posedge i_clk,posedge i_rst) begin if(i_rst) ro_mac_last <= 'd0; else if(r_mac_cnt == P_LEN - 2) ro_mac_last <= 'd1; else ro_mac_last <= 'd0; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

- 61

- 62

- 63

- 64

- 65

- 66

- 67

- 68

- 69

- 70

- 71

- 72

- 73

- 74

- 75

- 76

- 77

- 78

- 79

- 80

- 81

- 82

- 83

- 84

- 85

- 86

- 87

- 88

- 89

- 90

- 91

- 92

- 93

- 94

- 95

- 96

- 97

- 98

- 99

- 100

- 101

- 102

- 103

- 104

- 105

- 106

- 107

- 108

- 109

- 110

- 111

- 112

- 113

- 114

- 115

- 116

- 117

- 118

- 119

- 120

- 121

- 122

- 123

- 124

- 125

- 126

- 127

- 128

- 129

- 130

- 131

- 132

- 133

- 134

- 135

- 136

- 137

- 138

- 139

- 140

- 141

- 142

- 143

- 144

- 145

- 146

- 147

- 148

- 149

- 150

- 151

- 152

- 153

- 154

- 155

- 156

- 157

- 158

- 159

- 160

- 161

- 162

- 163

- 164

- 165

- 166

- 167

- 168

- 169

- 170

- 171

- 172

- 173

- 174

- 175

- 176

- 177

- 178

- 179

- 180

- 181

- 182

- 183

- 184

- 185

- 186

- 187

- 188

- 189

- 190

- 191

- 192

- 193

- 194

- 195

- 196

- 197

- 198

- 199

- 200

- 201

- 202

- 203

- 204

- 205

- 206

- 207

- 208

- 209

- 210

- 211

- 212

- 213

- 214

- 215

- 216

- 217

- 218

- 219

- 220

- 221

- 222

- 223

- 224

- 225

- 226

- 227

- 228

- 229

- 230

- 231

- 232

- 233

- 234

- 235

- 236

- 237

- 238

- 239

- 240

- 241

- 242

6.3 ARP表模块