热门标签

热门文章

- 1【软件质量】软件安全性_安全关键系统的两类是什么?这两类系统之间有什么重要的区别?

- 2Mac 中修改默认 Python 版本 - 同时保留 python 2 和 python3_mac上有python2和python3,默认版本

- 3基于SSM+Jsp+Mysql的准速达物流管理系统

- 4Git恢复到之前版本_git回滚到上个版本

- 5vue element UI常遇到的bug_elementui表单的bug

- 6redis安装步骤以及使用命令_redis怎么安装使用

- 7Java架构师学习路线

- 8车载测试需要有哪些知识需要学习的?_车载测试资料

- 9初次使用git上传项目,教你一步步上传文件,经验分享_阿里云云效新建了代码库如何上传项目

- 10App Store 新定价机制 - 2023最新版_iap苹果对账美元

当前位置: article > 正文

Xilinx FPGA——ISE软件使用_xilinx ise

作者:知新_RL | 2024-05-11 15:25:29

赞

踩

xilinx ise

项目需求更换了XC6SLX9-3TQG144C , Spartan6系列FPGA,需要使用ISE开发环境,我使用的是ISE 14.7版本。

一、新建工程

点击 Finish 新建工程完成。

二、给工程添加文件

新建文件后,添加点亮LED灯代码如下:

-

- module flow_led(

- input sys_clk , //系统时钟

- // input sys_rst_n, //系统复位,低电平有效

- output reg led //4个LED灯

- );

-

- //reg define

- reg [23:0] counter;

-

- //计数器对系统时钟计数,计时0.2秒

- always @(posedge sys_clk ) begin

- // if (!sys_rst_n)

- // counter <= 24'd0;

- if (counter < 24'd1000_0000)

- counter <= counter + 1'b1;

- else

- counter <= 24'd0;

- end

-

- //通过移位寄存器控制IO口的高低电平,从而改变LED的显示状态

- always @(posedge sys_clk ) begin

- // if (!sys_rst_n)

- // led <= 4'b0001;

- if(counter == 24'd1000_0000)

- led <= ~led;

- end

- endmodule

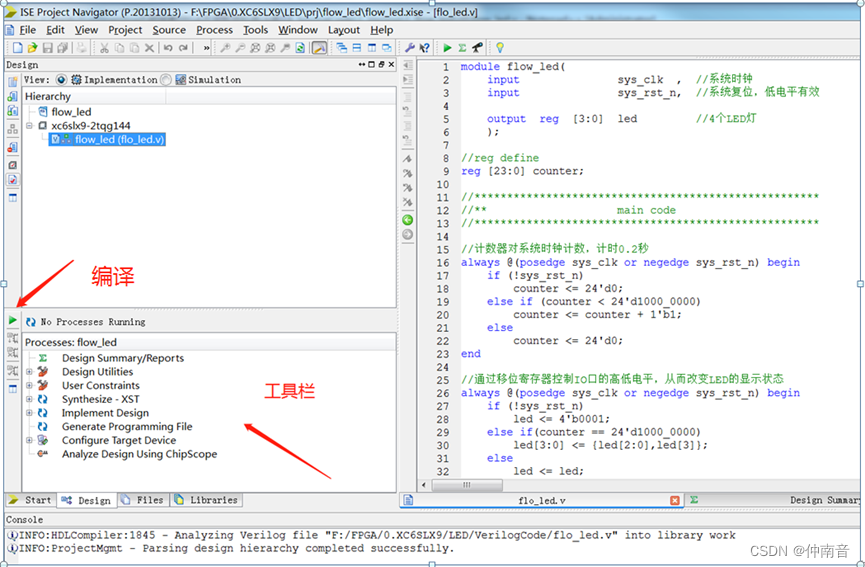

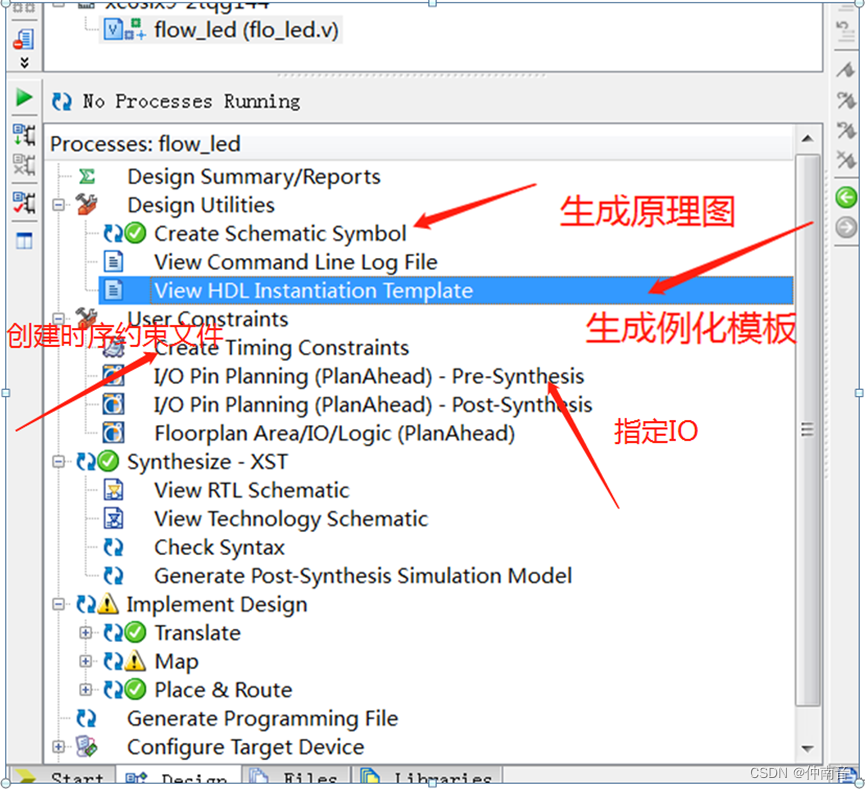

三、工具栏简介

四、添加时序约束文件

时序约束文件中,可指定IO口,和对输入时钟进行约束。

- #系统时钟时序约束

- NET "sys_clk" TNM_NET = "sys_clk_pin";

- TIMESPEC TS_sys_clk_pin = PERIOD "sys_clk_pin" 50000 KHz;

- NET "sys_clk" CLOCK_DEDICATED_ROUTE = FALSE;

- #------------------------------系统时钟和复位-----------------------------------

- //NET sys_clk LOC = N8 | IOSTANDARD = "LVCMOS33";

- //NET sys_rst_n LOC = G16 | IOSTANDARD = "LVCMOS33";

-

-

- NET "sys_clk" LOC = P84;

- NET "sys_clk" IOSTANDARD = LVCMOS33;

-

- //NET "sys_rst_n" LOC = P41;

- //NET "sys_rst_n" IOSTANDARD = LVCMOS33;

-

- NET "led" LOC = P50;

- NET "led" IOSTANDARD = LVCMOS33;

也可以通过工具栏中的IO指定功能进行视图化配置,然后自动生成时序约束文件。

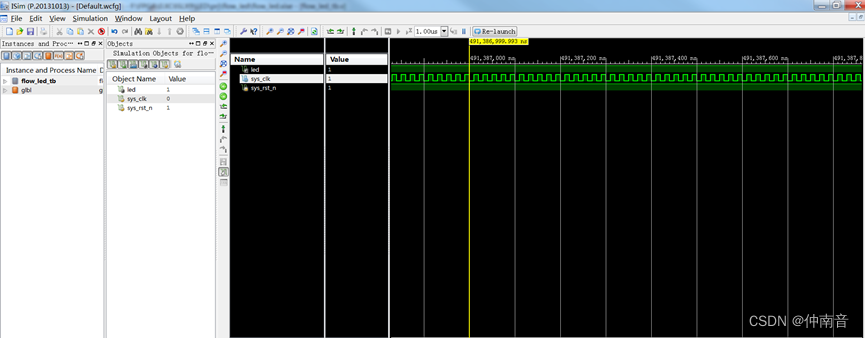

五、仿真

六、下载程序到芯片

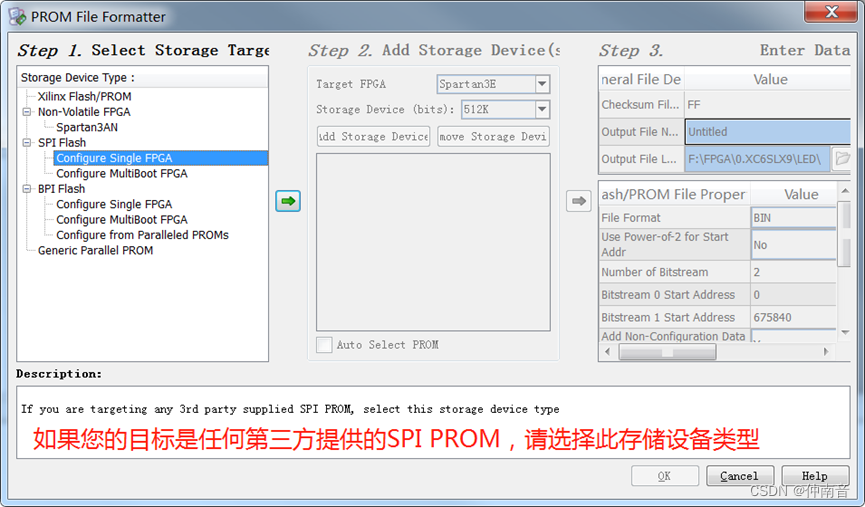

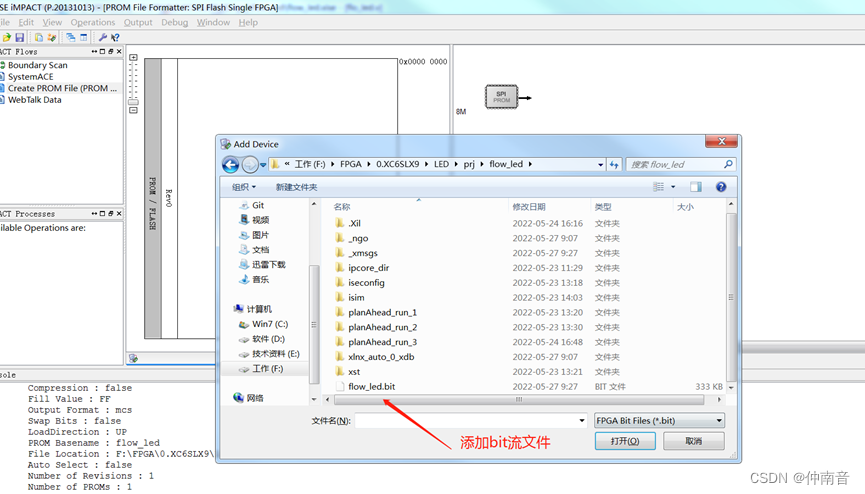

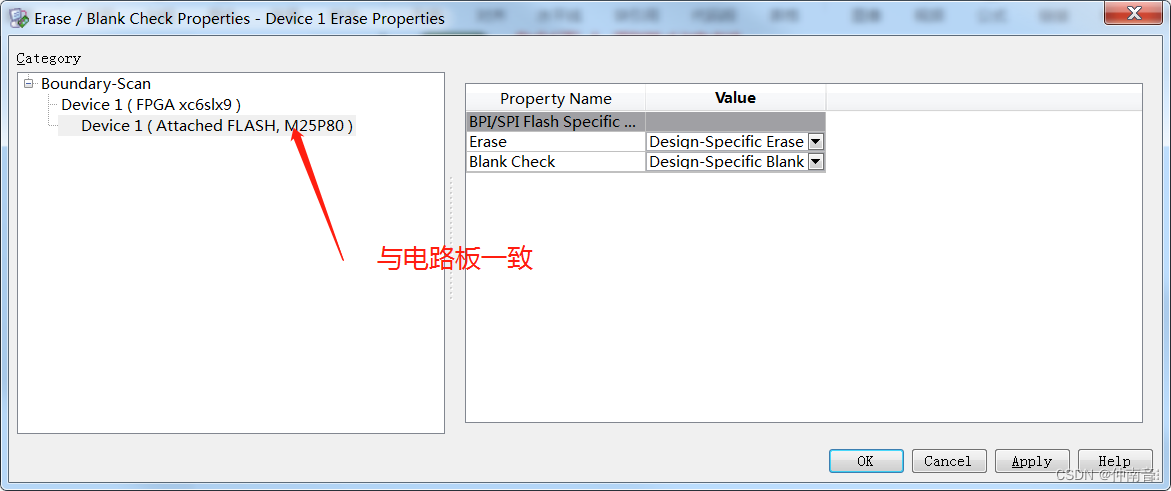

七、生成固化文件

或者:

问题记录:若固化文件下载出现 “Done did not go high”,以下是解决方法:

- 关闭工程重新打开ISE,重新插拔烧录器

- 若1失败,则右击“Processes”窗口中的“Generate Programming File”,点击“Process Properties”左边的“Configuration Options”,找到“Umused IOB Pins”选项,将其修改成“Float”。 (没有使用的引脚设置成浮空状态)

- 若2失败,则在“iMpact”界面中的Edit ---------> Preferences ------>IMPACT- Configuration Preferences 中选择“Use HighZ intstead of Bypass”,选中应用即可,我是到这一步就成功了。

- 若3失败,在生成bit流文件之前,右击“Processes”窗口中的“Generate Programming File”,点击“Startup Options”,找到“Match Cycle”,将其修改为最大值6。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/知新_RL/article/detail/555275

推荐阅读

相关标签