- 1PyQt5 QPainter在QPixmap上实现单一鼠标绘图功能。两种方式:在paintEvent函数外实现和内实现_qpixmap 填充鼠标图标

- 2element—ui的bug_element漏洞

- 3Jenkins从配置到实战(一) - 实现C/C++项目自动化构建_jenkins c++

- 4Shell脚本入门:编写自动化任务的利器

- 5什么是强化学习?预测股票的效果如何?

- 6Method-Swizzling 方法交换

- 7《深入分布式缓存 从原理到实践》笔记_深入分布式缓存:从原理到实践 pdf

- 8程序员面试过关必备的5大网站,你用过几个?_在哪里可以刷各职业面试题

- 9阅读笔记(Neurocomputing 2016)Stitching contaminated images_neuralcomputing投稿要求

- 10Leetcode-合并两个有序链表_合并两个有序链表leetcode

FPGA的高速收发器(GTX/GTY/GTP)的快速上手教程_gty高速收发器

赞

踩

工作中有对GT收发器的使用需求, 学习的过程中,看手册,看别人的文章。有些大佬写得非常好,但他们可能不是针对使用来写的,我在实际使用IP核的过程中,还是会有很多疑惑。

所以我就针对怎么使用GTX等IP核写的这几篇文章,希望可以帮助到想快速学会如何使用IP核的小伙伴。

这篇文章是写我对这个IP核一些理解,IP核的配置可以参考XILINX的IP核GTX的配置。IP核的例程修改参考对于XILINX的GTX官方例程的讲解。有了对IP核各项配置的理解以及对例程的修改,相信一定可以帮你快速的学会使用这个IP核。

高速收发器(GTX/GTY/GTP)是啥

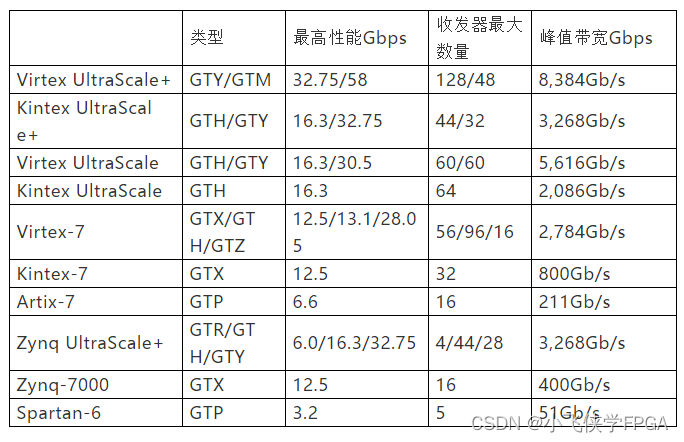

它是Xilinx的针对Gigabit应用的FPGA基本都会集成一些高速串行接口,统称为

Gigabit Transceiver(GTx),下图是各个系列的芯片所包含的GT资源,以及它们的相关性能参数。

它能干啥

首先可以把它理解为一个高速并串转换器(串行速率可达几十G),把你给它的并行数据,转换为串行输出,或者给它串行数据,它会给你转换为并行数据。它可以单独作为发送装置或接收装置,也可以一起运行。

可以自定义协议来实现通信。

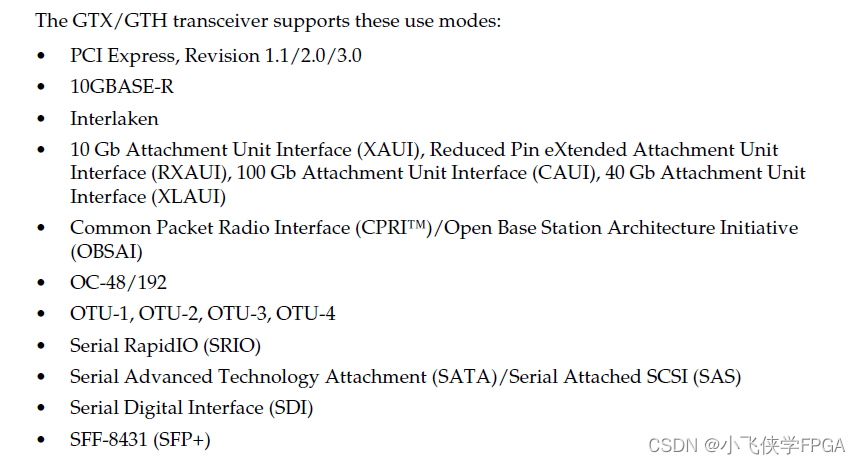

它也经常用来配合其他IP核,实现协议通信。比如常用于两块板子之间通信的Auraro协议,可以配合Xilinx 提供的 Aurora IP 核来实现。GTx主要负责物理层(Physical Layer)数据的发送和接收,包括一系列的物理层任务,如信号的串行化和解串行化、编码和解码、时钟恢复等。Aurora IP 核则负责帧生成和检查、错误处理、信道初始化、链路状态管理等功能。它还支持以下的协议

GTX支持的协议

我是把它作为信号发生器来使用的,单独使用它的发射端输出稳定高速的信号。

为什么需要高速收发器?

主要是还是速率的问题,特别是在现在对于速率要求越来越高的情况下。在高速串行口之前,当数据速率开始超过1gb /s时,并行I/O方案就会达到物理限制,并且不再能够提供可靠、经济的方式来保持信号同步。

在早期的并行I/O总线中,接口对齐问题阻碍了与外部设备的有效通信。随着更高的速度在数字设计中变得普遍,管理信号延迟成为一个问题。

接口对齐问题是指在并行通信中,由于各个数据位可能在物理线路长度、信号传播速度等方面存在不同,因此它们可能无法在完全相同的时间到达目标设备,导致数据传输过程中发生错误。简单地说,就是各个数据线的信号需要在同一时刻到达目标,对齐就是把这个时刻统一。

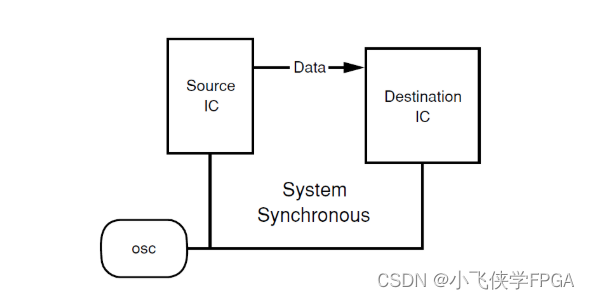

之前也有一些解决方案,比如利用系统时钟来同步:两个ic之间的通信,在两个ic上都应用一个公共时钟,用于数据传输和接收。

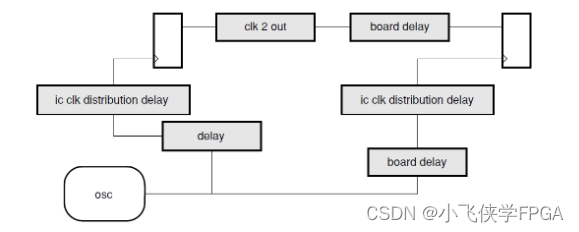

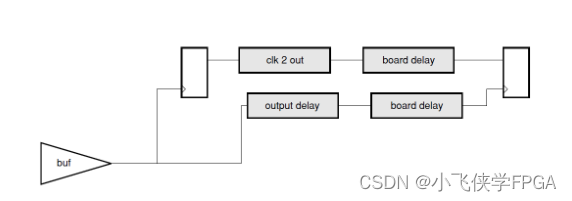

看起来好像很容易就解决了时间同步的问题,但实际上的系统是这样的

各种延误在速率低的情况下还可以忽略,因为延误相对于有效信号来说非常小。但随着速率的提高,延误的影响越来越大,甚至导致系统上的错误。随之而来的解决方法是,不依靠系统时钟,发送方在发生数据的时候,也发送一个同步的时钟

这样可以消除部分延迟,同时由于两根线是从同一个地方发出,传输距离等也很容易做的一致,所以有些延迟也可以抵消

不过,源同步设计导致时钟域数量的显著增加。这引入了时序约束和分析的复杂性,如现场可编程设备具有有限时钟缓冲的门阵列(FPGA),以及必须定制设计每个时钟树的专用集成电路(ASIC)。这个问题在大型并行总线上更加严重,因为电路板设计的限制常常迫使每个数据总线使用多个转发时钟。因此,32位总线可能需要4个,甚至8个转发时钟。

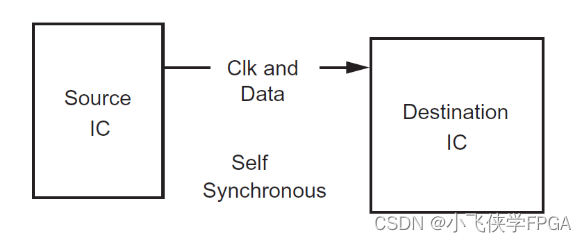

还有一种自同步的模式:

它一数据线带着时钟奔向你,相对自同步来说,它不需要那么多的时钟线了,随之而来的时钟复制也不需要。但比特率变动时需要额外的手段来纠正。如果数据包含相当多的连续零或连续一,那么可能出现失同步的情况。此外,在传输中,噪声或者干扰可能会导致误码。

这些问题,GTX的设计都给出了解决方案,具体的怎么解决的还说不太清楚,以后有机会再更吧。

怎么用呢

XILINX把使用它的流程做的非常简单:

配置IP核->生成相应的例程->更改部分程序满足自己的需求。

它也给了相关的文档pg168,但读的时候还是有点吃力,看懂它的介绍可能需要一些背景知识,偶尔能看懂一点又觉得零零散散的。所以写了开头的那两篇文章,先用起来再说,之后再去看官方文档就会比较顺畅了。