热门标签

热门文章

- 1走向大模型、大算力、大数据:特斯拉与毫末的自动驾驶AI路径寻踪

- 2android淡入淡出动画_在Android中淡入动画示例

- 3机器学习全解 - 集成学习&Adaboost(含算法讲解,公式全解,手写代码实现,调包实现)_机器学习adbost代码实现

- 4hive2.3.7安装部署-问题:show databases;没反应_showdatabases没反应

- 5本科论文查重会检测AI辅写疑似度吗?_本科论文查aigc吗

- 6实验-产生式系统(python)_实验关键步骤1.根据已知的数据建立数据库,存储植物个体(玫瑰、荷花、仙人球、

- 7NGINX编译启用SSL_nginx编译ssl

- 8我把大模型接入微信了!!!_微信客服接入大模型怎么办

- 9大一萌新の作品:红外寻迹模块做跟随小车之没有I的极简PID算法_红外循迹小车pid算法

- 10BEV经典之作Lift, Splat, Shoot解析_lift splat shoot

当前位置: article > 正文

FPGA在校学习记录系列---新建一个FPGA工程编写程序并仿真(Verilog HDL)

作者:从前慢现在也慢 | 2024-05-24 10:05:19

赞

踩

FPGA在校学习记录系列---新建一个FPGA工程编写程序并仿真(Verilog HDL)

此系列记录FPGA在学校的学习过程。

FPGA系列

需要用到的软硬件:

软件:

硬件:

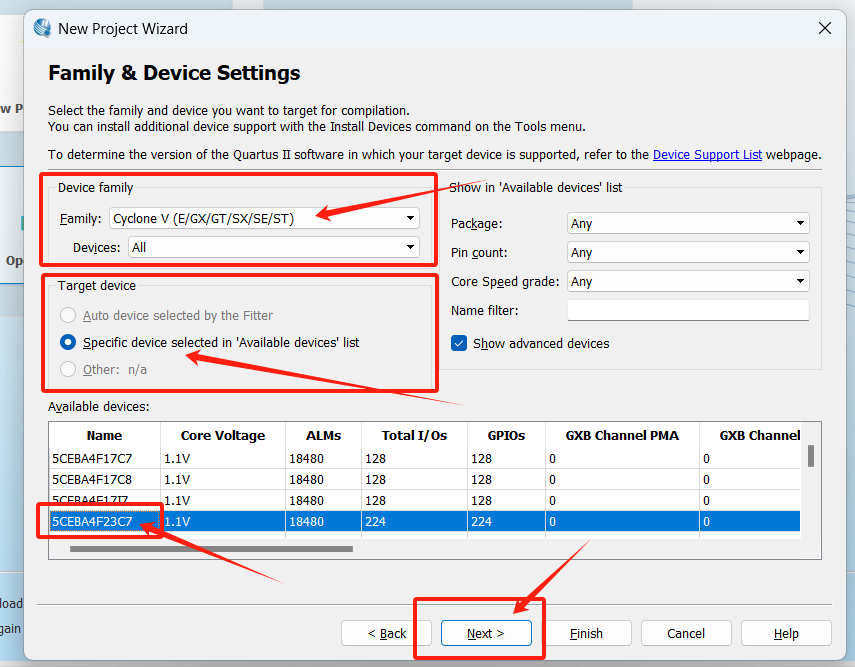

5CEBA4F23C7芯片

开始新建一个工程

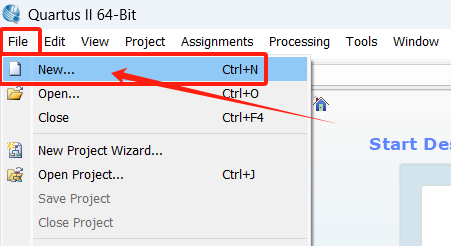

首先打开FPGA的软件

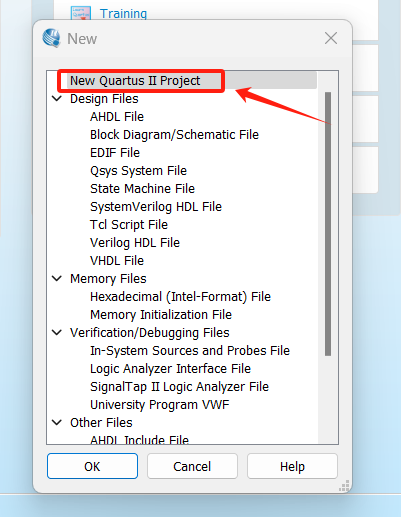

双击“New Quartus II Project”

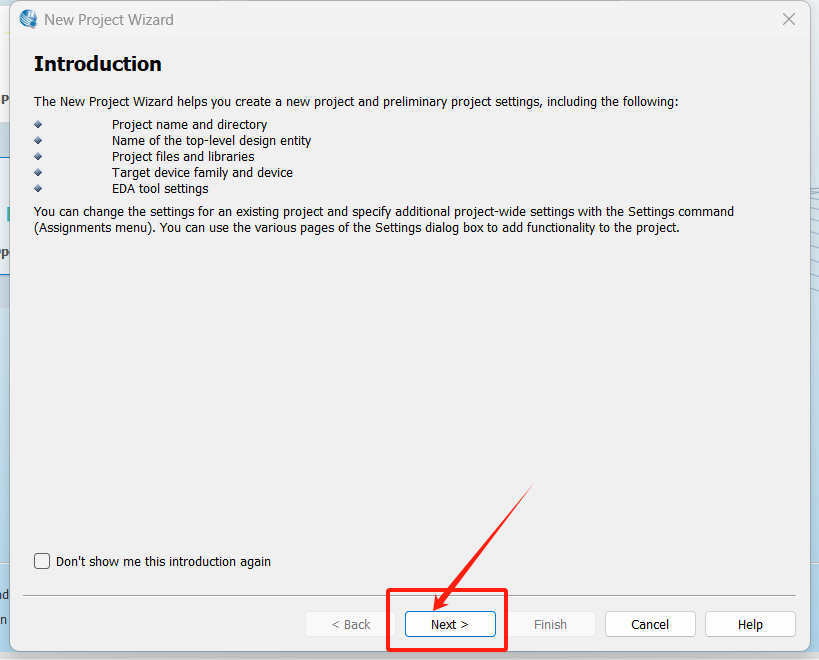

“NEXT”

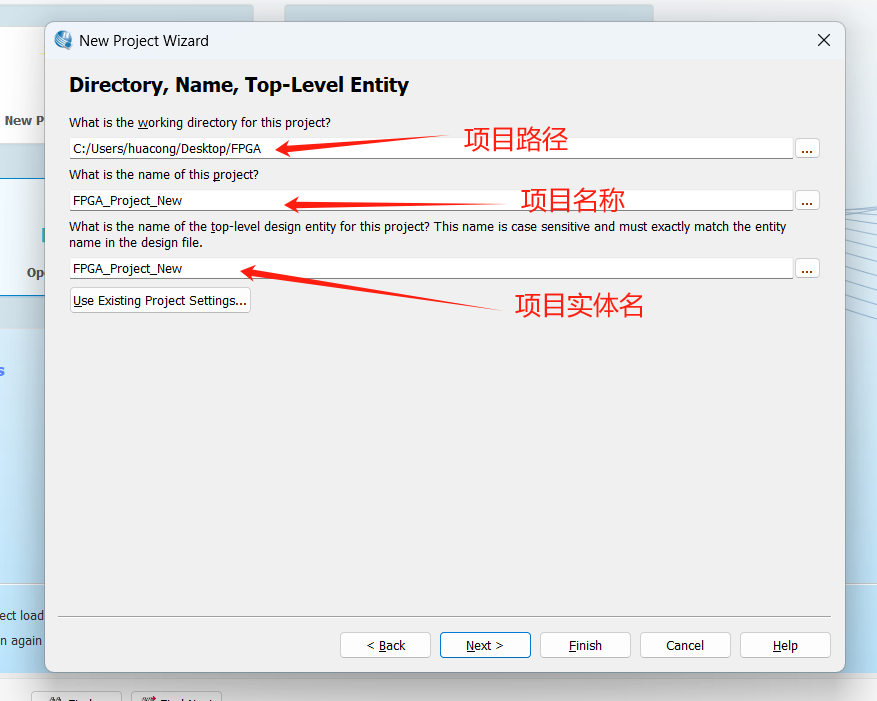

填入项目路径,名称,实体名

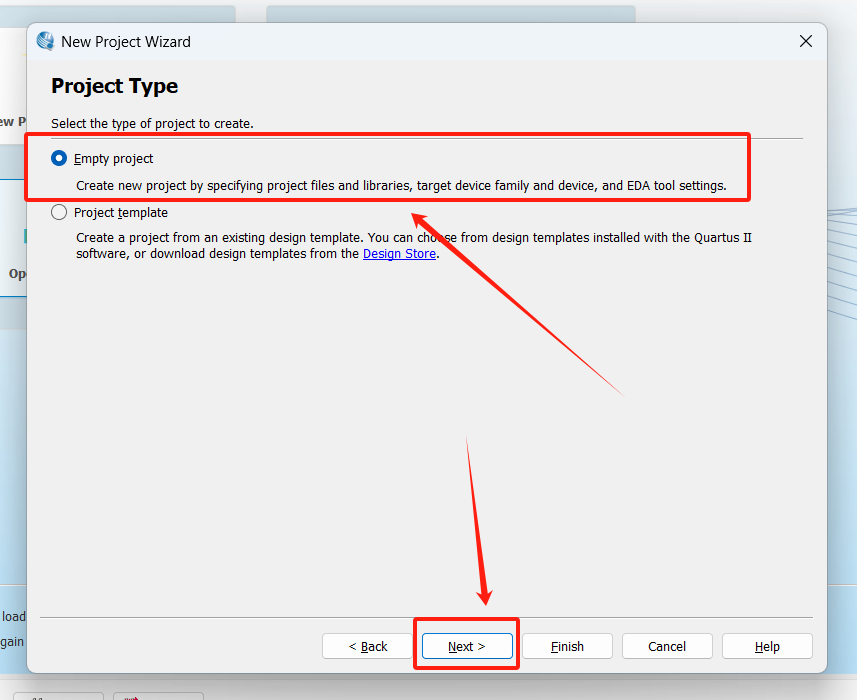

创建一个空项目

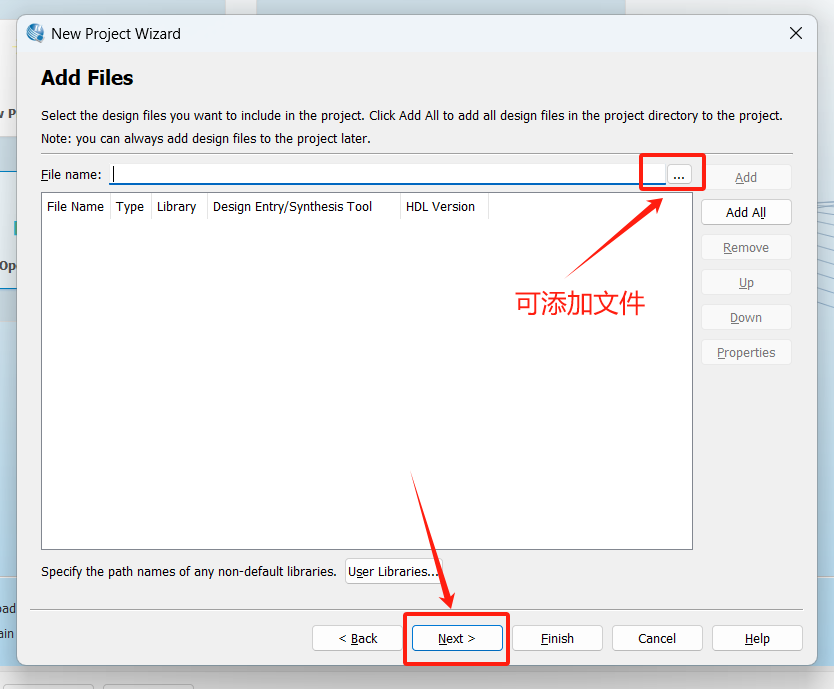

可以添加文件,但是我们暂时不添加

开始选择开发板上的芯片

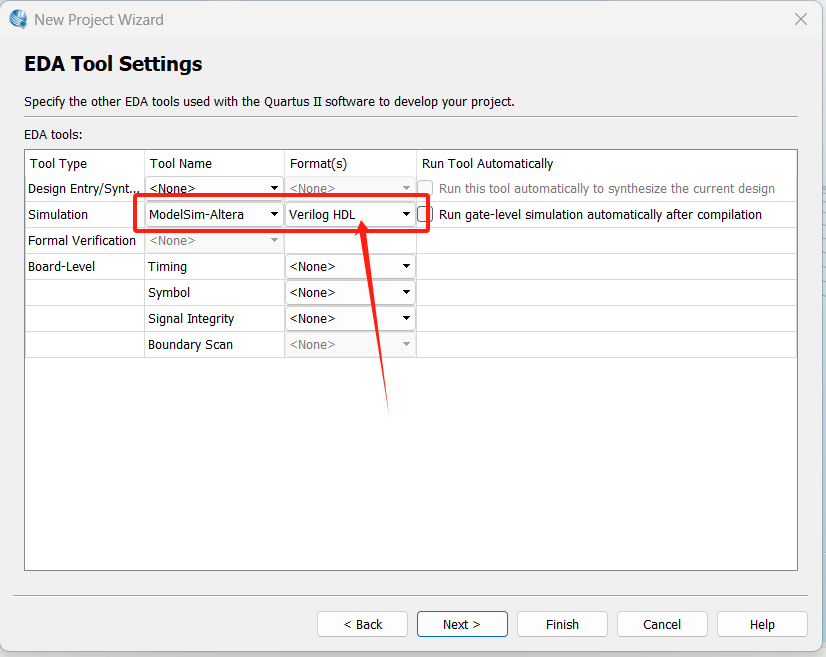

这里使用的是Verilog HDL语言

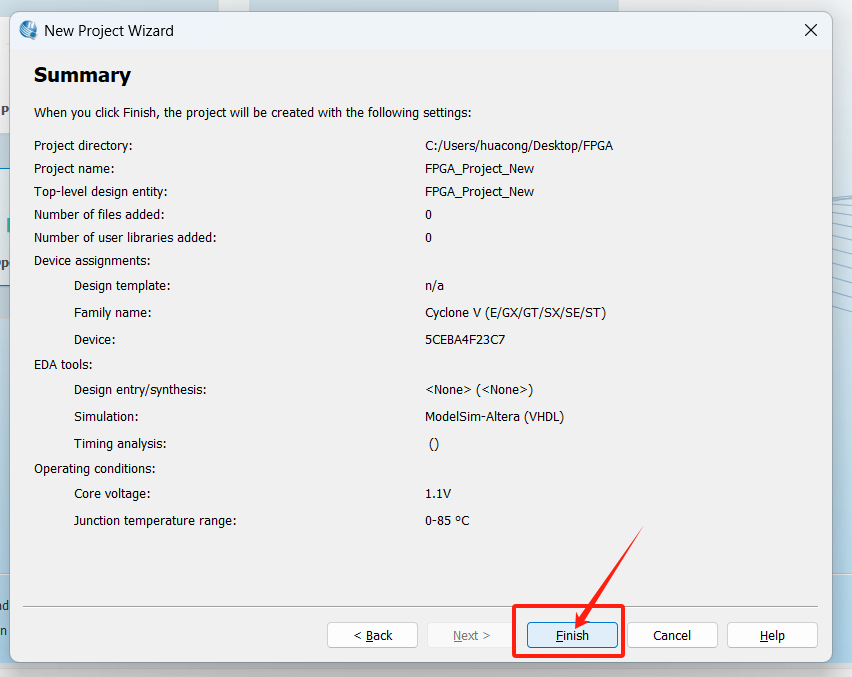

Finsh,完成创建

创建Verilog HDL文件(.V文件)

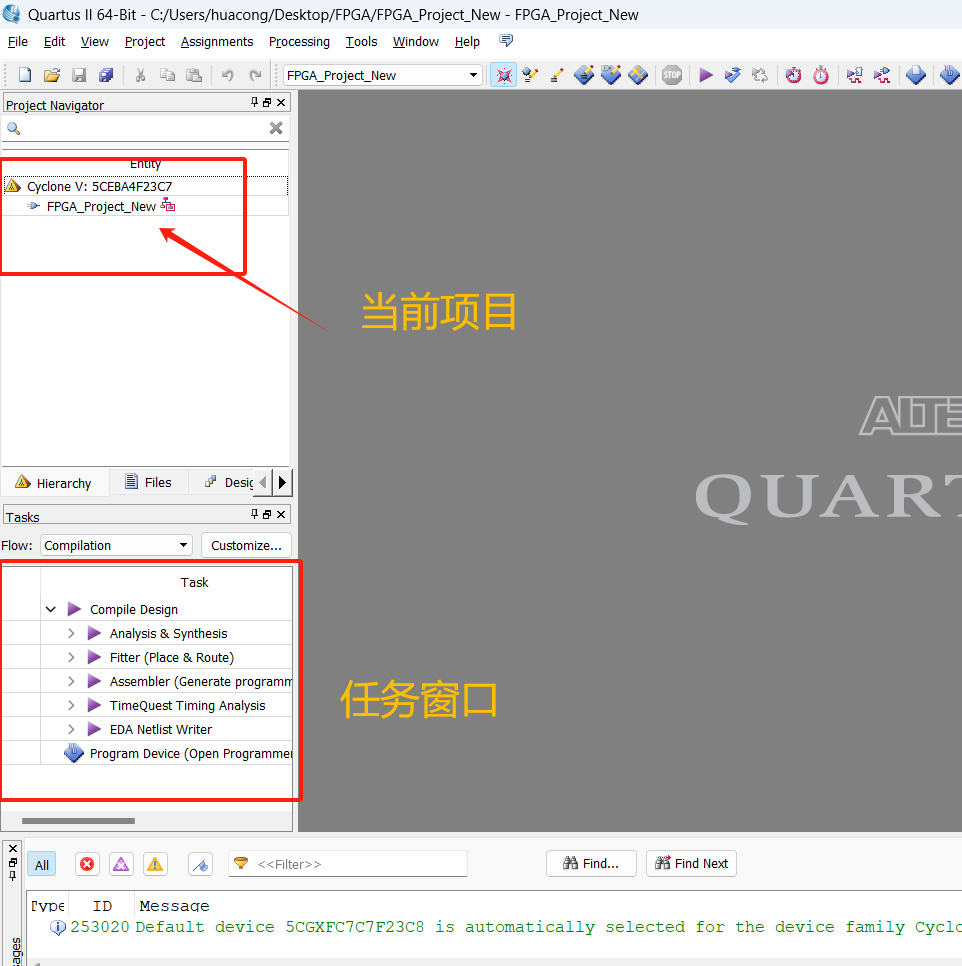

1.窗口界面

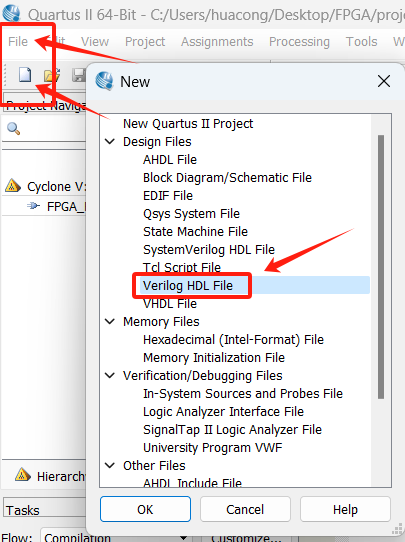

2.开始新建一个.v空白文件

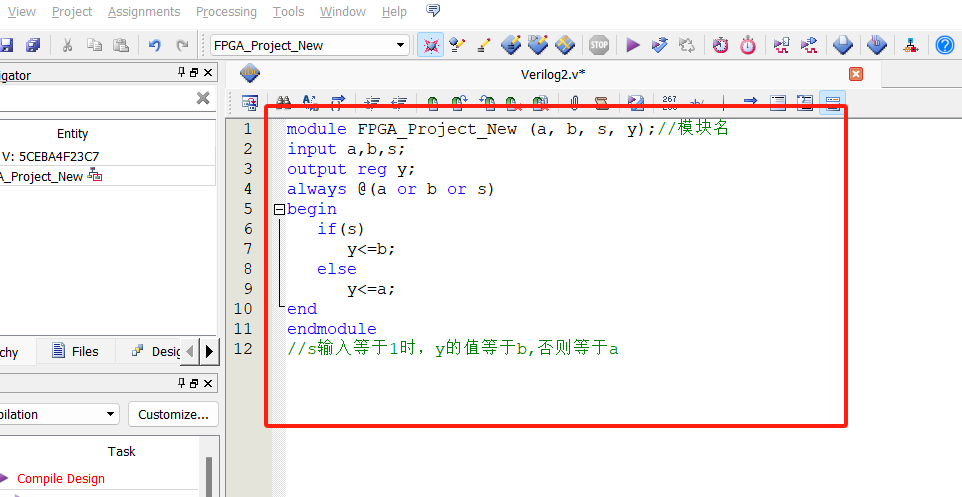

在新建的文件里面添加测试程序

//FPGA 使用:Verilog HDL语言

module FPGA_Project_New (a, b, s, y);//模块名

input a,b,s;

output reg y;

always @(a or b or s)

begin

if(s)

y<=b;

else

y<=a;

end

endmodule

//s输入等于1时,y的值等于b,否则等于a

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

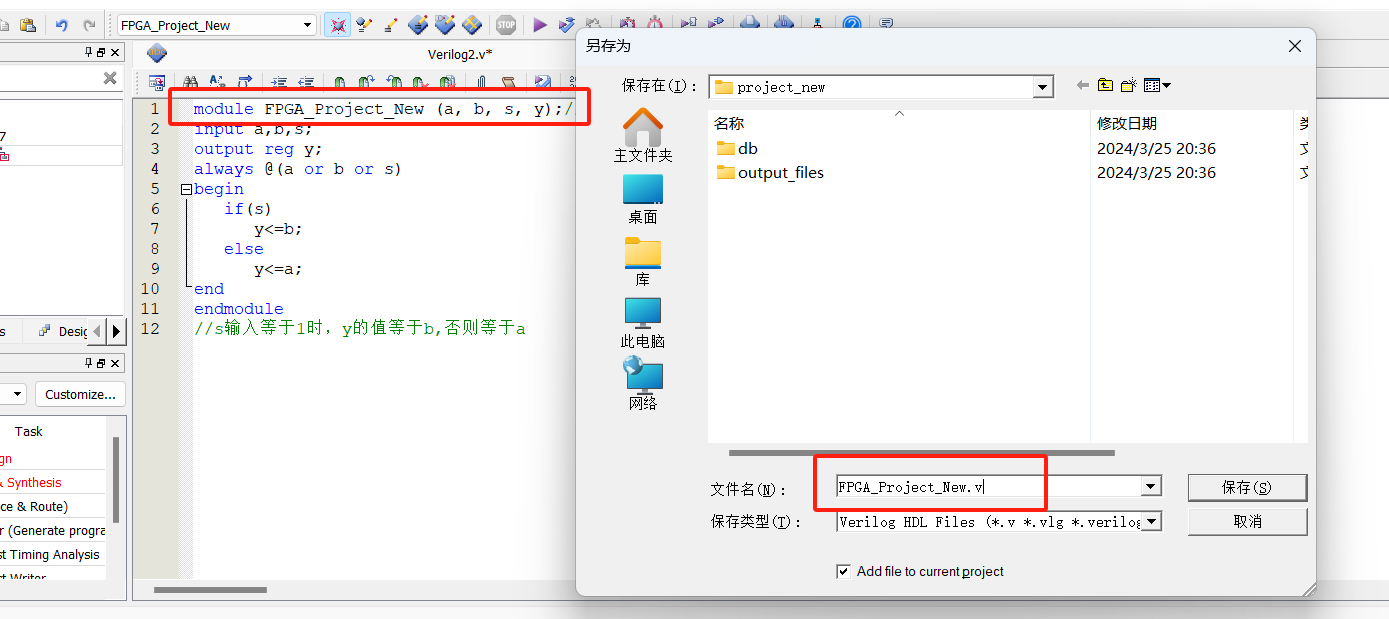

保存一下,名字要和模块名一样

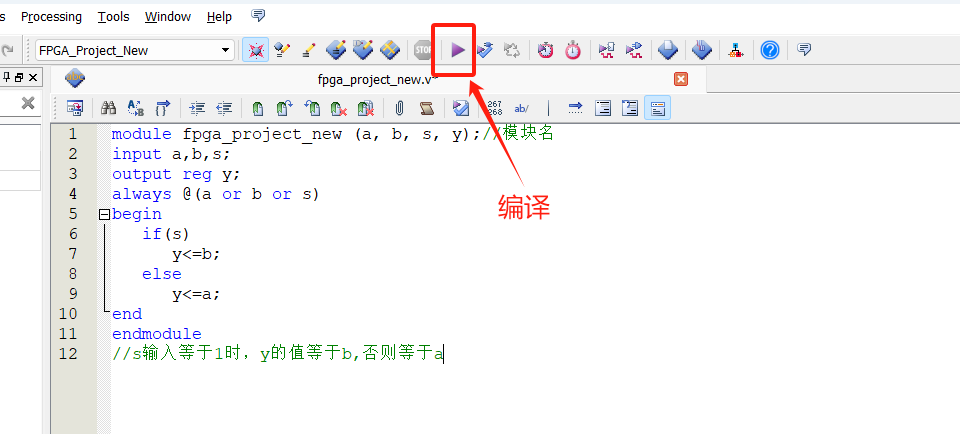

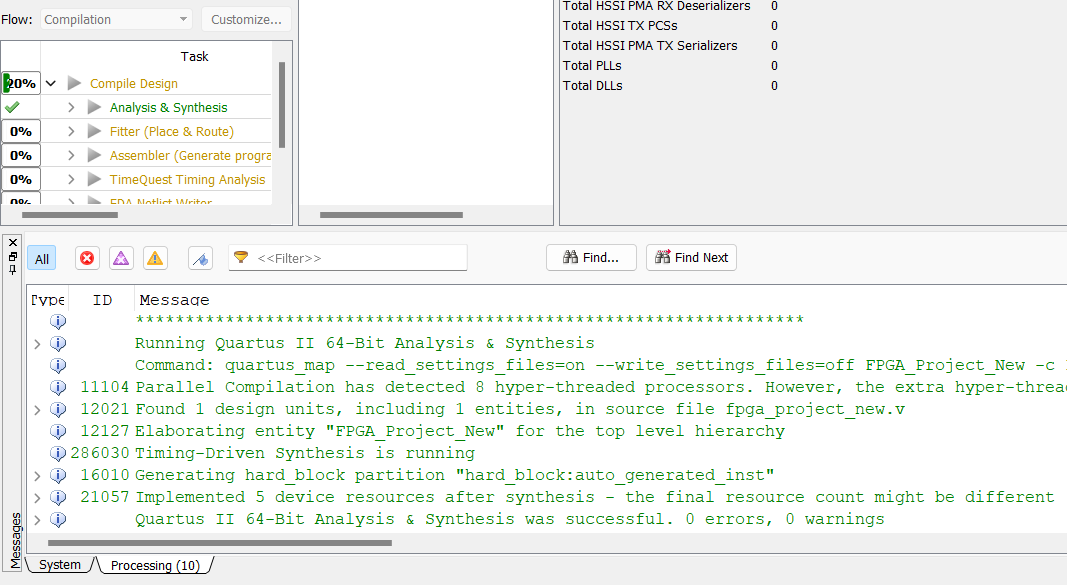

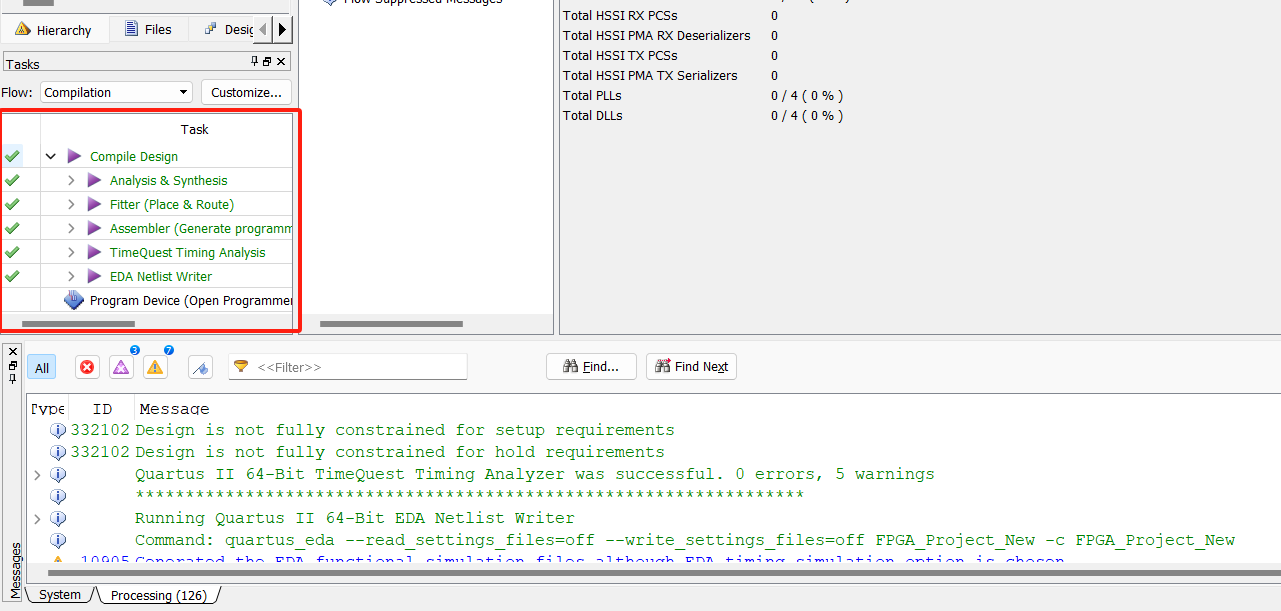

编译

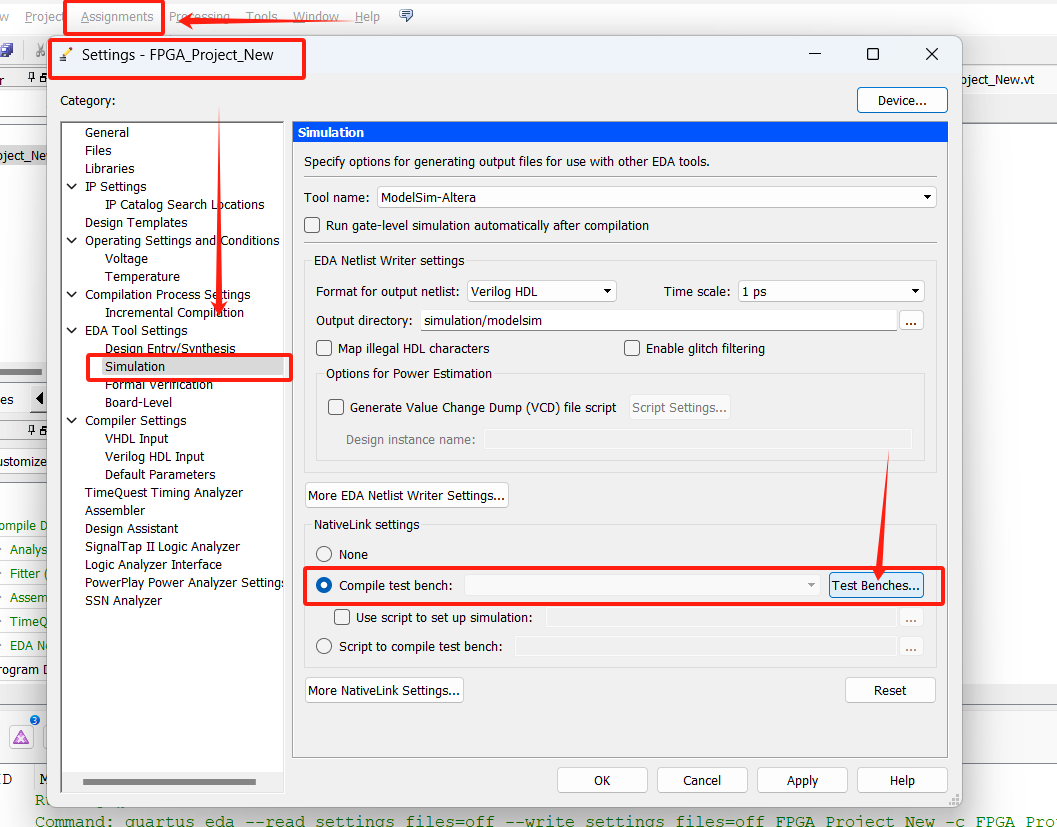

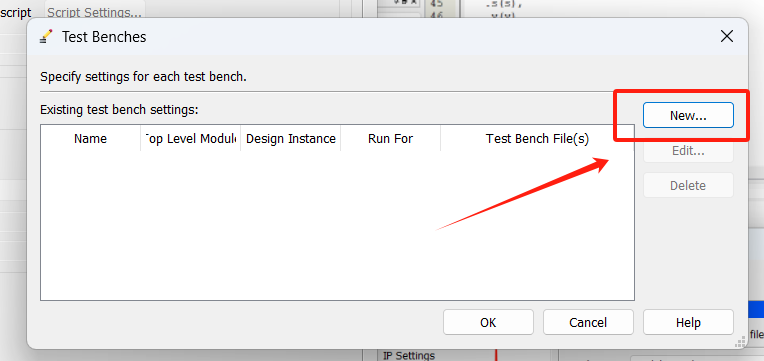

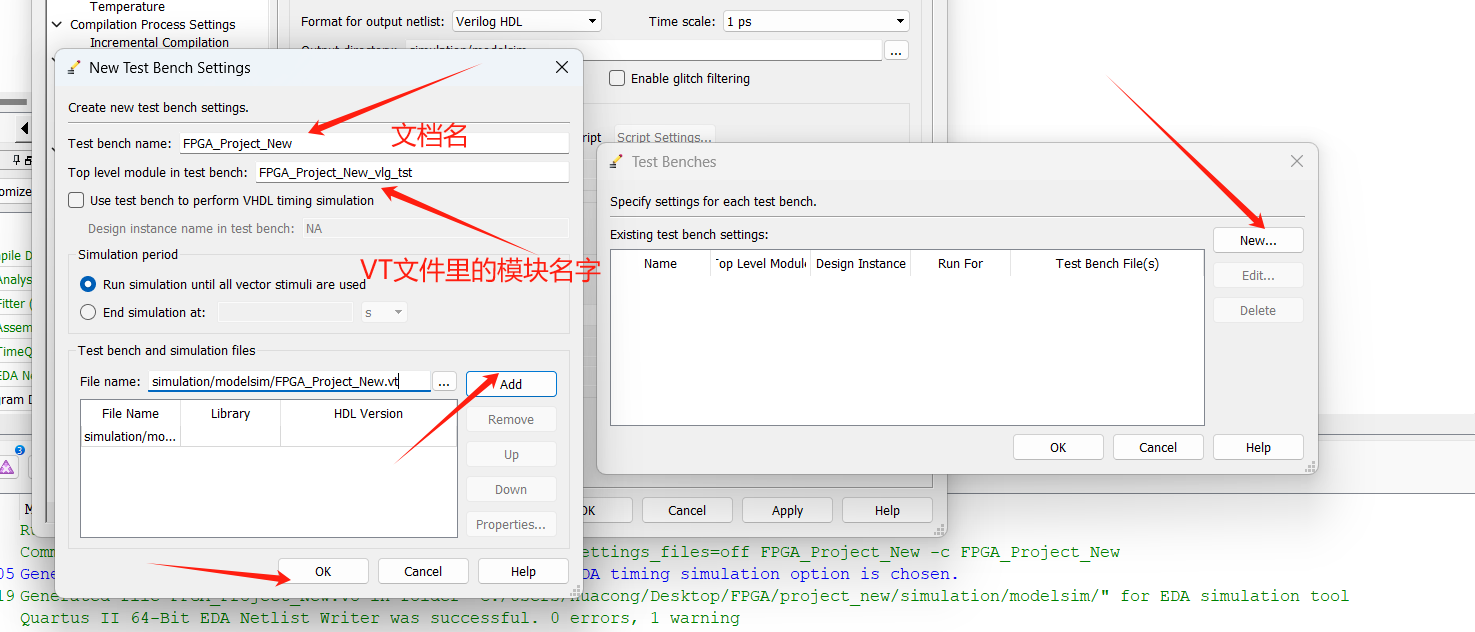

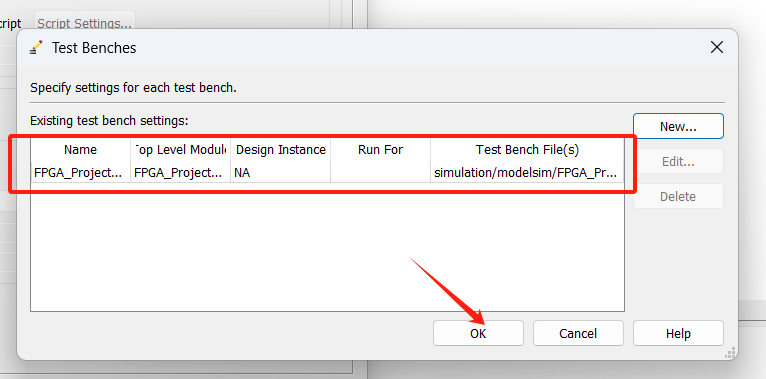

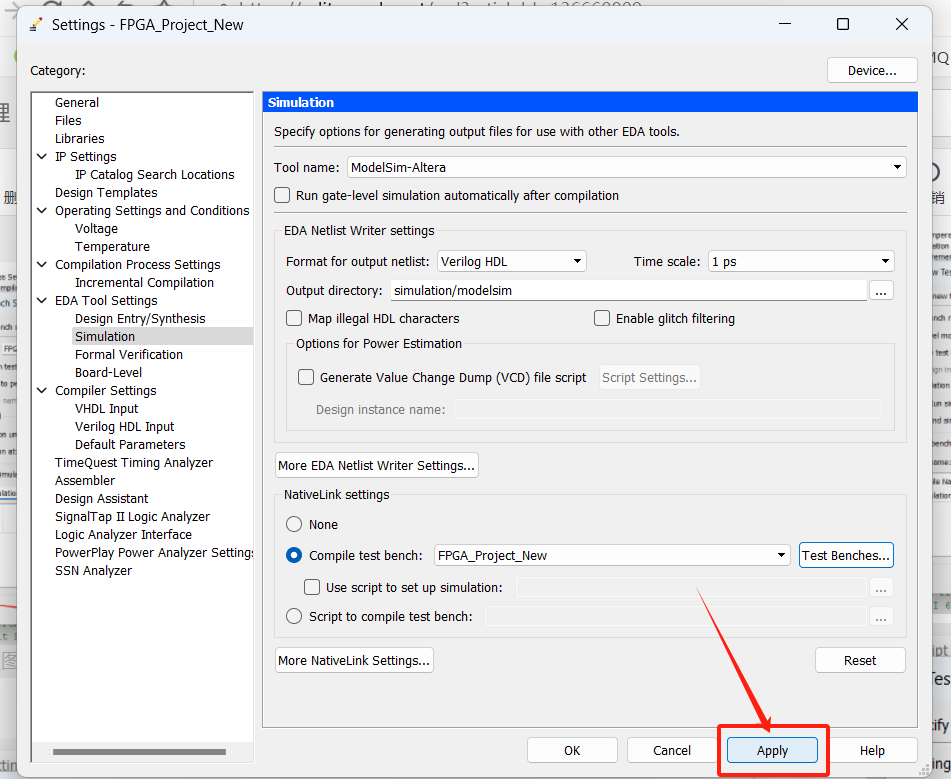

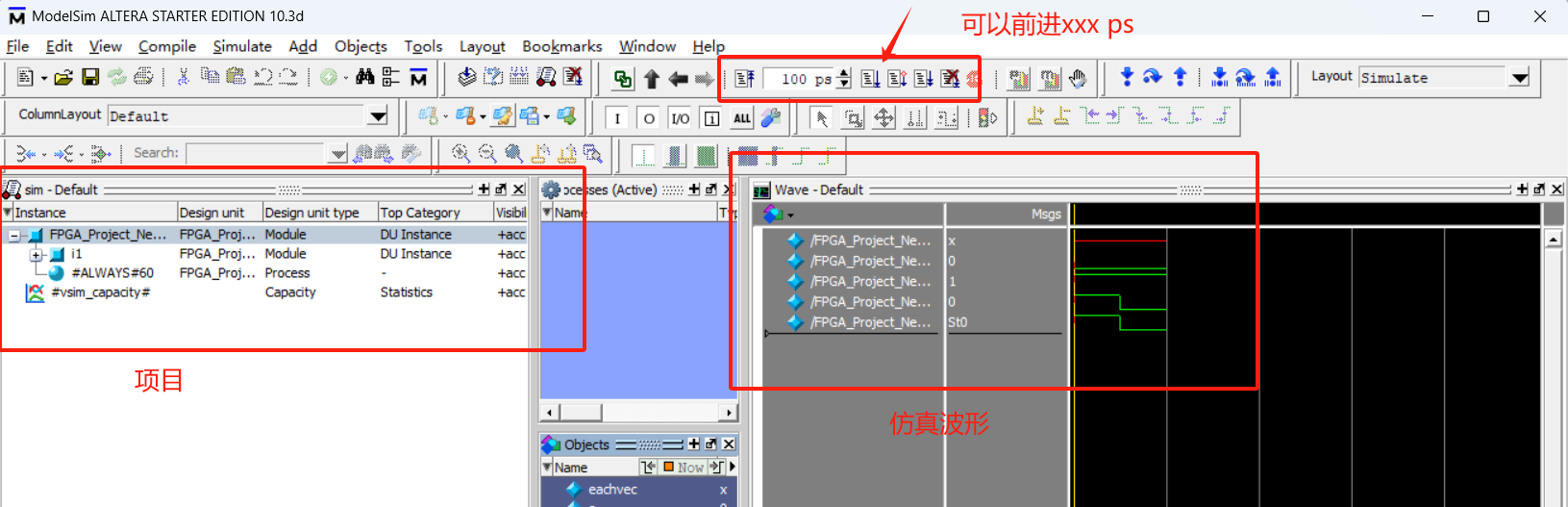

仿真

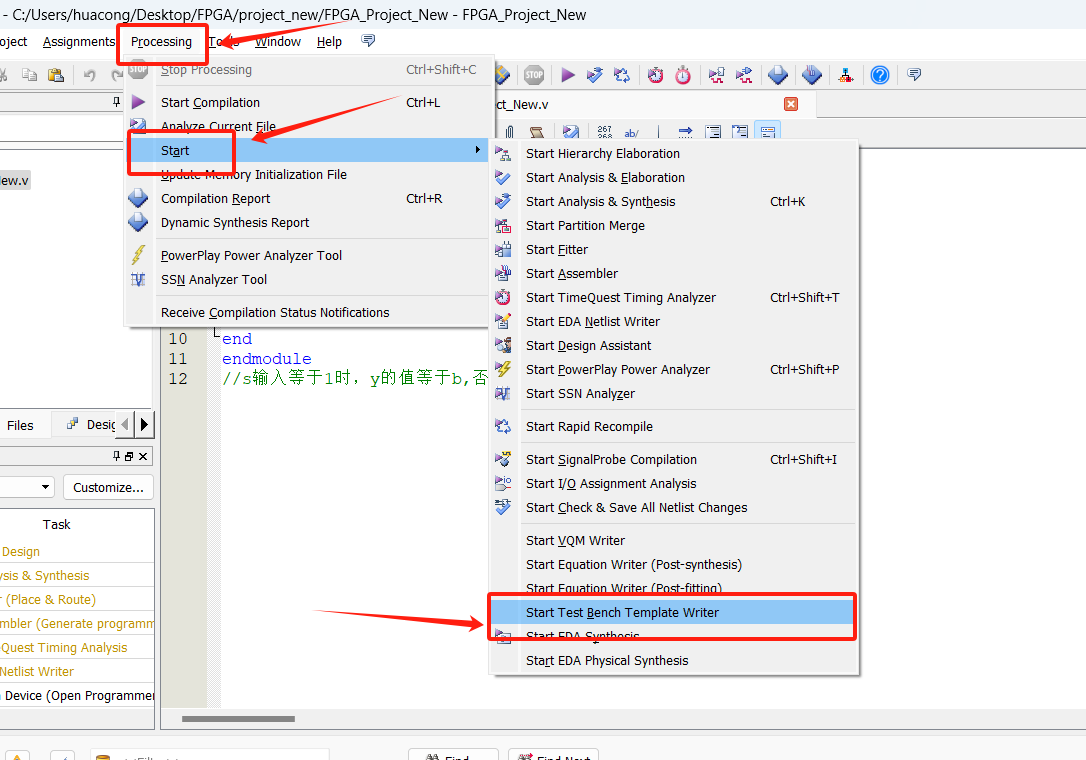

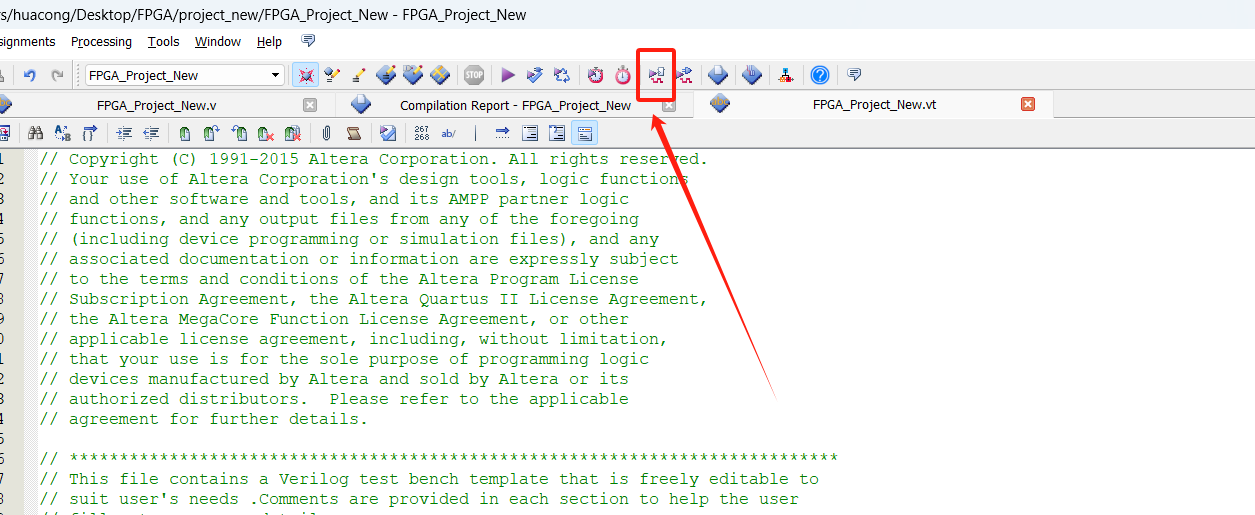

1.生成.VT仿真文件

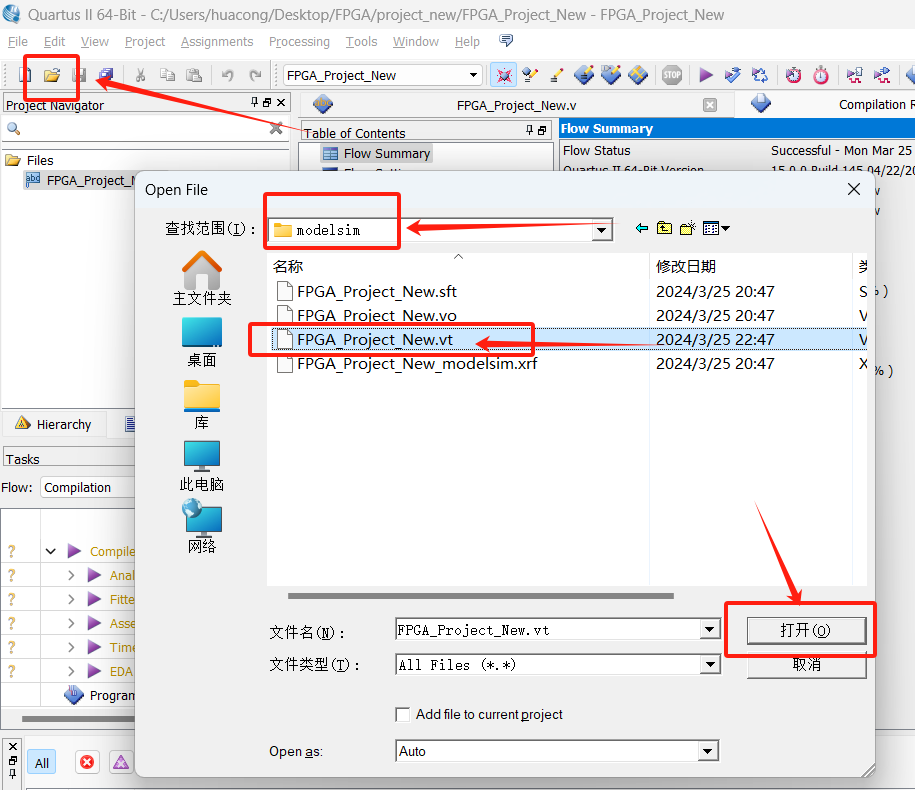

可以在文件夹找到生成的.vt文件(文件类别选全部可以看见)

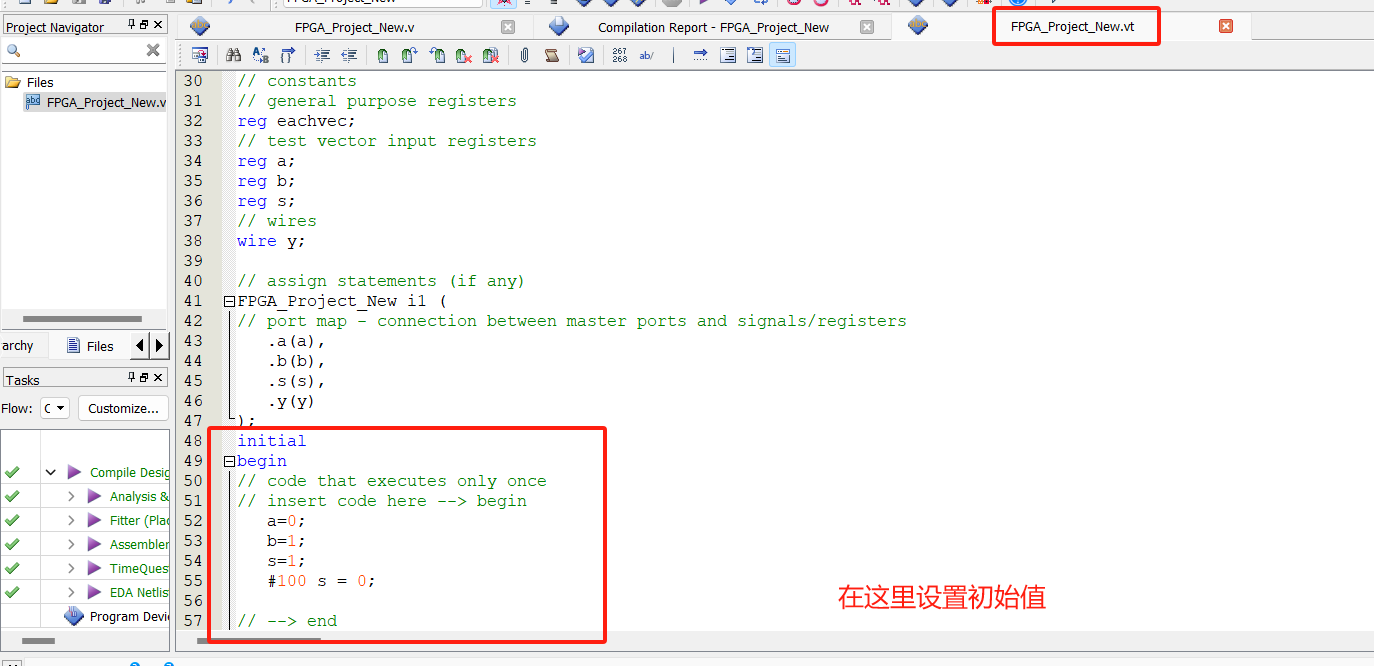

2.设置初始值并仿真

咱们可以设置初始值

initial

begin

// code that executes only once

// insert code here --> begin

a=0;

b=1;

s=1;

#100 s = 0;

// --> end

$display("Running testbench");

end

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

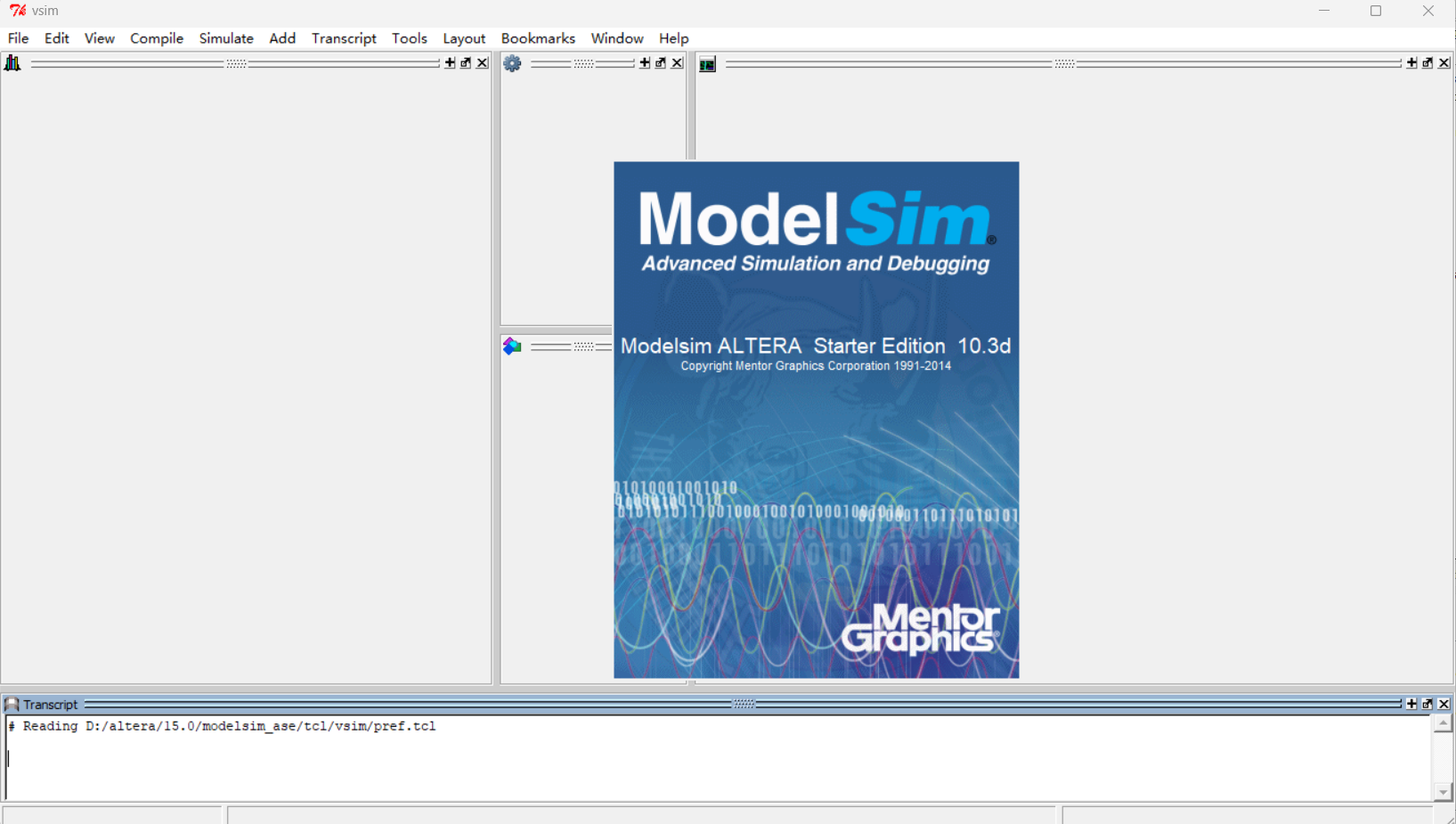

打开后自动弹出

总结

有一些坑要踩过才知道,所以一定要实际操作一次

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/从前慢现在也慢/article/detail/616952

推荐阅读

相关标签