热门标签

热门文章

- 1[大模型]DeepSeek-MoE-16b-chat Transformers 部署调用_deepseek本地部署

- 2浅谈驱动开发_驱动开发是干什么的

- 3AVM 环视拼接方法介绍_avm拼接算法

- 4鸿蒙OpenHarmony【轻量系统 编译】 (基于Hi3861开发板)_openharmony hb

- 5Android 中的动态应用程序图标_android 动态更新icon

- 6概率模拟(sigmoid、softmax)

- 7开源机器学习模型管理工具DVC介绍_算法模型版本管理服务

- 8十分钟带你认识大模型和生成式AI和其常见误解_生成式ai与大模型

- 9GO语言与C++语言的区别主要体现在什么地方?可以举个简单的例子说明吗?

- 10ROS2从入门到精通5-1:详解代价地图与costmap插件编写(以距离场ESDF为例)_ros costmap

当前位置: article > 正文

vivado进行管脚约束(详细教程)_vivado管脚约束

作者:从前慢现在也慢 | 2024-07-09 11:37:37

赞

踩

vivado管脚约束

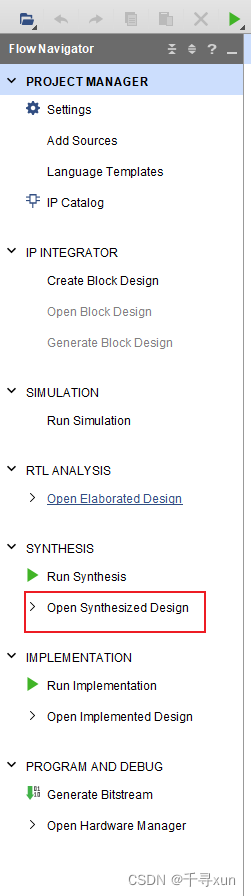

1、图形化界面

工程编译通过后,点击

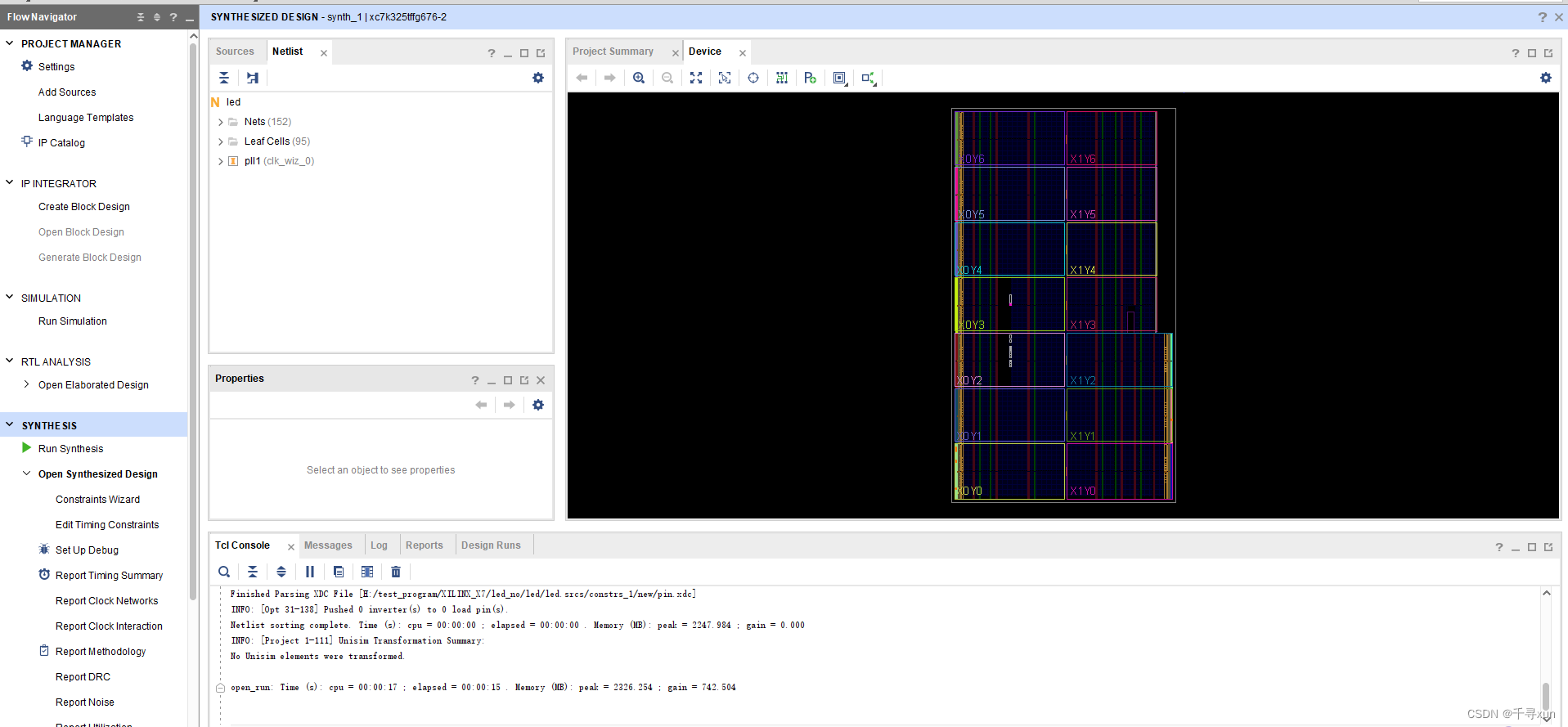

打开后长这样:

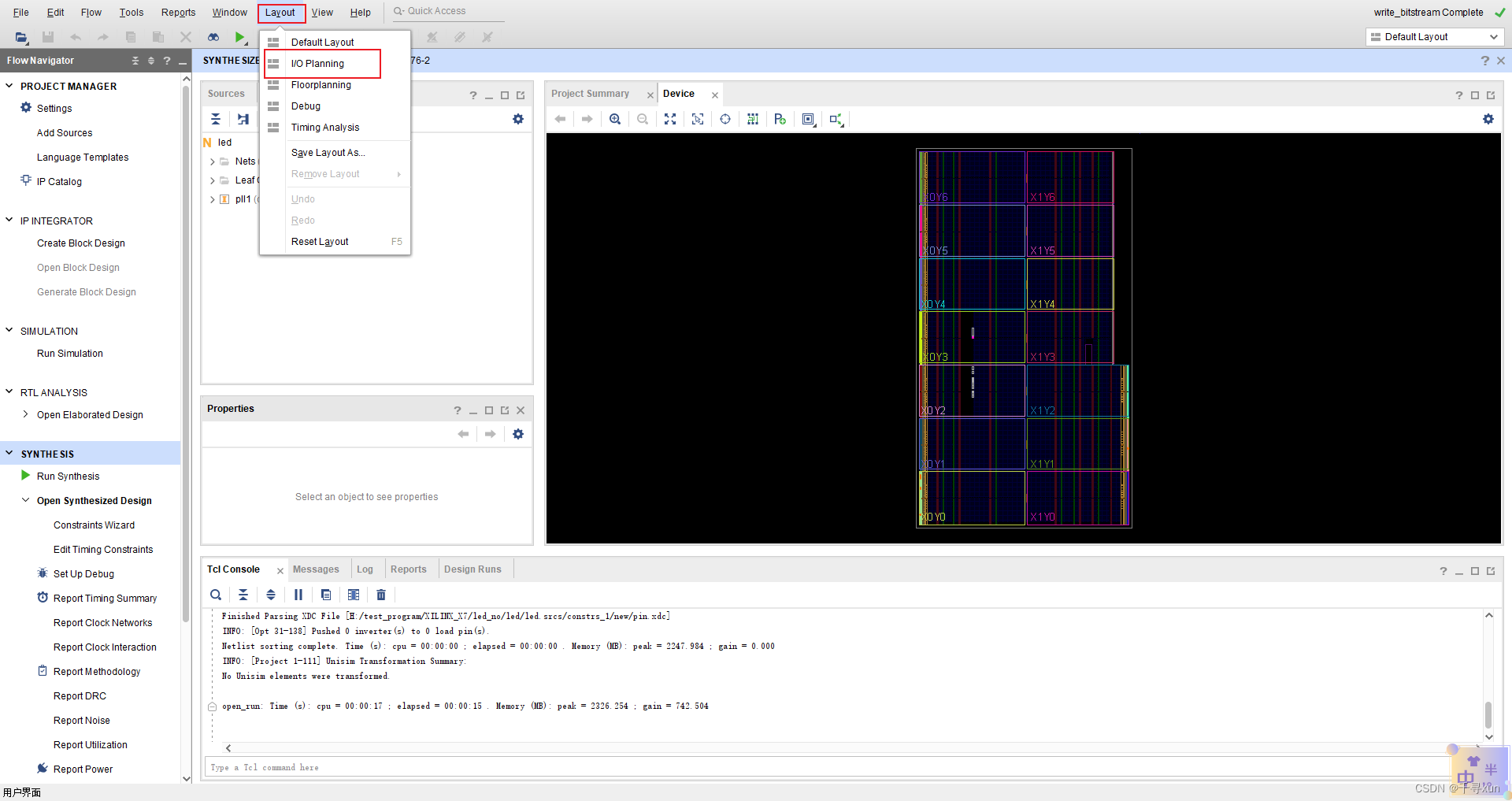

点击layout 选择IO planning:

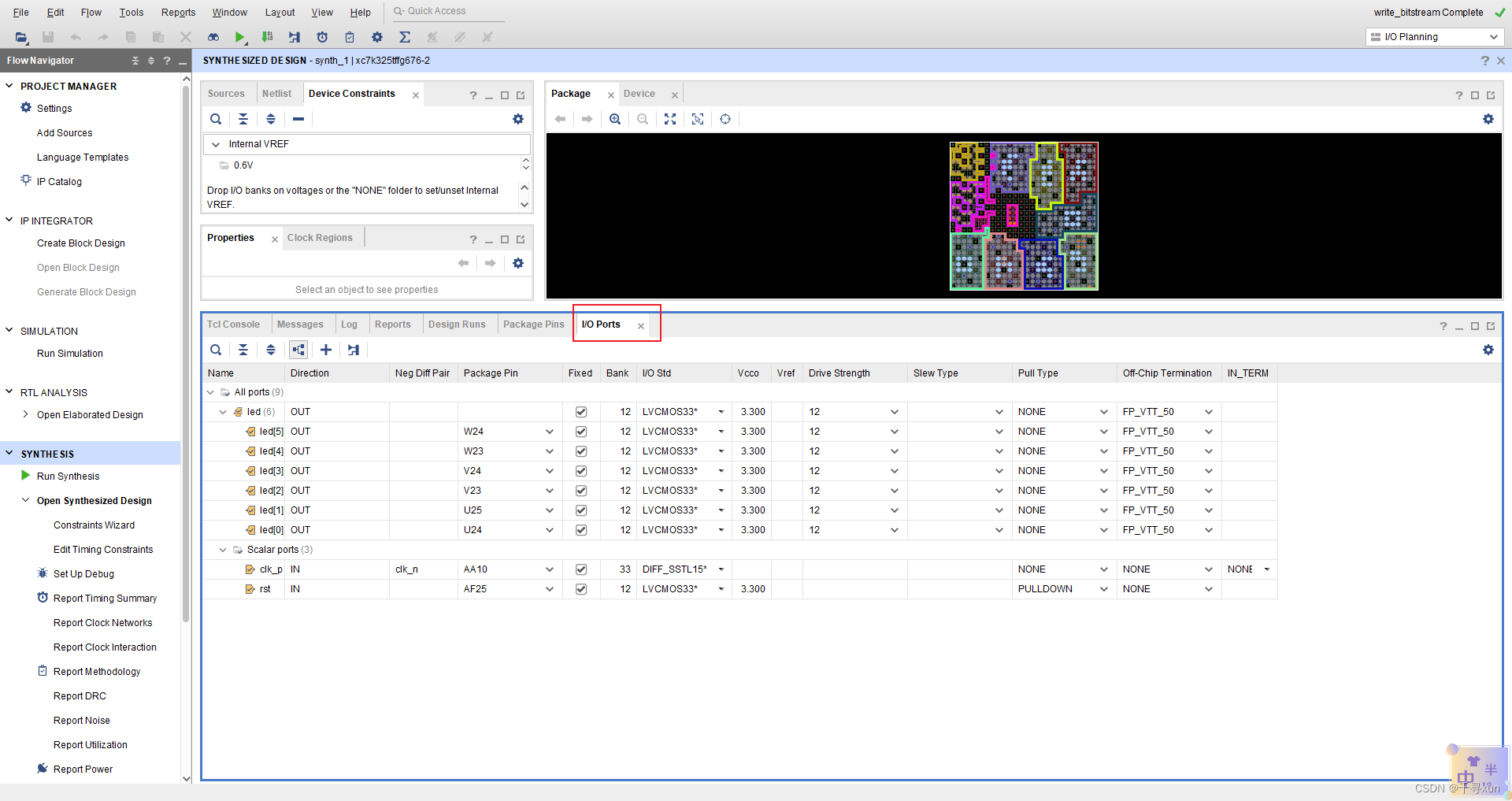

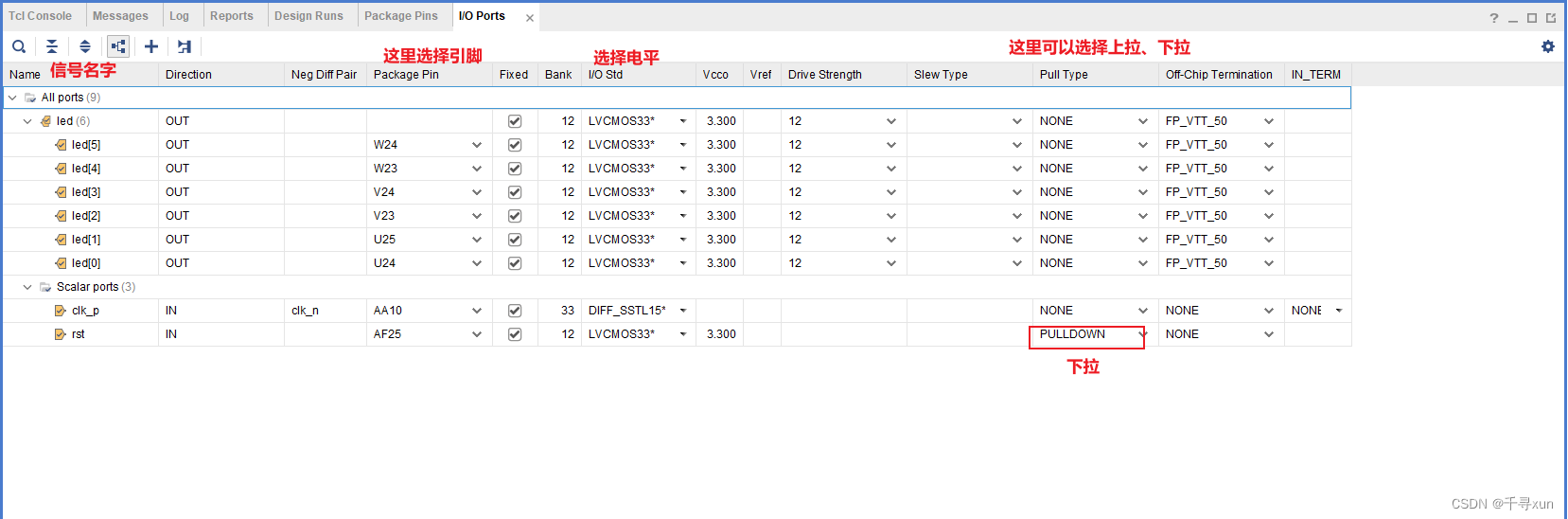

点击IO port进行管脚定义:

说明

设置好保存。

2、直接使用代码定义

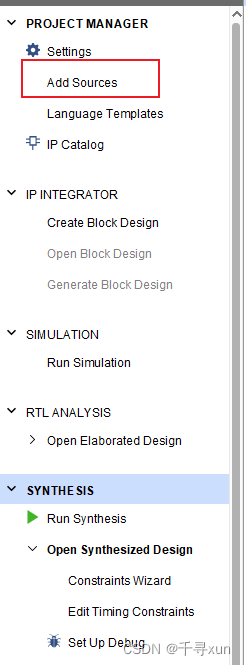

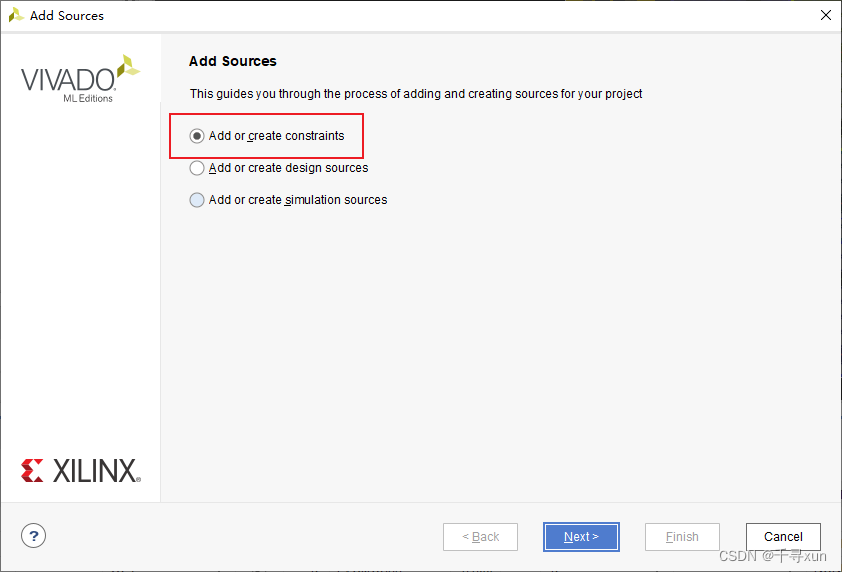

添加约束文件

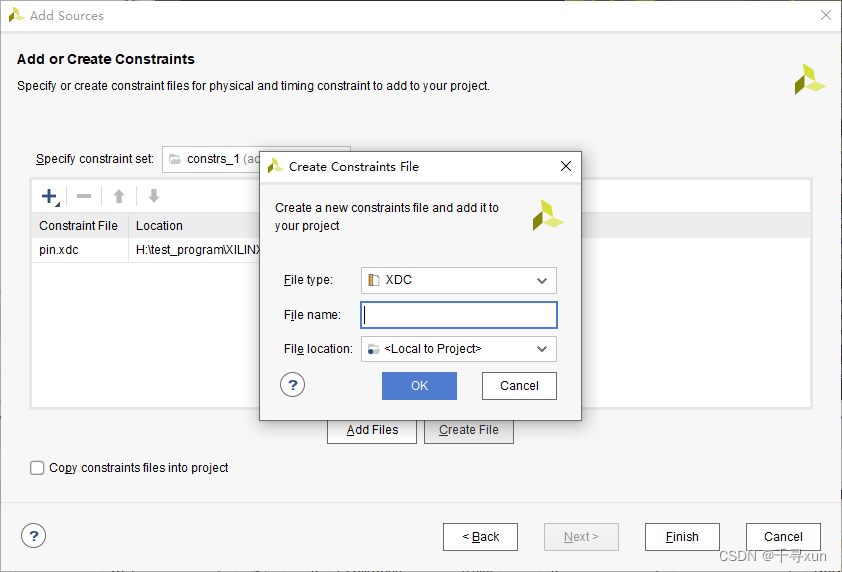

新建XDC文件

新建好后打开:

添加以下代码:

set_property PACKAGE_PIN AF25 [get_ports rst]

将信号名rst绑定AF25引脚,其他信号同理

set_property IOSTANDARD LVCMOS33 [get_ports rst]

将信号名rst电平定义为LVCMOS33,就是3.3v电平

set_property PULLDOWN true [get_ports rst]

将信号名rst下拉,非必须。上拉PULLUP

约束好保存编译即可。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/从前慢现在也慢/article/detail/802289

推荐阅读

相关标签