- 1yolov5模型部署到web端,识别返回json格式文件_yolov5 输出图片识别结果json

- 2Bean的作用域中prototype原型模式(浅拷贝和深拷贝)_bean prototype

- 3html固定在页面底部,css中页脚如何固定在底部?

- 4监督学习和无监督学习的基本概念及作用-机器学习知识点

- 5java搭建阿里云服务器环境(java环境+mysql+tomcat)和部署 JavaWeb 项目到云服务器(十分详细)_tomcat+mysql的项目迁移到移动云上

- 62021-11-22 (atcoder)_atcoder预测分

- 7ES(elasticsearch)搜索引擎 结合java 使用_es搜索引擎java使用

- 8Kafka简单总结_kafka-console-producer.sh --broker-list

- 9计算机视觉所需要的数学基础

- 10Docker、Docker file、Docker-compose 详解_docker file docker compose

FPGA时序分析与约束(13)——I/O接口约束_fpgaio接口

赞

踩

一、概述

在应用了时钟约束后,所有寄存器到寄存器的路径都能定时。为了获得更加精准的FPGA外部时序信息,设计者需要为FPGA的I/O接口指定时序信息,一般时序工具只能获取FPGA器件内部的时序信息,对于FPGA器件引脚之外的时序信息,必须由设计者约束定义。如果没有指定的输入输出的,时序分析工具会假设在接口上使用最优时序要求并假设电路单元的组合逻辑本身具有整个周期,电路单元外部没有信号。

二、输入有效

2.0 输入有效

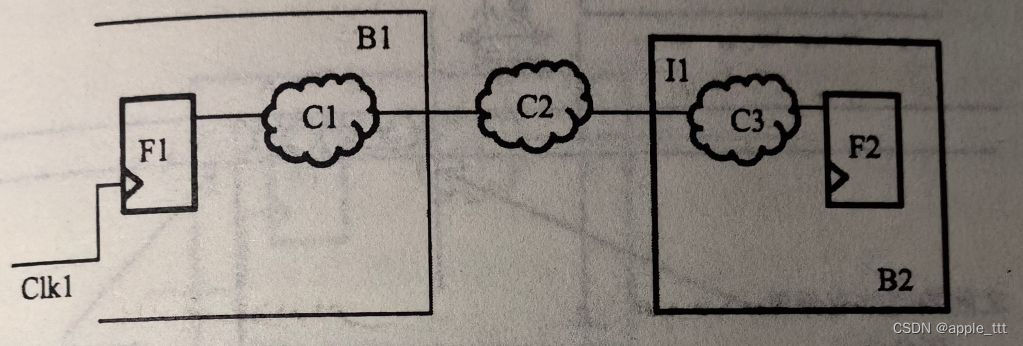

我们需要为每个输入端口指定输入有效时间,考虑如下的一个电路图:

对于电路单元B1,我们需要知道信号到达I1的时间。

这个到达时间可以告诉实现工具在组合逻辑云C1(输入端口和第一个寄存器元器件之间)中花费的时间,反过来,到达时间也决定了要求优化的等级。如果信号没有按时达到F1(通过组合逻辑后的第一个寄存器)并被及时锁定,那么它将允许STA工具发送报告。思考如下图电路的情况:

对于电路单元B2,需要指定输入I1的输入到达时间。当触发器由一个时钟触发时,信号从F1(前一个电路单元B1的F1)开始。这个时钟触发就充当了参考事件,参考事件产生后,信号通过线路经过触发器(Clk_to_Q延迟)、组合逻辑C1(在前一个电路单元B1中)、组合逻辑C2(在顶层中)和互连延迟。但是,如果考虑了I1的信号到达时间,那么延迟在C1、C2、Clk_to_Q、互连线等之间如何分配就不那么重要了。我们只需要知道参考事件在发生后经过多久到达现在的输入端口。

2.1 最小和最大有效时间

这个话题在之前的文章中已经多次提到过了,这里再简单说明一下,在输入端口,设计者需要指定信号可以改变的最早时间、这也就是最小时间,在这个时间之前,输入信号不能到达输入输入端口。由此可以确定,输入端口的上一个值要保持到这个时间。最小时间可以保证输入信号不违反后级电路的保持时间要求。

设计者还需要指定最大时间,在这个时间内,要确保输入端口上的输入信号有效。这个时间也是最迟时间,在这个时间内,输入端口上信号的所有变化都是有效的。最大时间用于确保满足后级电路的建立要求。

2.2 多时钟

有的时候,一个输入信号可能由多个时钟触发,如下图所示:

到达I1的信号可能从Clk1(电路单元B)处产生,也可能从Clk2(电路单元B2)处产生。两个触发事件可能相互独立。在这种情况下,到达事件会根据两个参考事件来指定。实现工具和STA工具会考虑每个到达时间,并同时满足在两个条件。

三、输出要求

3.0 输出要求

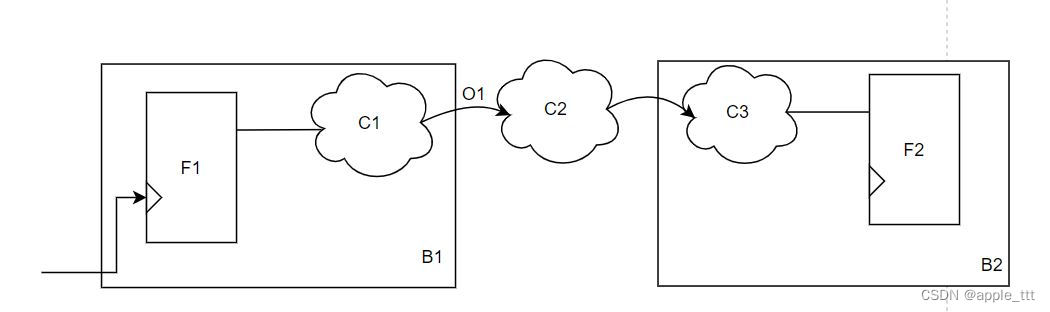

对于每个输出端口,都需要指定信号被采样前,在电路单元外部经过的时间。电路如下图所示:

对于电路单元B1来说,我们需要知道产生输出O1后,在采样前信号需要的传输时间。

实现工具可以通过这个时间计算出应该在逻辑云C1(最后一个寄存器元件F1和输出端口O1之间)放置多少逻辑。STA工具也可以通过这个时间报告在某个时间O1上信号是否有效,这样在产生输出O1后,就有足够的时间经过电路单元的外部,如下图所示:

对于电路单元B1,需要为输出O1指定输出要求时间(output required time)。O1输出后,信后由电路单元B2中的触发器F2采样。触发器F2的时钟起到了参考事件的作用。在参考事件到达F2之前,信号经过组合逻辑C2(在顶层中)、组合逻辑C3(在下一个电路单元中)存在延迟和互连延迟。信号需要在参考事件之前到达F2,这样触发器才能满足建立要求。但是,只要考虑了在O1处的信号输出要求时间,那么延迟在C2、C3、F2的建立时间和互连线之间是如何分配的就不重要了。我们只需要知道参考时间之前在输出端口处信号有效需要多长时间。在O1外的时间越多意味着逻辑云C1(寄存器与输出端口之间)的延迟越小。

输出要求时间是根据信号采样之前,在电路单元外需要的时间来确定的,而不是根据输出端信号有效时间来确定的。输出要求时间可以通过计算得出。例如,如果输出延迟为6ns,这意味着信号输出后需要6ns。如果一个时钟触发器在10ns时对信号进行采样,那么意味着信号需要在4ns时有效。在SDC中,用户指定6,即输出后需要的时间时6ns。信号应该什么时间有效可以通过计算获得。这就是输入延迟和输出延迟在概念上的不同。在输入端,指定的输入延迟直接给定了输入有效时间。在输出端,指定的输出延迟是信号进一步传输需要的时间。输出延迟不同于输出信号的有效时间。

3.1 最小和最大要求时间

有时候,在输出端不太能指定信号在输出后需要传输的精确时间,例如,从输出端到相同参考事件可能有多条路径时。但是,我们还是要求设计者尽可能给出信号输出后需要传输的最小时间和输出信号从输出出来后需要传输的最大时间。

3.2 多个参考事件

有时候,输出信号可以被多个参考事件捕获,电路图如下所示:

从O1出来的信号可以被Clk1捕获,也可以被Clk2捕获。这两个捕获事件可以是独立的。在这种情况下,要求时间根据两个参考事件来指定。这是实现工具和STA工具的功能,它们独立计算每个要求时间并满足每个要求。

四、set_input_delay

在输入端口指定延迟的SDC命令是set_input_delay。命令的BNF如下:

- set_input_dalay [-clock clock_name]

- [-clock_fall]

- [-level_sensitive]

- [-rise]

- [-fall]

- [-max]

- [-min]

- [-add_delay]

- [-network_latency_included]

- [-source_latency_included]

- delay_value port_pin_list

4.1 时钟规格

-clock 选项用于指定参考时钟,根据参考时钟指定延迟时间,这个选项通常指的是触发器输入端信号的时钟名称。

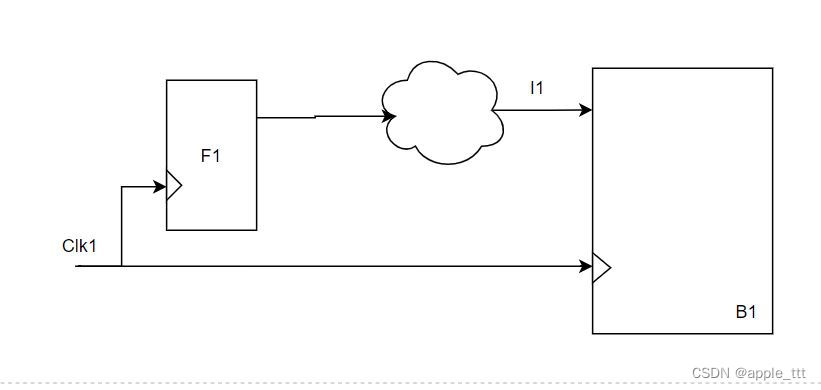

假设电路单元B1的输入I1由触发器F1驱动,它也可以在其他电路单元中,还可以是顶层逻辑的一部分。假设触发F1的时钟还可以进入电路单元B1,B1的时钟名称是Clk1。在这种情况下,clock_name的规格应该指定为Clk1。这个时钟触发输入的到达时间,同时这个时钟也是参考事件。当驱动F1时,时钟信号的名称相同也没有关系。例如,可以把包含F1的时钟信号命名为CLK_1,但是,对于B1的输入延迟,时钟的名称还需指定以便对B1可见。

有时候,触发F1的时钟信号可能不会进入电路单元B1,在这种情况下,需要为B1声明虚拟时钟。这种虚拟时钟的特性必须与触发F1的时钟相同,这时,虚拟时钟能够使用带-clock选项的clock_name来指定。

默认情况下,输入延迟是基于时钟上升沿来指定的,但是,如果触发器F1由时钟下降沿触发,那么需要添加选项-clock_fall,这个选项可以使得参考事件是clock_name的下降沿而不是上升沿。

如果时钟周期是10ns,具有{0 5}波形,触发器F1是由时钟下降沿触发的,那么可以指定时钟下降沿的延迟是2,或者指定时钟上升沿的延迟是7。关于时序分析,下面命令具有相同的作用。

- set_input_delay -clock CLK1 -clock_fall 2.0 [get_ports I1]

- set_input_delay -clock CLK1 7.0 [get_ports I1]

但是,如果启动触发器F1是由时钟下降沿触发的,那么我们应该使用第一个命令,因为它可以很好地反映电路的设计。

如果输入引脚是组合电路唯一路径的一部分,那么就没有时钟触发到达输入引脚上的信号。这种情况下,就不需要指定-clock。对于set_input_delay命令,参考事件是时间0。如果没有指定-clock,那么-clock_fall也就没有意义。因为现在许多设计都是同步的,通常会用set_input_dalay指定时钟,组合路径(即使存在)也可以使用其他约束方式来约束。

4.2 -level_sensitive

如果启动元器件不是一个触发器而是一个锁存器,那么就应该指定这个开关。从概念上讲,使用这个开关后启动锁存器可以借用这个周期里的时间。这意味着建立裕度(setup slack)会减少——这考虑了当锁存器为透明信号从锁存器开始的情况。

但是,这个选项应该谨慎使用。不同工具对这个选项的处理方式不同,一些工具和转换器会简单地忽略这个选项。如果设计者想使用这个选项,那么应该保证在整个过程中使用所有工具处理这个选项时都使用同一种方法。

4.3 rise/fall 限定符

-rise 用于限定输入延迟与输入端口信号的上升沿对应。-fall用于限定输入延迟与输入端口的下降沿对应。如果在输入端口信号上升或下降时的输入到达时间不同,那么这个命令需要提供rise或者fall限定符。

当不指定限定符 rise 或者 fall 时,给定值适用于这两种过渡。在CMOS电路中,上升和下降过渡时的路径延迟非常相似,所以不会经常使用 -rise/fall 规格。

4.4 min/max限定符

-min 用于限定指定的延迟值与输入端口信号的最早到达时间到达对应。这个值用在当前设计内部以保持检查。-max 用于限定指定的延迟值与输入端口信号的最迟到达时间对应。这个值用于在当前设计内部以实现建立检查。

当不使用-min/max限定符时,两个限定符使用相同的设定值。通常不使用-min/-max 限定符,其值与指定的最大延迟相同。

目前随着纳米技术的发展,单个触发器的保持值大幅下降,在某种程度上可以说降低了很多。很显然,因为在数据路径上的延迟有限,所以会出现输入到达时间为正,保持时间为负的情况,即使保持值不是负值,也会与“零”非常接近,因此,在大部分情况下,通过启动元器件的延迟(启动触发器的Clk_to_q延迟)和互连延迟将比保持时间长,因此,大部分情况下外部到达信号都能满足保持要求。通常,使用最大值可以可靠完成建立检查。这个值也用于保持检查,无论如何必须满足保持检查。如果信号将输入到一个保持要求很大元器件中,那么保持检查就很重要,如内存。这种情况下,也应该正确指定-min值。

4.5 -add_delay

许多时序分析工具都为用户提供了交互shell,用户使用这些shell可以修改上述指定值。当指定端口的输入延迟时,在这个端口上最新的规格就会覆盖前面的规格。如果用户必须在同一个端口指定多个参考事件的输入延迟,那么所有后续规格就需要指定-add_delay。

4.6 时钟延迟

我们知道,在触发触发器之前,时钟在路径上会有延迟(时钟源延迟和网络延迟),我们可以通过开关-source_latency_included 和 -network_latency_included 来进行约束。

4.7 完成输入延迟约束

要完成输入约束,现在就剩下唯一的工作就是需要指定输入延迟的实际端口或引脚,并且指定延迟值,这是set_input_delay 命令必须指定的两个选项。

五、set_output_delay

用于指定输出端口延迟的SDC命令是set_output_delay。命令的BNF是如下:

- set_output_dalay [-clock clock_name]

- [-clock_fall]

- [-level_sensitive]

- [-rise]

- [-fall]

- [-max]

- [-min]

- [-add_delay]

- [-network_latency_included]

- [-source_latency_included]

- delay_value port_pin_list

从概念上讲,set_output_delay和set_input_delay两个命令非常相似,所以这里不会像之前那样一一展开,仅对两个命令不同的部分详细说明。

set_input_delay 和 set_output_delay 的根本区别在于:输入延迟是指到达输入端的时间,即在输入端信号有效的时间。另一方面,输出延迟是信号输出后还要传输的时间,这个时间与在输出端信号需要有效的时间不同。但是,从语义上讲,两个命令非常相似,它们都指定了在感兴趣的电路单元外的延迟要求。就像外部延迟需要满足要求一样,电路单元内部也有自己的时序要求。

六、小结

set_input_delay 和 set_output_delay 需要正确设定,这样,电路单元的信号就可以保证时序正确了。如果设定不正确,那么单个电路单元可能就能够满足自己的时序,而当集成整个设计时,最终的设计可能不会满足时序。