- 1MATLAB dt含义,Matlab的D算法

- 2推荐!程序员常用的15个学习交流网站_chinaunix

- 3git分支 MERGING状态_merging分支

- 4基于遗传算法的新安江模型参数优化率定(一)_python 新安江 参数率定

- 5普通学历,大一大二要不要打ACM?_acm竞赛一般大几参加

- 6git(3)Git 分支

- 7Prompt是什么_揭秘Prompt:大模型时代的关键技术与实践应用_prompt 计算机语言

- 8Apple Push Notification Services in iOS 6 Tutorial: Part 2/2_what command do you want to use to start the app?

- 9Python招聘信息爬虫数据可视化分析大屏全屏系统(Django框架) 开题报告

- 10集铁们,你Flutter打包不会是用app.apk吧?

Xilinx Aurora 64B/66B IP使用_aurora6466b

赞

踩

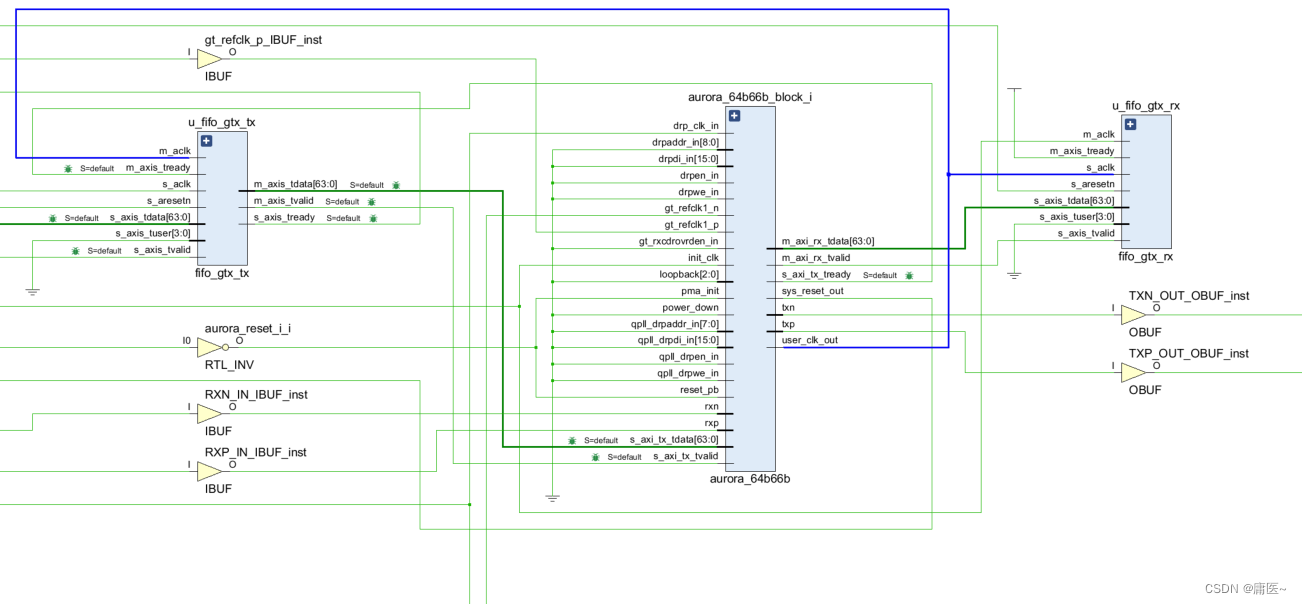

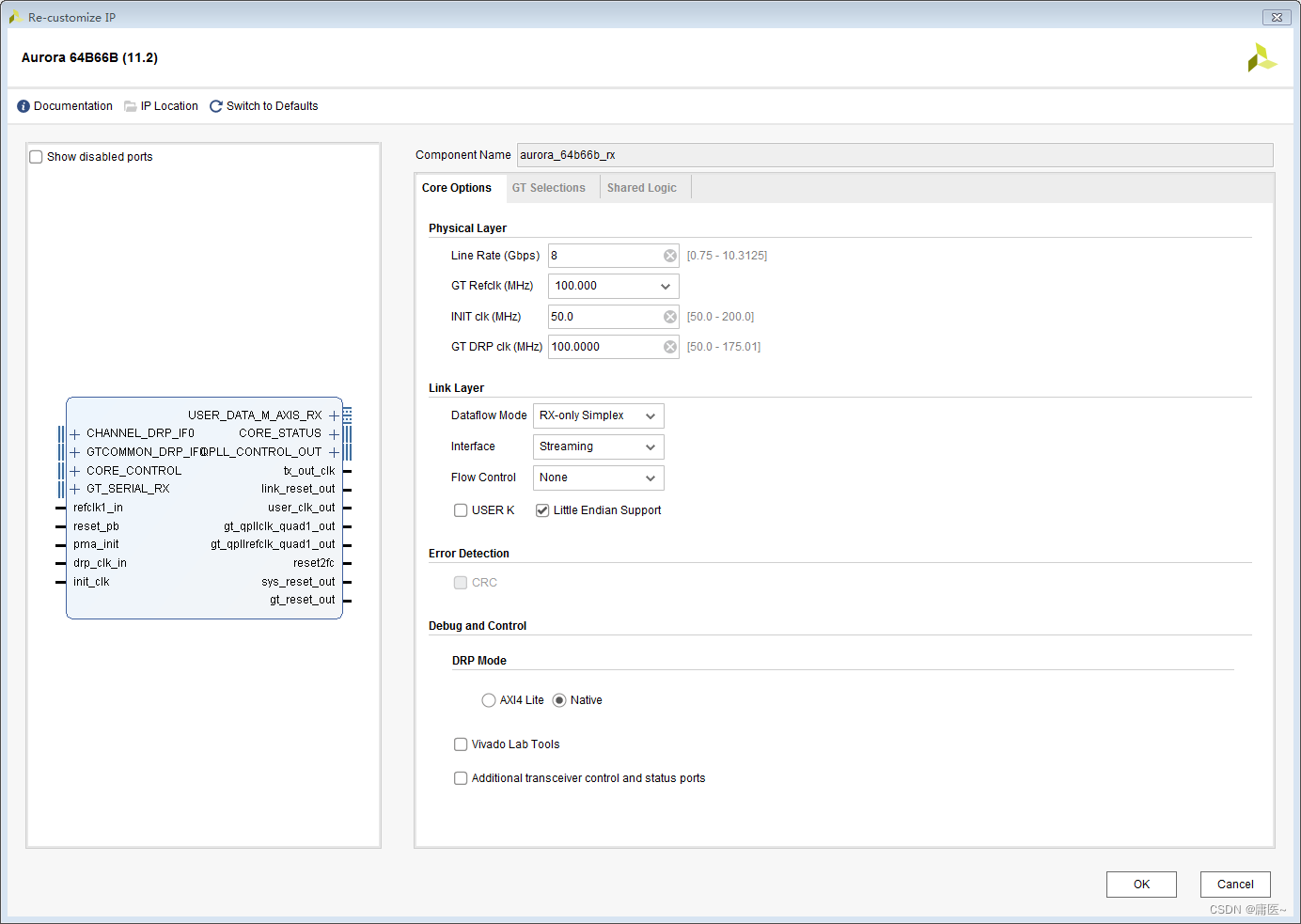

IP核配置

Aurora 64B/66B IP核的配置也比较简单,只需要对线速率和时钟进行配置,INIT clk和DRP clk是IP核内部逻辑使用,与线速率和uesr_clk无关,这两个时钟可以选择用户提供方便的时钟频率,

Link Layer进行接口的配置,datafolw模式可以选择全双工传输,半双工传输,以及单工传输。接口类型可以选择帧式接口和流式接口,可以选择是否使用流量控制功能,数据默认大端类型。也就是[0:63]的格式,可以勾选litter endian support改成常见的小端格式[63:0]。

对于Debug and control,这里的几乎用不到,不用管,为了减少IP核的接口,模式可以选用native模式,

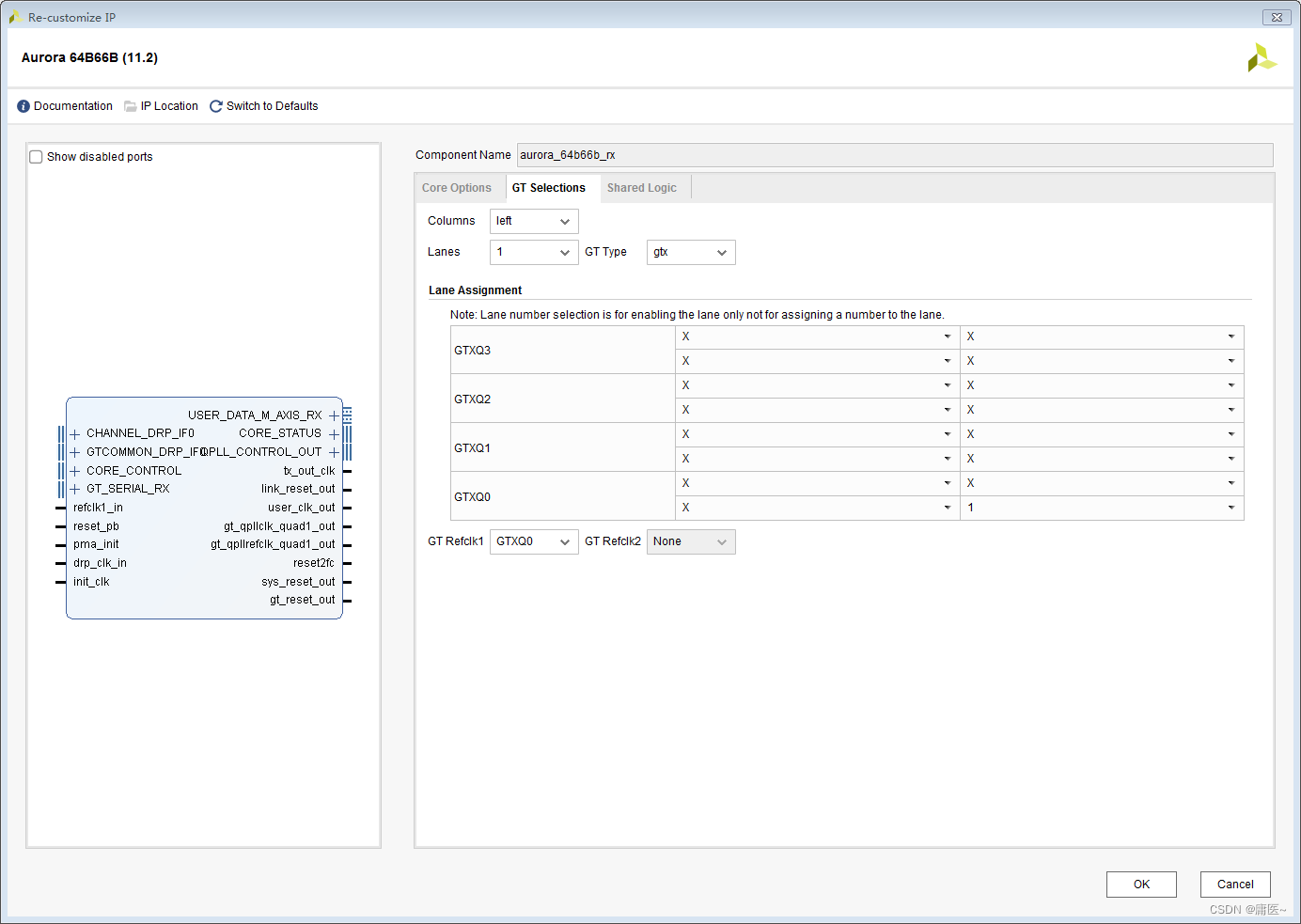

GT_selections 这里可以不用管,这里规定了用的哪一组收发器,只要在引脚约束的时候把管脚约束对就行。对于GT refclk,对于单链路传输,这里的选项只能选同一quad的时钟,但实际上可以选用临近quad的时钟,也就是临近bank上的时钟,只需要在进行引脚约束的时候把约束对就行。

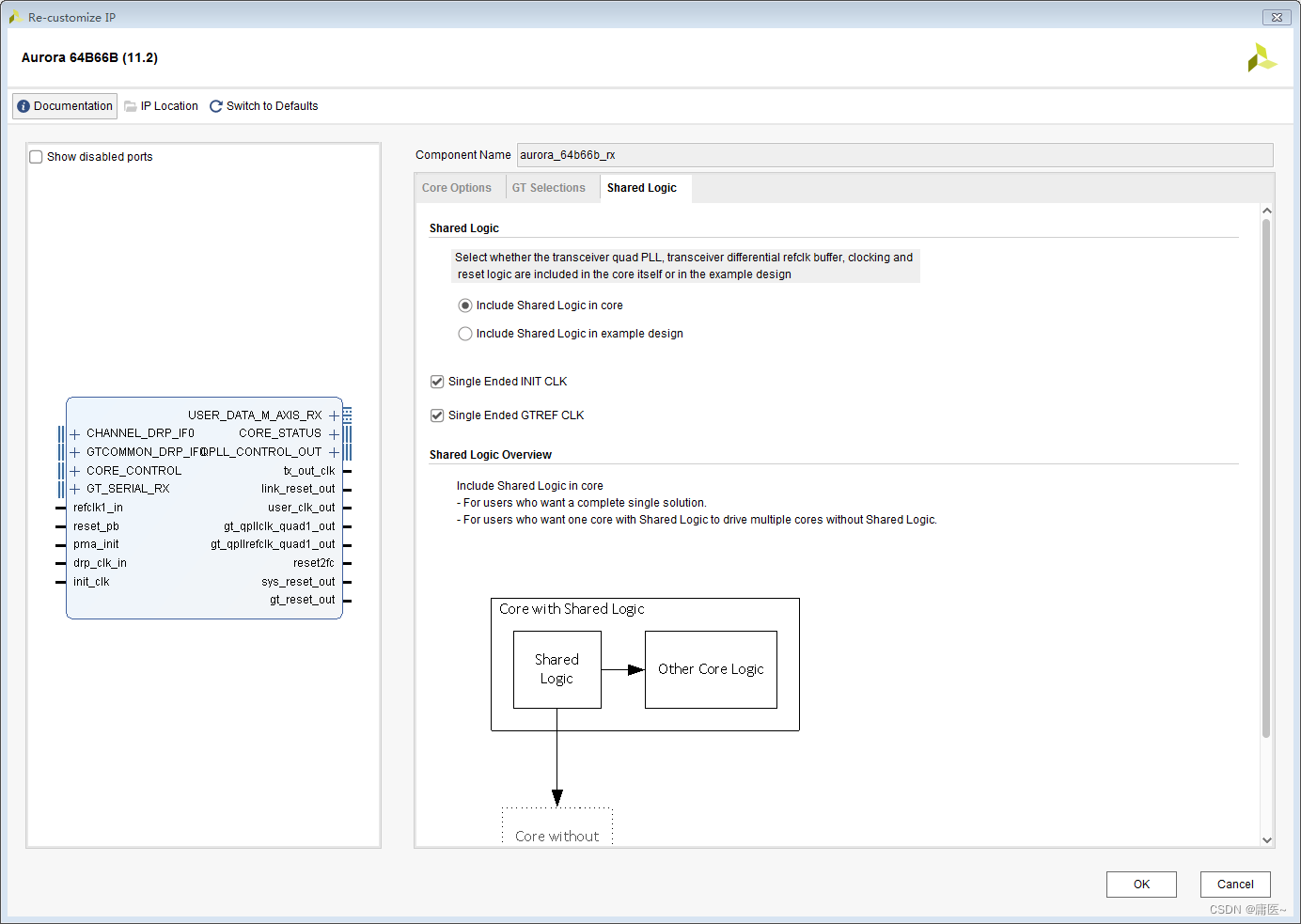

对于shared logic 这里选择的共享逻辑在核心中还是共享逻辑在示例程序中,当选择共享逻辑在核心中时,可以选择init clk和ref clk是单端时钟输入还是差分时钟输入。选择共享逻辑在核中,就不需要例化GTXE2_COMMON,GTXE2_COMMON在IP内部进行例化使用。选择共享逻辑在示例中这种通常是为了同时使用两组quad,一个IP核选用共享逻辑在核中,一个选择共享逻辑在示例中,选用IP在core的输出时钟提供给共享逻辑在示例程序中。

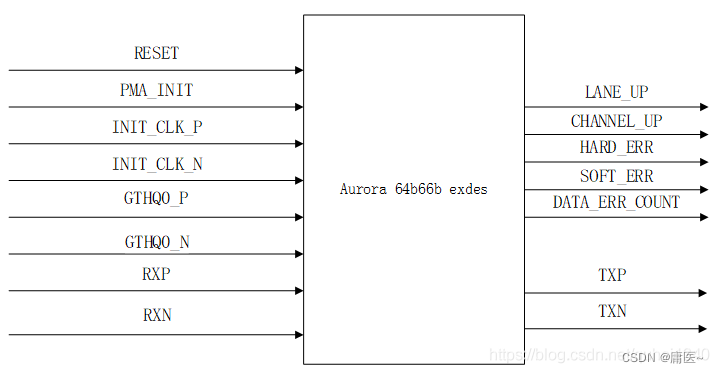

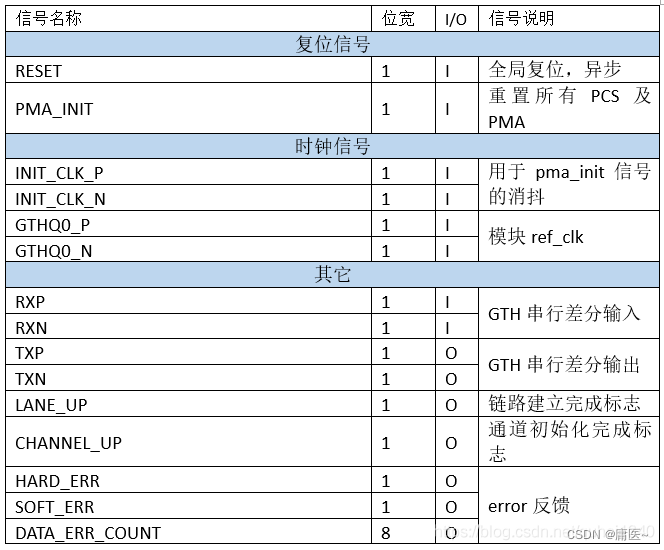

接口

用户接口

| Name | Direction | Clock Domain | Description |

| s_axi_tx_tdata | Input | user_clk | 传出数据(大小端由用户设定) |

| s_axi_tx_tready | Output | user_clk | 当接受来自源的信号时断言。当忽略来自源的信号时取消断言。 |

| s_axi_tx_tvalid | Input | user_clk | 当来自源的AXI4-Stream信号有效时断言。当应忽略来自源的AXI4-Stream控制信号和/或数据时取消断言。 |

| s_axi_tx_tlast | Input | user_clk | 帧的结束。 如果Streaming接口选项为chos,则此端口不可用 |

| s_axi_tx_tkeep | Input | user_clk | 指定最后一个数据节拍中的有效字节数(有效字节数= tkeep中的1数)。只有在断言s_axi_tx_tlast时才对S_axi_tx_tkeep进行采样。 核心支持连续对齐和连续未对齐的数据流,并期望数据从LSB连续填充到MSB。无效字节不能与有效的s_axi_tx_tdata总线交叉。 如果选择了流式接口选项,则此端口不可用。 |

| m_axi_rx_tdata | Output | user_clk | 来自信道伙伴的传入数据(升序位)。 |

| m_axi_rx_tvalid | Output | user_clk | 当来自core的数据有效时断言。当应该忽略来自核心的数据时取消断言。 |

| m_axi_rx_tlast | Output | user_clk | 表示进入帧的结束。 如果选择了流式接口选项,则此端口不可用。 |

| m_axi_rx_tkeep | Output | user_clk | 指定最后一个数据节拍中的有效字节数。 如果选择了流式接口选项,则此端口不可用 |

时钟接口

| Name | Direction | Clock Domain | Description |

| init_clk init_clk_p/init_clk_n | Input | init_clk信号用于注册和撤销pma_init信号。首选的init_clk范围是50 ~ 200 MHz。内核设置的默认init_clk频率对于7系列设计是50 MHz,对于UltraScale设备设计是line_rate/64。Init_clk频率是用户可配置的参数。使用Include Shared Logic in core选项,init_clk信号是不同的。单端INIT CLK选项提供单端init_clk输入。 | |

| init_clk_out | Output | init_clk | Init_clk输出。此端口对于单端INIT CLK选项不可用,因为UltraScale和UltraScale+设备没有差分init_clk输入。 |

| mmcm_not_locked | Input | user_clk | 如果使用混合模式时钟管理器(MMCM)为Aurora 64B/66B核心生成时钟,则mmcm_not_locked信号应该连接到串行收发器锁相环(PLL)锁定信号的反方向。与核心配套的时钟模块采用锁相环进行时钟划分。时钟模块的mmcm_not_locked信号应该连接到核心的mmcm_not_locked信号。在示例设计中包含共享逻辑时,mmcm_not_locked信号可用。 |

| mmcm_not_locked_out | Output | user_clk | |

| user_clk | Input | 由核心和用户共享的并行时钟应用程序。user_clk信号是一个BUFG 从tx_out_clk派生其输入的输出。的时钟生成器在<组件中可用名称>_clock_module文件。User_clk用作txusrclk2输入到收发器。看到相关收发机用户指南/数据表rate-related信息。User_clk可用当示例中包含共享逻辑时 设计。User_clk_out是当共享逻辑包含在核心中时可用的用户时钟输出。 | |

| user_clk_out | Output | user_clk | |

| tx_out_clk | Output | tx_out_clk | 由GTX、GTH或GTY收发器生成基于收发器锁相环的参考时钟频率设置。是否应该缓冲和使用为所连接的逻辑生成用户时钟深入到核心。 |

| sync_clk | Input | 串行收发器使用的并行时钟内部同步逻辑。规定为Txusrclk信号发送到收发器接口。的Sync_clk是user_clk的两倍。看到相关收发机用户指南/数据表rate-related信息。Sync_clk可用,当示例中包含共享逻辑时设计。Sync_clk_out是同步时钟输出。RX-only_Simplex模式下该端口不可用。 | |

| sync_clk_out | Output | sync_clk | |

| gt_refclk1_p/gt_refclk1_n gt_refclk2_p/gt_refclk2_n gt_refclk3_p/gt_refclk3_n gt_refclk4_p/gt_refclk4_n gt_refclk5_p/gt_refclk5_n refclk1_in refclk2_in refclk3_in refclk4_in refclk5_in | Input | Gt_refclk (CLKP / CLKN)是一个由振荡器产生并馈电的专用外部时钟 通过专用的IBUFDS。 •gt_refclk1_p/gt_refclk1_n =差分收发器参考时钟1 •gt_refclk2_p/gt_refclk2_n =差分收发器参考时钟2 •gt_refclk3_p/gt_refclk3_n =差分收发器参考时钟2 •gt_refclk4_p/gt_refclk4_n =差分收发器参考时钟2 •gt_refclk5_p/gt_refclk5_n =差分收发器参考时钟2 •refclk1_in =单端收发器参考时钟1 •refclk2_in =单端收发器参考时钟2 •gt_refclk1_out =单端收发器参考时钟1 •gt_refclk2_out =单端收发器参考时钟1 单端GT REFCLK选项不可用。 | |

| gt_refclk1_out gt_refclk2_out gt_refclk3_out gt_refclk4_out gt_refclk5_out | Output | ||

| gt_rxusrclk_out | Output | rxoutclk | 接收器从Aurora64b66b核心的主GT通道恢复时钟。只有在Aurora 64b66b核心定制期间启用了附加收发器控制和状态端口选项时,才启用此输出时钟端口。 |

| gt_qpllclk_quad_in, gt_qpllrefclk_quad_in | Input | Clock inputs generated by GTXE2_COMMON/GTHE2_COMMON/GTHE3_ COMMON/GTYE3_COMMON, GTHE4_COMMON, GTYE4_COMMON. | |

| gt_qpllclk_quad_out, gt_qpllrefclk_quad_out | Output | Clock outputs generated by GTXE2_COMMON/GTHE2_COMMON/ GTHE3_COMMON/GTHE4_COMMON/GTYE3_COMMON/GTYE4_COMMON. If the line rate is < 6.6 Gb/s in the GTX transceivers and < 8.0 Gb/s in 7 series. In UltraScale and UltraScale+ FPGA GTH and GTY transceivers, the gt_qpllclk_quad< quad_no >_out signal is tied High. |

IP核配置RTL视图