热门标签

热门文章

- 1关于转行产品经理的十大顾虑《上》_宋紫薇图

- 2Git切换分支(创建本地分支,远程分支,合并分支代码)_git切换branch

- 3六西格玛黑带考试试题|优思学院_在研究完改进措施后,决定进行试生产。试生产半月后,采集了100个数据。发现过程仍

- 4登录安全分析报告:创蓝云智注册

- 5Facebook术语表_加速投放缩略词

- 6Java Web应用开发课程大作业(电商品牌管理系统)_javaweb大作业

- 7中级工程师职称评定条件及申报资料,伴德诚

- 8应届生面试时如何破解没有工作经验的困局_应届毕业生面试,缺少经验该咋办

- 9克隆别人的项目并上传到自己的仓库_git克隆别人的项目上传到自己的仓库

- 10数据结构之——堆(Heap)_heap数据结构

当前位置: article > 正文

vivado Virtex-7 配置存储器器件_virtex7 ultrascale ddr3 ip使用手册

作者:你好赵伟 | 2024-05-30 08:10:27

赞

踩

virtex7 ultrascale ddr3 ip使用手册

Virtex-7

配置存储器器件

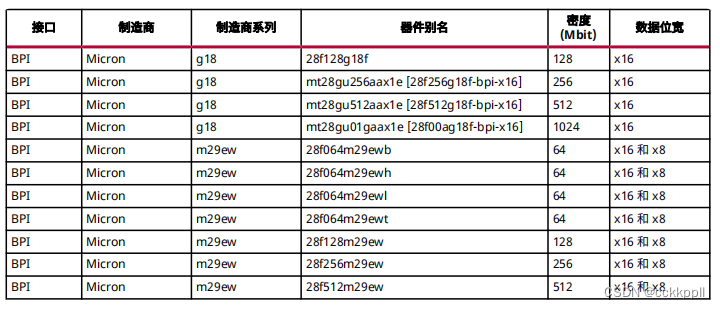

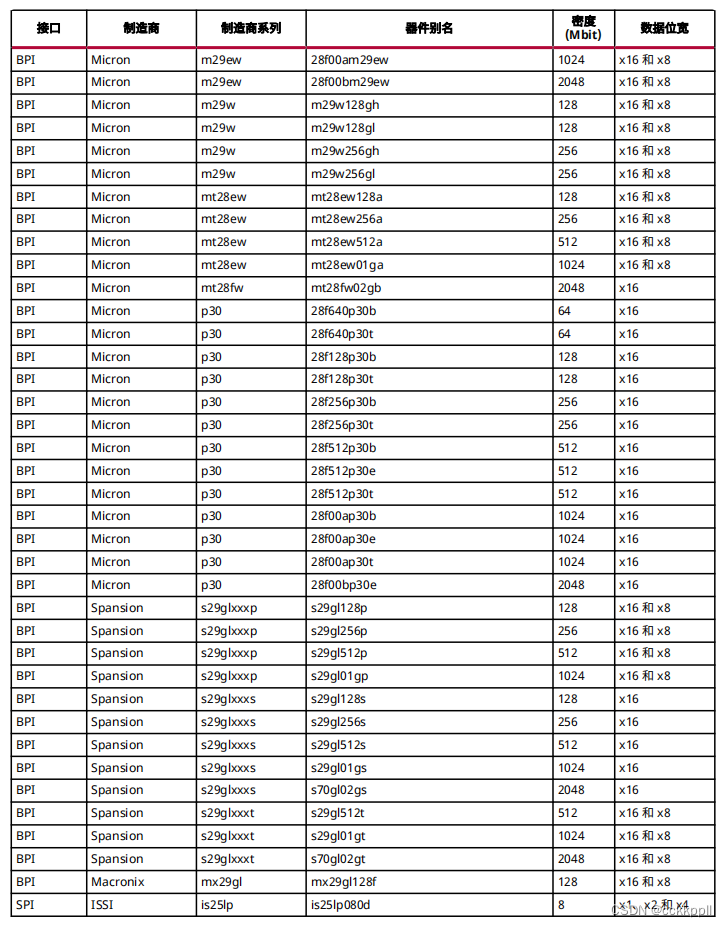

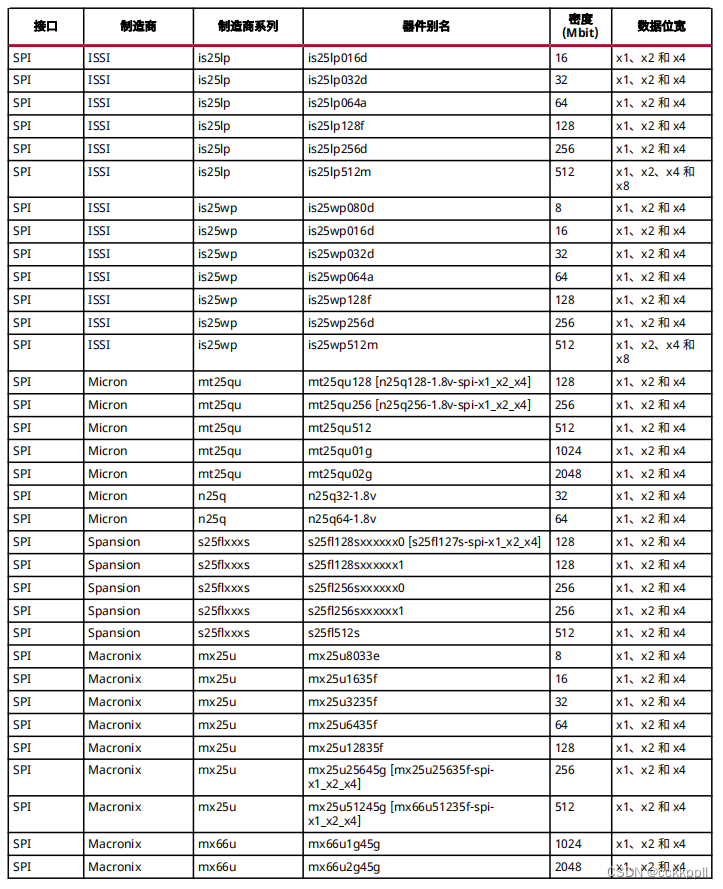

下表所示闪存器件支持通过

Vivado

®

软件对

Virtex

®

-7

器件执行擦除、空白检查、编程和验证等配置操作。

本附录中的表格所列赛灵思系列非易失性存储器将不断保持更新

,

并支持通过

Vivado

软件对其中所列非易失性存储器

进行擦除、空白检查、编程和验证。赛灵思竭尽所能保留此列表上的组件

,

即使这些组件不再适用于新设计也是如此

,

从而为可能包含这些组件的最终产品提供长期维护支持。

重要提示

!

鉴于商用非易失性存储器市场不断演变

,

赛灵思建议您与自己的非易失性存储器供应商联系

,

以确认

器件可用性和生命周期。下表中引用的特定器件并不能作为其当前或未来可用性的保证。

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/你好赵伟/article/detail/646031

推荐阅读

相关标签