热门标签

热门文章

- 1DataWhale打卡Day01--推荐系统入门_隐语义模型与矩阵分解 协同过滤算法的特点: 协同过滤算法的特点就是完全没有利用

- 2知识图谱——事件抽取

- 3Golang 学习笔记3:Go 并发与网络_go 接口并发

- 4从GitHub克隆项目到本地

- 5卷完了!分享下我的秋招面经(投递近50家自动驾驶与机器人公司)_杉川机器人结构创新工程师面试经验

- 62020B证(安全员)模拟考试系统及B证(安全员)考试试题_安全员b证历年真题试卷网盘

- 7Transformer的位置编码笔记(positional encoding)_transformer位置编码为啥用sin和cos

- 8git从tag拉分支_git 从tag拉分支

- 9IDEA JRebel最新版(2024.2.0)在线激活以及配置_idea插件jrebel 2024.2.0激活

- 10谷歌将正式推出 Fuchsia OS,已有适配设备_fuchsia os支持设备

当前位置: article > 正文

Verilog手撕代码(7)数据位宽转换_verilog位宽转换模块编写

作者:你好赵伟 | 2024-06-07 08:11:24

赞

踩

verilog位宽转换模块编写

数据位宽转换器

数据位宽转换器,一般常用于模块接口处,比如一个电路模块的输出数据位宽大于另一个模块的输入数据位宽,此时就需要进行数据位宽转换。比如SATA控制器中,内部数据位宽为32bit,但外部物理收发器PHY的接口通常为16bit,或者8bit,在不使用FIFO进行缓存的情况下,可以使用数据位宽转换器,通过时钟倍频在实现数据位宽的转换。

宽到窄

假设数据从模块A传入到模块B,模块A的输出数据为32位,模块B的输入数据位宽为16位,并把数据从A传入B而不损失数据。

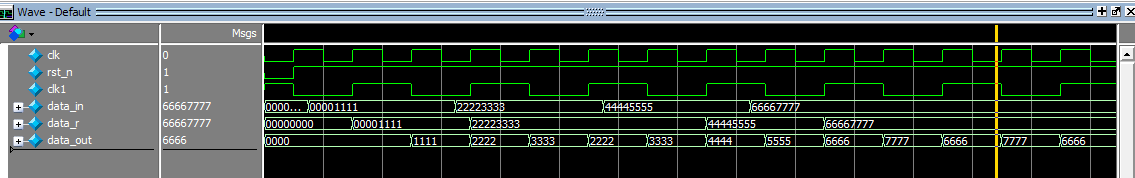

假设一个原时钟clk2x,通过二分频,把原时钟变为时钟clk1x,那么clk2x的时钟频率就是clk1x的两倍。在clk2x的上升沿,我们读入32bit数据,在clk2x的上升沿我们输出16bit数据,由于clk2x的频率是clk1x的两倍,每读入一次32bit数据,就会输出两次16bit数据,从而实现了数据位宽的转换,如图:

module width_32to16( input clk, input rst_n, input [31:0] data_in, output [15:0] data_out ); reg clk1; reg [31:0] data_r; always@(posedge clk or negedge rst_n)begin if(!rst_n) clk1 <= 1'b1; else clk1 <= ~clk1; end always@(posedge clk1 or negedge rst_n)begin if(!rst_n) data_r <= 31'd0; else data_r <= data_in; end assign data_out = clk1?data_r[31:16]:data_r[15:0]; endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

Testbench:

`timescale 1ns/1ns module width_32to16_tb(); reg clk; reg rst_n; reg [31:0]data_in; wire [15:0]data_out; width_32to16 inst( .clk(clk), .rst_n(rst_n), .data_in(data_in), .data_out(data_out) ); always #10 clk = ~clk; initial begin clk =0; rst_n = 0; data_in = 32'h0000_0000; #10 rst_n = 1; #5 data_in = 32'h0000_1111; #50 data_in = 32'h2222_3333; #50 data_in = 32'h4444_5555; #50 data_in = 32'h6666_7777; #200 $stop; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

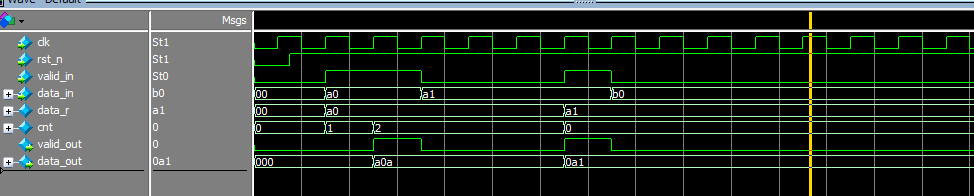

仿真结果:

窄到宽

8bit to 16bit

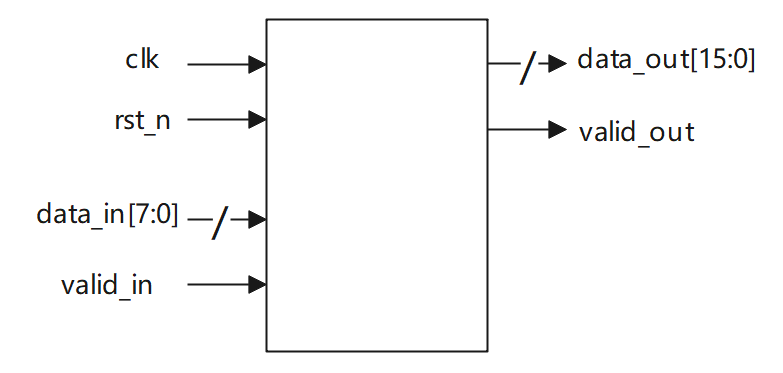

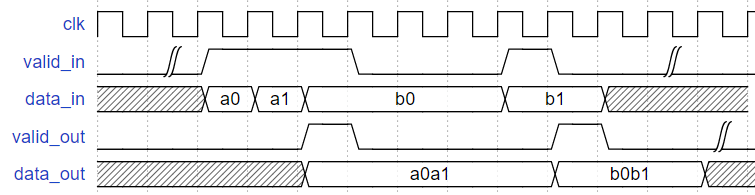

实现数据位宽转换电路,实现8bit数据输入转换为16bit数据输出。其中,先到的8bit数据应置于输出16bit的高8位。

电路的接口如下图所示。valid_in用来指示数据输入data_in的有效性,valid_out用来指示数据输出data_out的有效性;clk是时钟信号;rst_n是异步复位信号

代码:

module width_8to16( input clk, input rst_n, input valid_in, input [7:0]data_in, output reg valid_out, output reg [15:0]data_out ); reg [1:0]cnt; always@(posedge clk or negedge rst_n)begin if(!rst_n) cnt <= 2'b0; else if(valid_in) cnt <= (cnt == 1'd1)?1'd0:cnt + 1'b1; else cnt <= cnt; end reg [7:0]data_r; always@(posedge clk or negedge rst_n)begin if(!rst_n) data_r <= 8'd0; else data_r <= valid_in?data_in:data_r; end always@(posedge clk or negedge rst_n)begin if(!rst_n)begin data_out <= 16'd0; valid_out <= 1'b0; end else if(cnt == 1)begin data_out <= valid_in?{data_r,data_in}:data_out; valid_out <= valid_in; end else begin data_out <= data_out; valid_out <= 1'b0; end end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

Testbench:

module width_8to16_tb(); reg clk; reg rst_n; reg valid_in; reg [7:0]data_in; wire valid_out; wire [15:0]data_out; width_8to16 inst( .clk(clk), .rst_n(rst_n), .valid_in(valid_in), .data_in(data_in), .valid_out(valid_out), .data_out(data_out) ); always #10 clk = ~clk; initial begin clk = 0; rst_n = 0; valid_in = 0; data_in = 8'd0; #15 rst_n = 1; #5 valid_in = 1; #20 data_in = 8'h11; #20 data_in = 8'h22; #20 data_in = 8'h33; #20 valid_in = 0; #20 valid_in = 1; #20 data_in = 8'h44; #20 data_in = 8'h55; #200 $stop; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

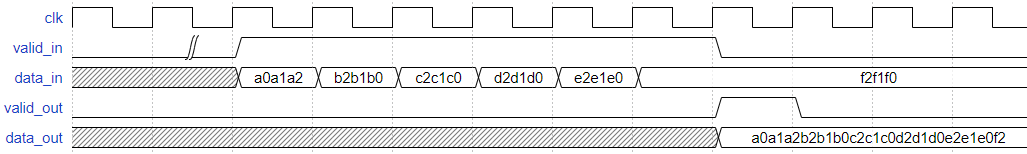

仿真结果:

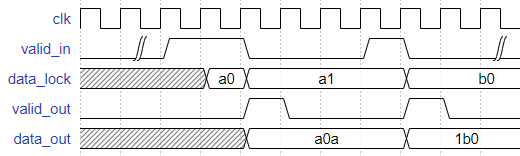

非整数倍转换

8bit to 12bit

代码:

module width_8to12( input clk , input rst_n , input valid_in , input [7:0] data_in , output reg valid_out, output reg [11:0] data_out ); reg [1:0]cnt; always@(posedge clk or negedge rst_n)begin if(!rst_n) cnt <= 0; else if(valid_in) cnt <= cnt == 2?0:cnt + 1; else cnt <= cnt; end reg [7:0]data_r; always@(posedge clk or negedge rst_n)begin if(!rst_n) data_r <= 0; else data_r <= valid_in?data_in:data_r; end always@(posedge clk or negedge rst_n)begin if(!rst_n) data_out <= 0; else if(cnt == 1) data_out <= valid_in?{data_r,data_in[7:4]}:data_out; else if(cnt == 2) data_out <= valid_in?{data_r[3:0],data_in}:data_out; else data_out <= data_out; end always@(posedge clk or negedge rst_n)begin if(!rst_n) valid_out <= 0; else valid_out <= (cnt == 1 || cnt == 2) && valid_in; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

Testbench:

module width_8to12_tb(); reg clk; reg rst_n; reg valid_in; reg [7:0] data_in; wire valid_out; wire [11:0] data_out; width_8to12 inst( .clk(clk), .rst_n(rst_n), .valid_in(valid_in), .data_in(data_in), .valid_out(valid_out), .data_out(data_out) ); always #10 clk = ~clk; initial begin clk = 0; rst_n = 0; data_in = 0; valid_in = 0; #15 rst_n = 1; #15 valid_in = 1; data_in = 8'ha0; #40 valid_in = 0; data_in = 8'ha1; #60 valid_in = 1; #20 valid_in = 0; data_in = 8'hb0; #200 $stop; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

仿真结果:

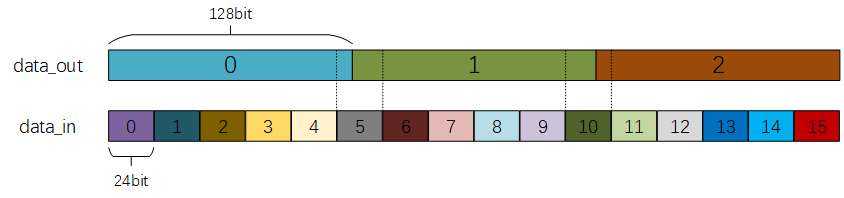

24bit to 128bit

代码:

module width_24to128( input clk, input rst_n, input valid_in, input [23:0] data_in, output reg valid_out, output reg [127:0] data_out ); reg [3:0]cnt; always@(posedge clk or negedge rst_n)begin if(!rst_n) cnt <= 4'd0; else if(valid_in) cnt <= (cnt == 4'd15)?0:cnt + 1'b1; end reg [127:0] data_r; always@(posedge clk or negedge rst_n)begin if(!rst_n) data_r <= 128'd0; else data_r <= valid_in?{data_r[103:0],data_in}:data_r; end always@(posedge clk or negedge rst_n)begin if(!rst_n) data_out <= 128'd0; else if(cnt == 4'd5) data_out <= valid_in?{data_r[119:0],data_in[23:16]}:data_out; else if(cnt == 4'd10) data_out <= valid_in?{data_r[111:0],data_in[23:8]}:data_out; else if(cnt == 4'd15) data_out <= valid_in?{data_r[103:0],data_in[23:0]}:data_out; else data_out <= data_out; end always@(posedge clk or negedge rst_n)begin if(!rst_n) valid_out <= 1'd0; else valid_out <= (cnt == 4'd5 || cnt == 4'd10 || cnt == 4'd15) && valid_in; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

Testbench:

module width_24to128_tb(); reg clk; reg rst_n; reg valid_in; reg [23:0] data_in; wire valid_out; wire [127:0] data_out; width_24to128 inst( .clk(clk), .rst_n(rst_n), .valid_in(valid_in), .data_in(data_in), .valid_out(valid_out), .data_out(data_out) ); always #10 clk = ~clk; initial begin clk = 0; rst_n = 0; valid_in = 0; data_in = 0; #15 rst_n = 1; #15 valid_in = 1; data_in = 24'ha0a1a2; #20; data_in = 24'hb2b1b0; #20; data_in = 24'hc2c1c0; #20; data_in = 24'hd2d1d0; #20; data_in = 24'he2e1e0; #20; data_in = 24'hf2f1f0; #20 valid_in = 0; #200 $stop; end endmodule

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

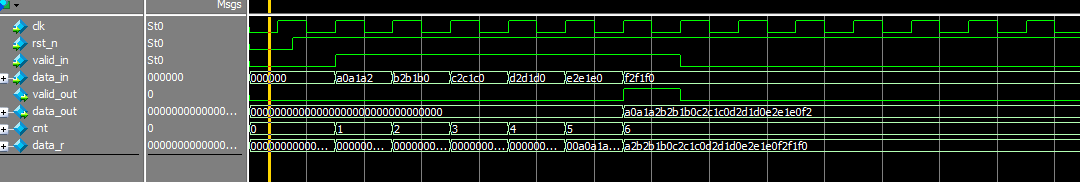

仿真结果:

声明:本文内容由网友自发贡献,不代表【wpsshop博客】立场,版权归原作者所有,本站不承担相应法律责任。如您发现有侵权的内容,请联系我们。转载请注明出处:https://www.wpsshop.cn/w/你好赵伟/article/detail/684600

推荐阅读

相关标签