- 1curl 命令_curl命令

- 2这个用PHP开发的全开源商城系统可免费商用_支付开源项目代码

- 3Unity开发OpenXR |(三)使用 OpenXR 添加一个运动系统,实现传送、抓取功能 的简单VR示例场景 的全过程详细教程_unity开发openxr |(三)使用 openxr 添加一个运动系统,实现传送、抓取功能 的简单

- 4Selenium知识点_selenium page_source

- 5[从源码学设计]蚂蚁金服SOFARegistry 之 ChangeNotifier_sofaregistry 源码

- 6layui数据表格接收json数据规范——一件有意思的json数据“键-值”封装问题_c#将数据符合 layui 数据表格规范的 json 格式数据

- 7GPT-3是什么?OpenAI GPT-3大白话指南:对未来的影响 -Fahri Karakas_gpt-3 参数 是什么含义

- 8vs文件乱码:文件加载,使用Unicode(UTF-8)编码加载文件xxx时,有些字节已用Unicode替换字符替换。保存该文件将不会保留原始文件内容。解决方案_文件加载 使 用unicode (utf-8) 编码加载文件时,有些字节已用 unicode 替换字

- 9机器学习笔记(9)——随机森林算法(RandomForest,RF)_随机森林特征向量

- 10element v-for循环列表的表单校验(动态绑定的数据)_el-row v-for

S32K144中CAN位时序计算/CANFD波形分析_canfd波形不稳

赞

踩

1 CAN位时序计算

使用S32K144已经很久了,每次使用到CAN模块时总是忘记波特率、位时序怎么配置的,这里总结、记录一下。

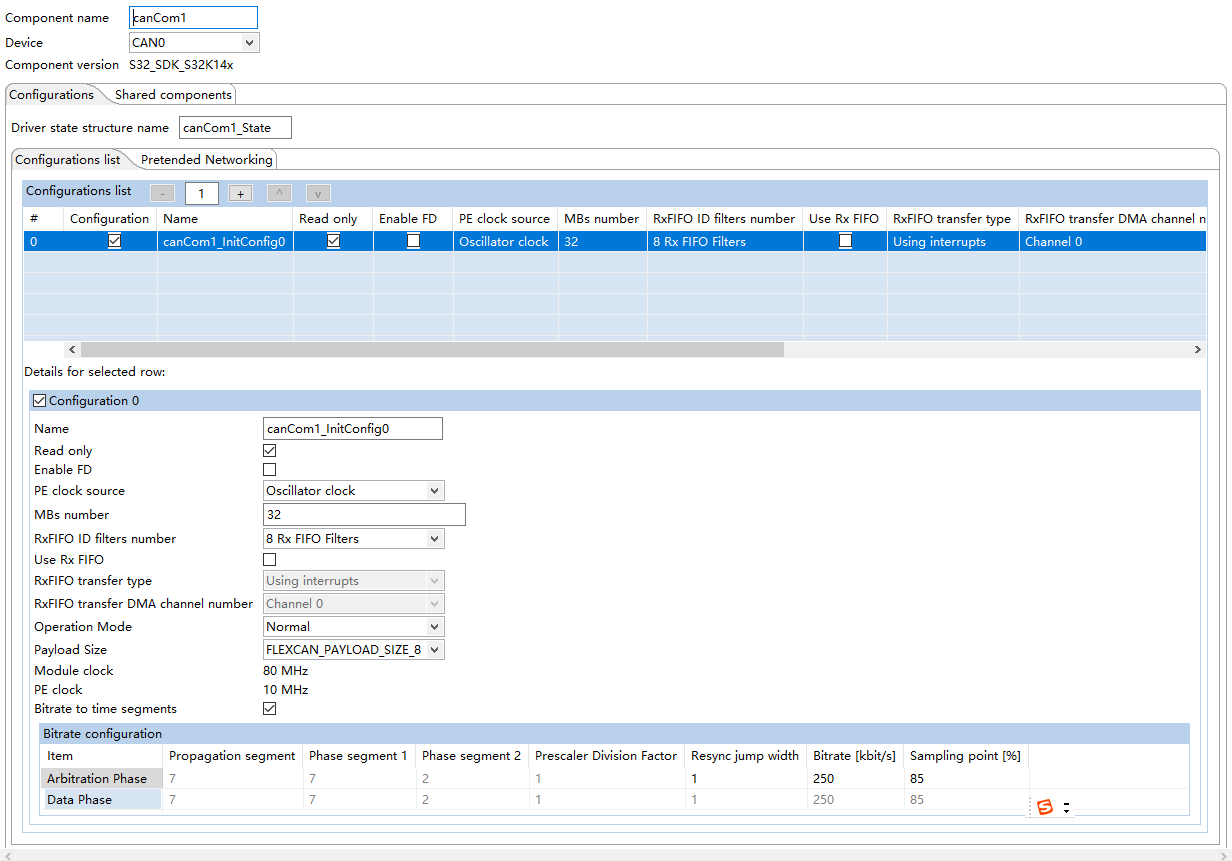

上图是PE中CAN0的配置记录。

1.1 位时序

从上图中可以看到,

Propagation segment = 7,

Phase segment1 = 7,

Phase segment2 = 2,

Prescaler Division Factor = 1,

Resync jump width = 2,

即传播时间段为7tq,相位缓冲段1为7tq,传播缓冲段2为2tq,预分频系数为1tq,重同步补偿宽度为2tq,同步段默认为1tq,那么一个bit由1+(7+1)+(7+1)+(2+1)=20tq构成。

1.2 波特率

从上图可以看到PE clock为10MHz,

波特率= CAN时钟/(总tq数)/(预分频系数+1) = 10M/(20tq)/(1+1) = 250k。

2 CANFD波形分析

调试CAN程序特别是CAN收发驱动时,总是避免不了通过用示波器观察报文波形的方式确认MCU收发报文的正确性,因为CAN报文的波特率是固定的,报文的位时间也是固定的,500k的波特率对应2us的位时间;但是CANFD报文的波特率不是固定的,在某些场速率是500k,而在其他场速率则是2m,因此位时间不是固定的,这确实带来了一个实际问题,CANFD波形中总是会有一个bit,对应的位置大概是BRS位,但是它的时间既不是标准的2us,也不是标准的0.5us,一直没弄明白这个bit的产生原因是什么。

以前开发时这一块总是有点疑问,正好前段时间小组在做硬件测试,需要测试CANFD中BRS位在CANH/CANL上的电平上升/下降斜率,那首先需要找到TXD上BRS的位置,在这里记录一下分析CANFD波形的过程,顺便总结一下CANFD的特点,着重写一下速率转换处的位时间计算。

2.1 CANFD帧结构分析

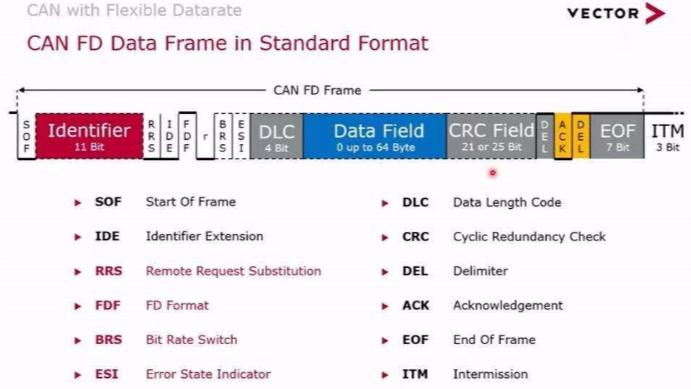

CANFD帧结构与CAN帧结构类似,只不过多了三个位,分别是FDF、BRS、ESI,见下图。

整个帧分为了7部分,分别是:

起始域:SOF;

仲裁域:ID+RRS+IDE+FDF+r;

控制域:BRS+ESI+DLC;

数据域:DATA Field;

校验域:CRC Field+DEL;

应答域:ACK+DEL;

结束域:EOF;

CANFD指的是可变速率的CAN,即在CAN总线上进行数据传输时7个域的传输速率不同,以500k/2m为例:起始域+仲裁域+应答域+结束域的速率为500k,而控制域+数据域+CRC域的速率为2m。

2.2 CANFD波形分析

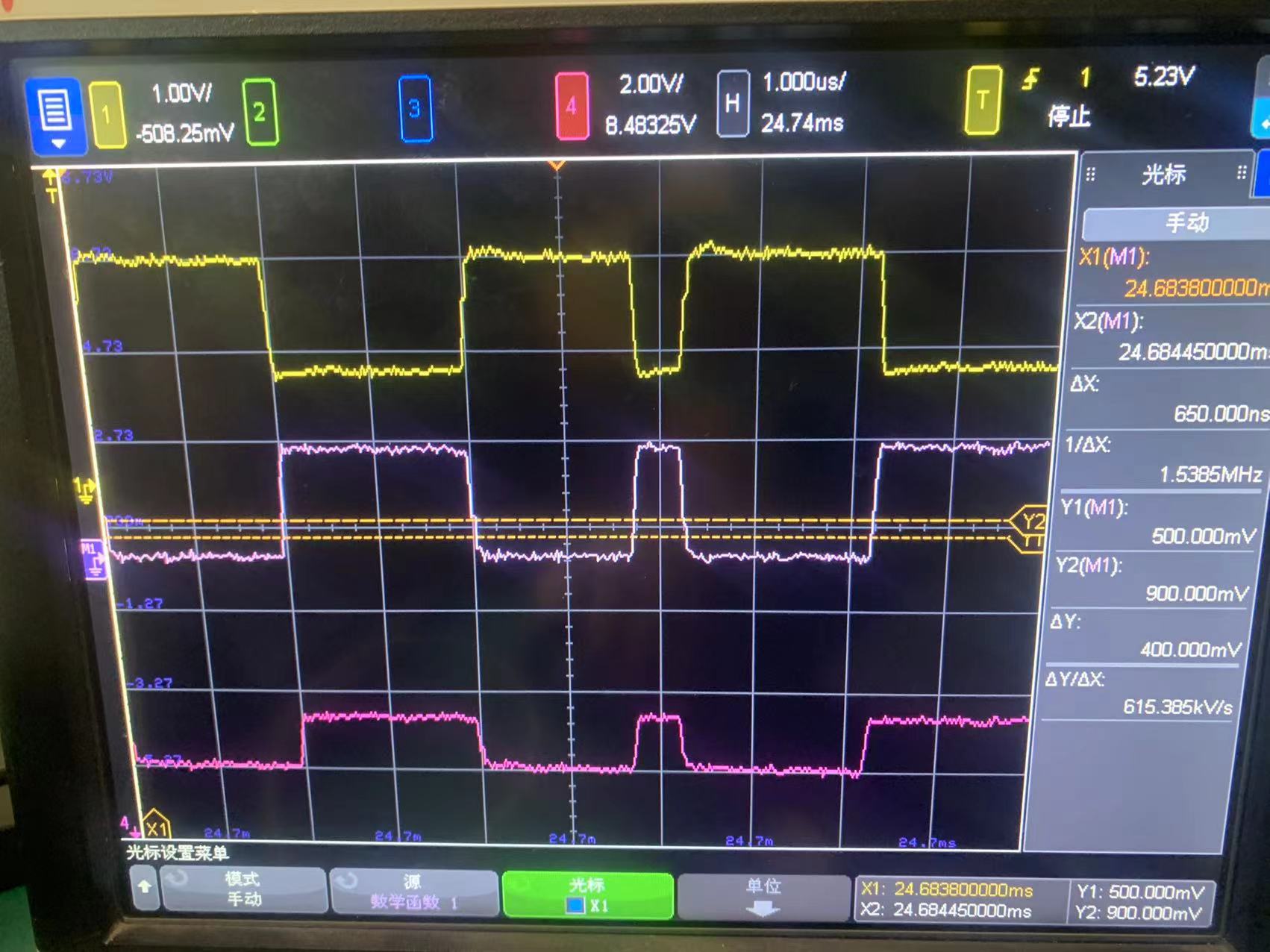

搞清楚CANFD帧结构之后,就可以分析CANFD波形了,见下图。

上面黄色波形是CANL波形,下面紫色波形是CANH波形,中间淡紫色波形是作差得到的波形,请注意:中间的波形并不是TXD的波形,因为差分电平里的高电平对应CAN总线里逻辑0(显性电平),低电平对应逻辑1(隐形电平)。

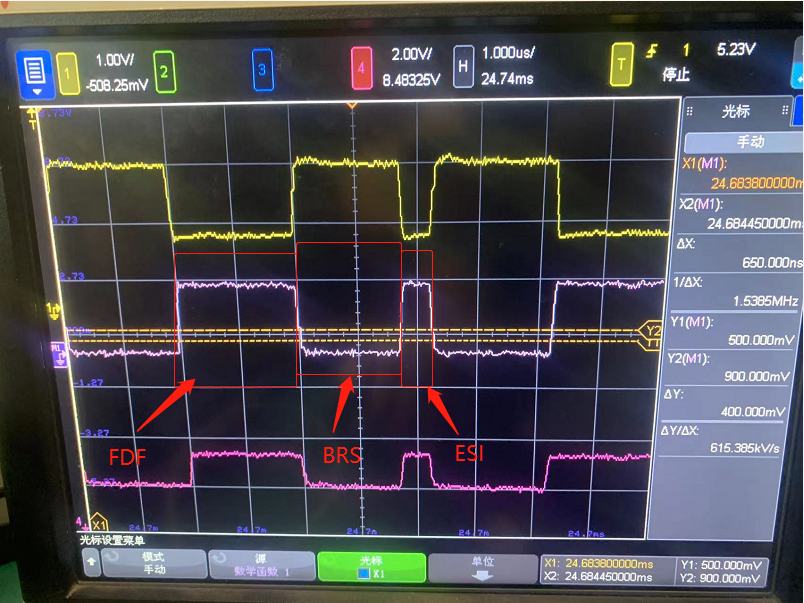

我将上图中的FDF、BRS、ESI位标注出来了,可以看到FDF的位时间是2us,ESI的位时间是0.5us,而BRS的时间既不是2us,也不是0.5us,经过查阅资料,得知BRS的位时间有自己的计算方式。

CANFD总线配置时,高波特率为2m,采样点为80%,低波特率为500k,采样点为81.25%。

BRS为可变速率值低速率向高速率切换,等于低波特率位宽度中采样点之前的段加上高波特率位宽度中采样点之后的段。因此BRS的位宽计算公式为:

BRS位宽 =(2us × 81.25%) + (0.5us × 20%)= 1.735us。

1.735us与上图中BRS的持续时间也比较贴近,因此可以确认BRS位就是上图中的中间位。

同理,高波特率向低波特率切换发生在CRC DEL位,CRC DEL的位时间为高波特率位宽度采样点之前的段加上低波特率位宽度采样点之后的段。因此,CRC DEL的位宽计算公式为:

CRC DEL位宽 = (2us × 18.75%) + (0.5us × 80%)= 775us。

至此,后续在分析CANFD波形时就知道BRS位在哪里了。